High-speed coding chip

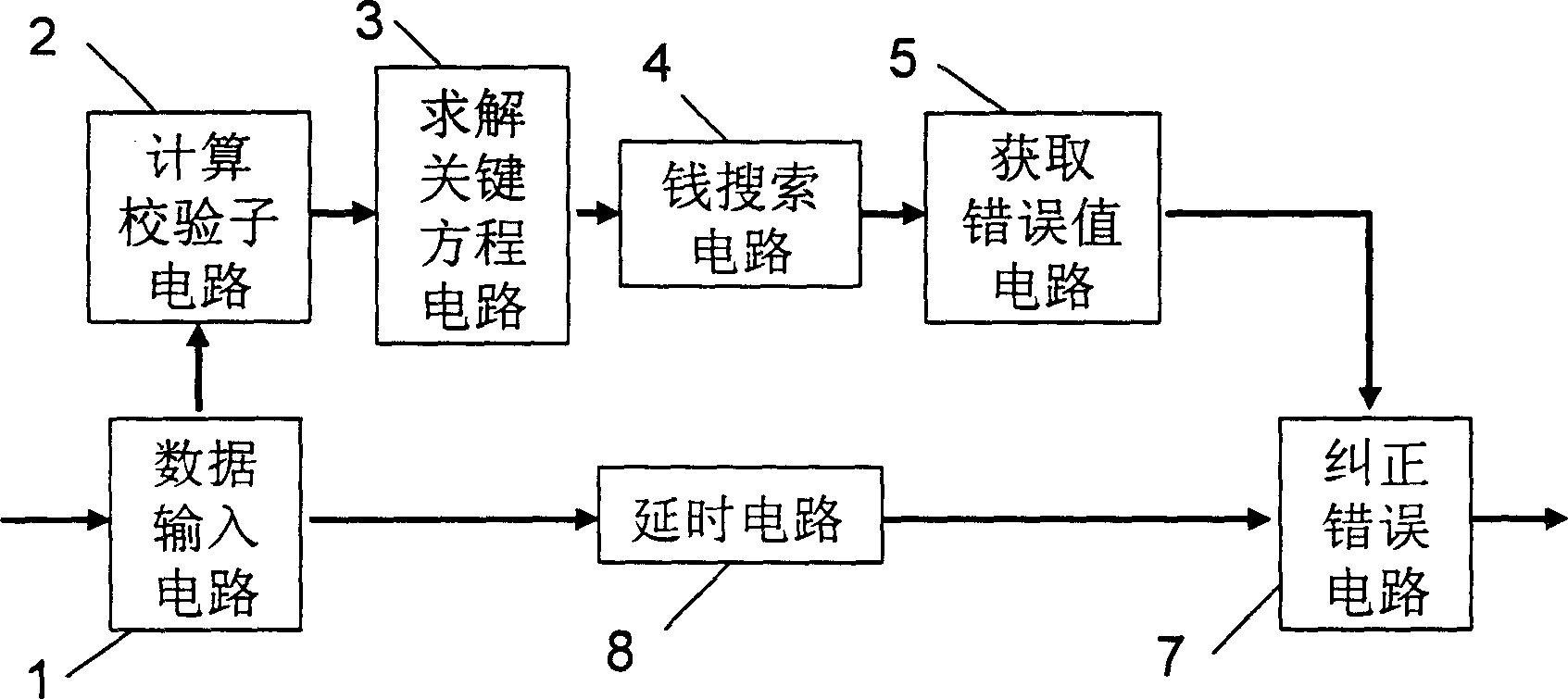

A decoding chip, high-speed technology, applied in the field of decoding chips, can solve the problems of complex decoding methods, difficult to achieve decoding speed, high engineering cost, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

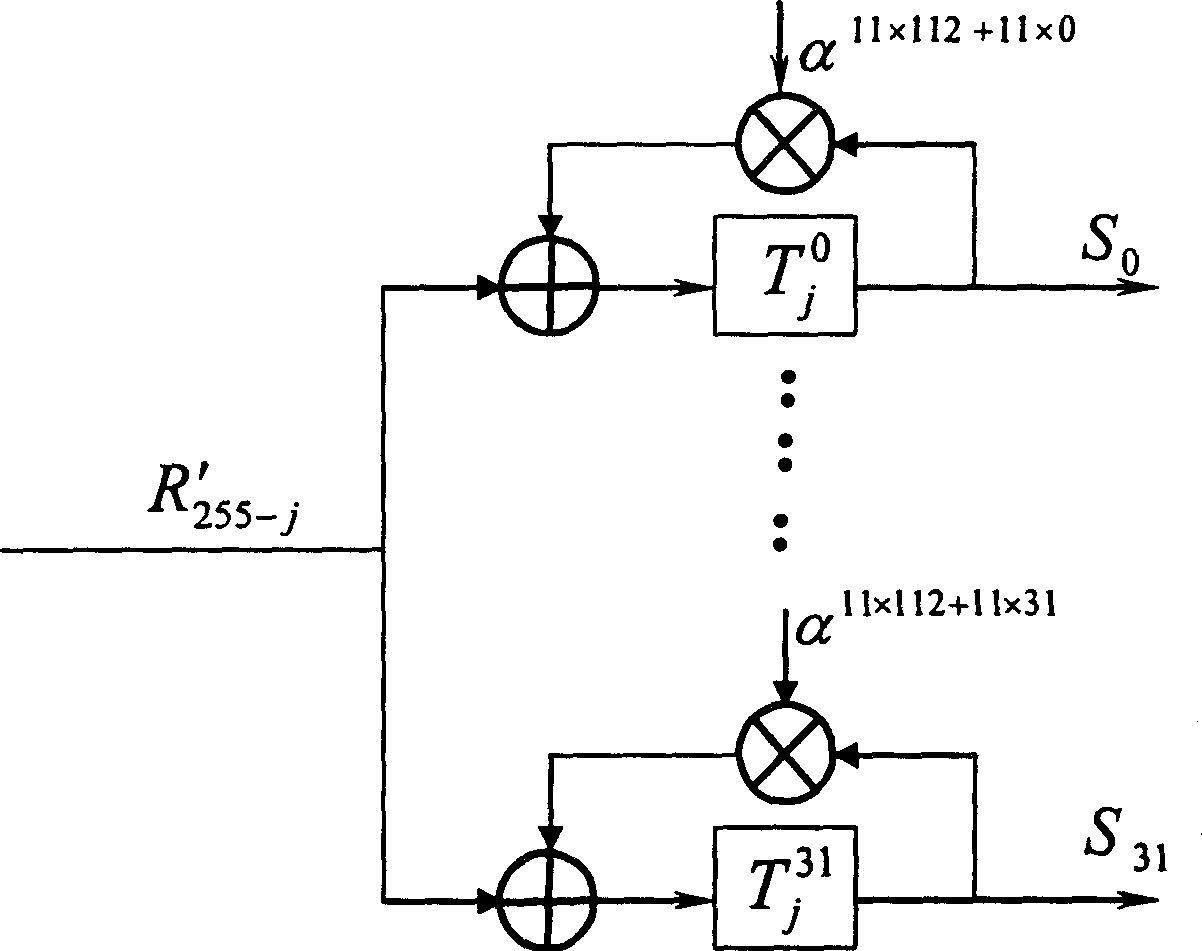

[0080] The various parameters that embodiment adopts are as follows:

[0081] m=8, representing the number of bits required for a code symbol of an RS code;

[0082] E=16, the code block that represents an RS code can correct the number of error code symbols;

[0083] Among them, m and E are mutually independent parameters.

[0084] N=2 m -1=255, representing the number of code symbols of the code block of each RS code;

[0085] 2E=32, representing the number of code symbols of the parity bit in the code block of each RS code;

[0086] k=n-2E=223, representing the number of code symbols of the information bits in the code block of each RS code;

[0087] F(X)=X 8 +X 7 +X 2 +X+1, indicating that the code symbol of the RS code is in GF(2 8 ) The domain generator polynomial defined in );

[0088] g ( x ) = Π j = 112 ...

Embodiment 2

[0197] Such as Figure 8 As shown, on the basis of Embodiment 1, a de-interleaving circuit 6 connected to the data input circuit 1 is also included for correcting burst errors. The RS code data is first input to the de-interleaving circuit 6 for de-interleaving, and then the processed data is input to the data input circuit 1, and then the decoding process as described in the first embodiment is performed.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More