Implementation method of high-speed reed-solomon (RS) codec based on field programmable gate array (FPGA)

An implementation method and codec technology are applied in the field of FPGA-based high-speed RS codec implementation, and can solve the problems of difficulty in achieving decoding speed, complex implementation, and high engineering implementation cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0096] In order to make the technical means, creative features and objectives of the present invention easy to understand, the present invention is further described below in conjunction with specific embodiments.

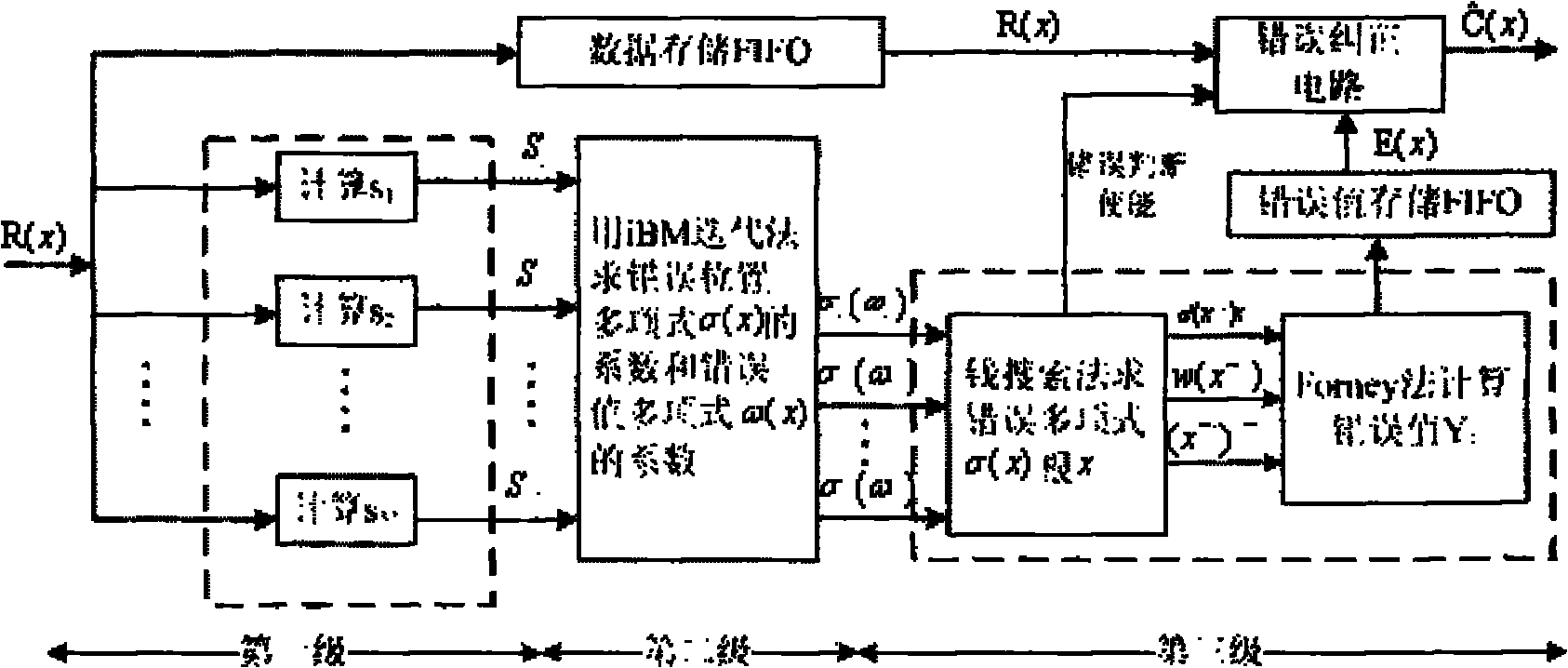

[0097] A kind of FPGA-based high-speed RS codec realization method of the present invention comprises the FPGA realization of high-speed RS (244,212) encoder and the FPGA realization of high-speed RS (244,212) decoder, adopts reverse clock to accomplish.

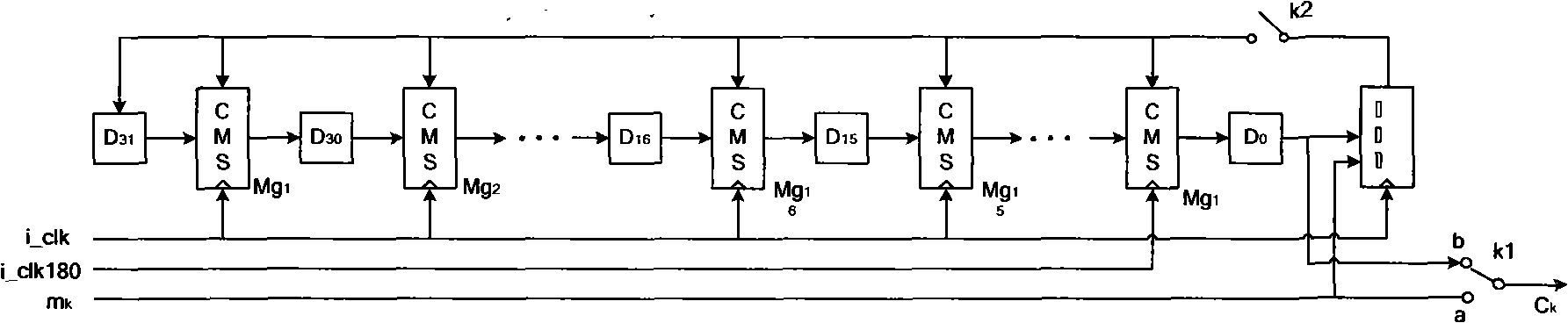

[0098] The FPGA method to realize the high-speed RS (244, 212) encoder is as follows:

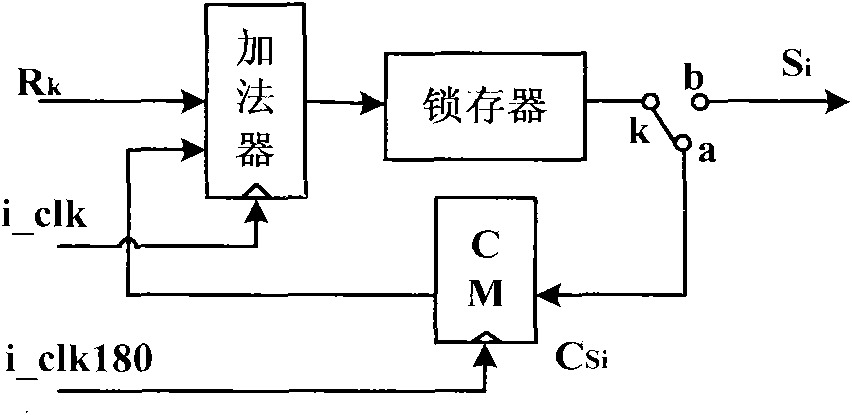

[0099] Described high-speed RS (244, 212) coder adopts dual-clock driving mode work, for each group of 212 information symbol {m 1 , m 2 , L, m 212} encoding to get 32 check code elements {p 1 ,p 2 , L, p 32}, without increasing the complexity of the hardware, the clock utilization rate is improved, thereby improving the encoding speed, and the resource consumption is low, such as figure 1 , the specific implementatio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More