Semiconductor packing process

A packaging process and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid device manufacturing, semiconductor/solid device components, etc., can solve problems such as limited, product scrapping, inconvenience, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] In order to further explain the technical means and effects that the present invention takes to achieve the intended purpose of the invention, the specific implementation methods, methods, steps, features and features of the semiconductor packaging process proposed according to the present invention will be described below in conjunction with the accompanying drawings and preferred embodiments. Efficacy, detailed as follows.

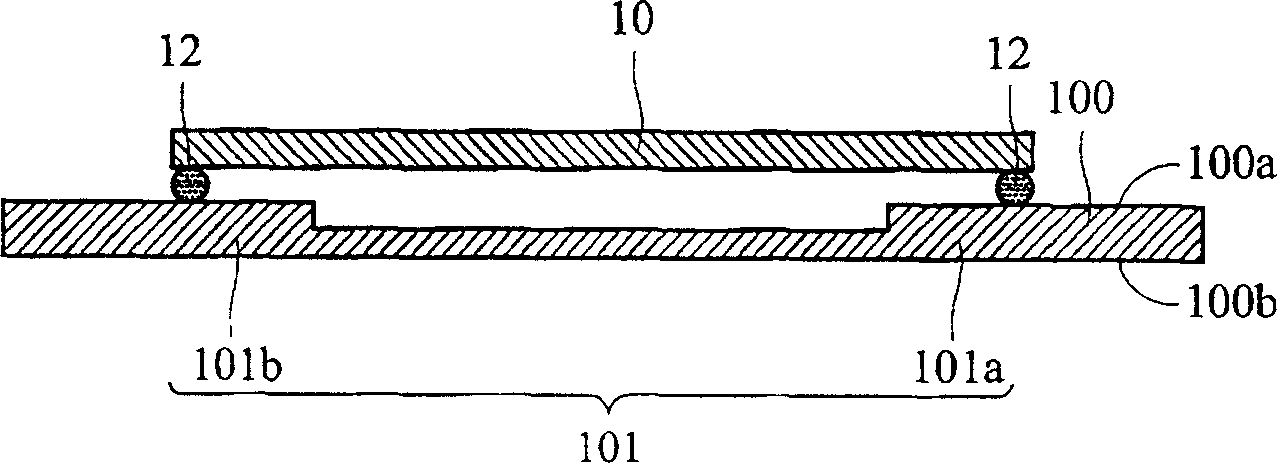

[0048] Figures 1A-1H Shown are a series of cross-sectional views showing the semiconductor packaging manufacturing process of the first embodiment of the present invention.

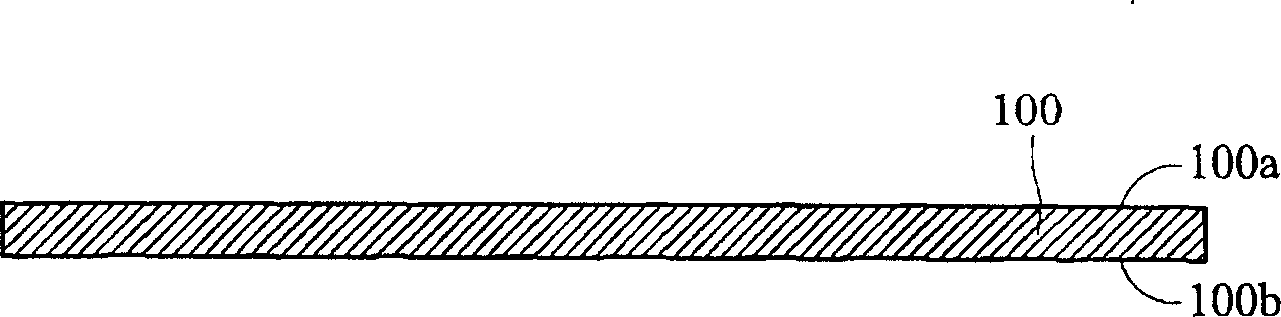

[0049] First, see Figure 1A As shown, a conductive substrate 100, preferably copper or aluminum, is provided. The conductive substrate 100 has opposite first surface 100a and second surface 100b.

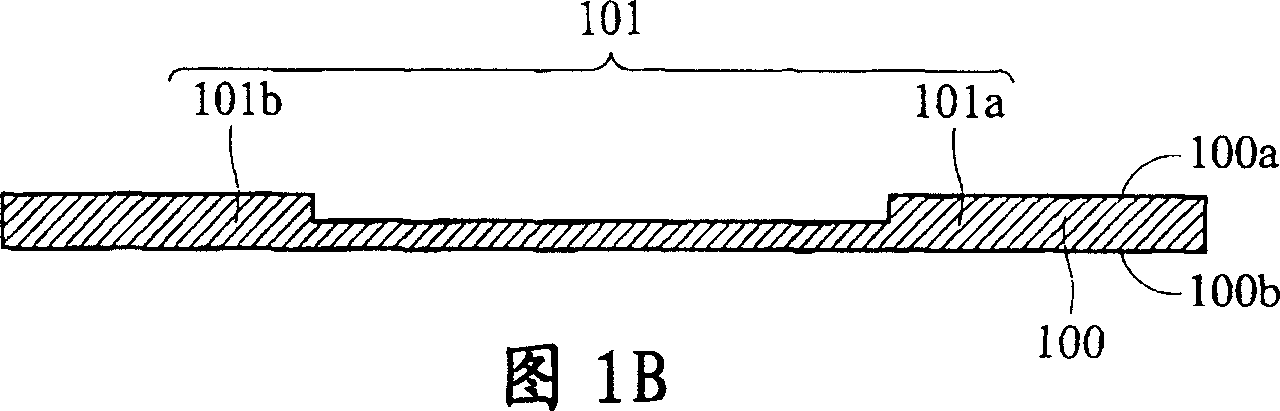

[0050] Next, as shown in FIG. 1B , a portion of the conductive substrate 100 is etched away from the first surface 100 a, but the conductive substrate 100 is not hollowed out, so...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap