Method and circuit for processing chip reset

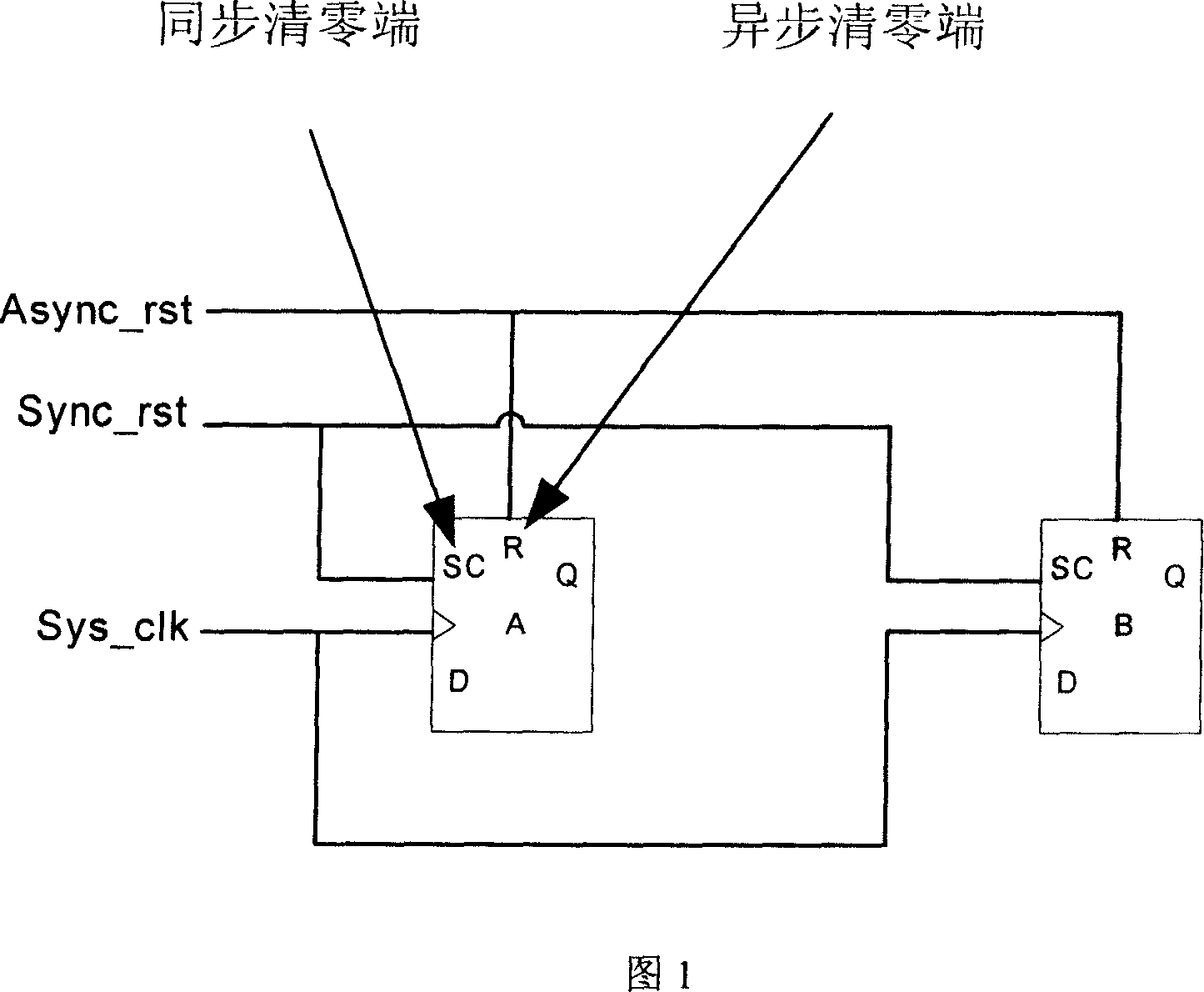

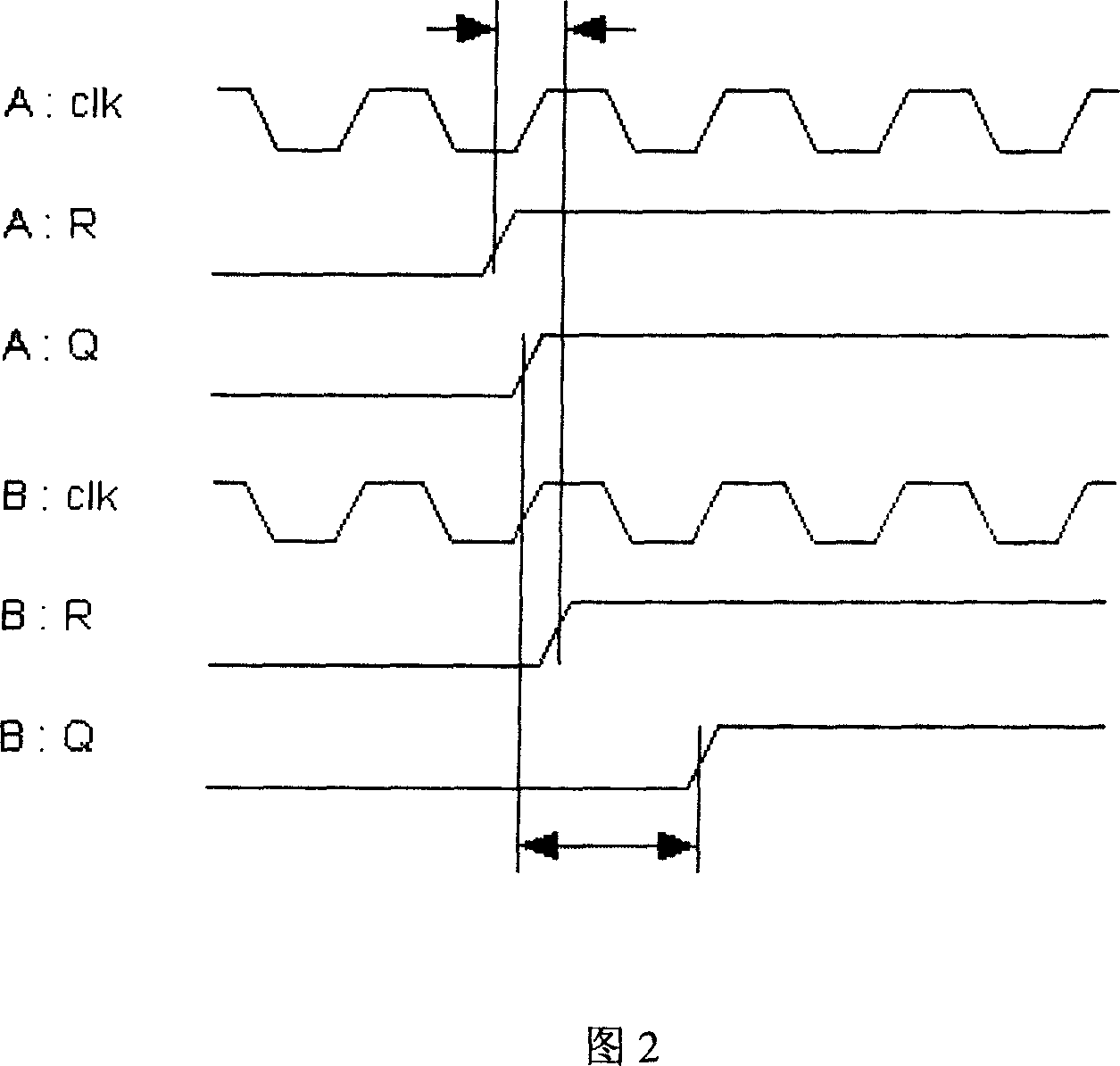

A technology for processing chips and circuits, which is applied in the field of processing chip resets. It can solve the problems of reset signal position deviation, uncertain initial state of registers, increased circuit design complexity, power consumption, and chip area, so as to ensure stability and simplify wiring. , the effect of small area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The method and circuit for chip reset of the present invention will be described in detail below with reference to the drawings and embodiments.

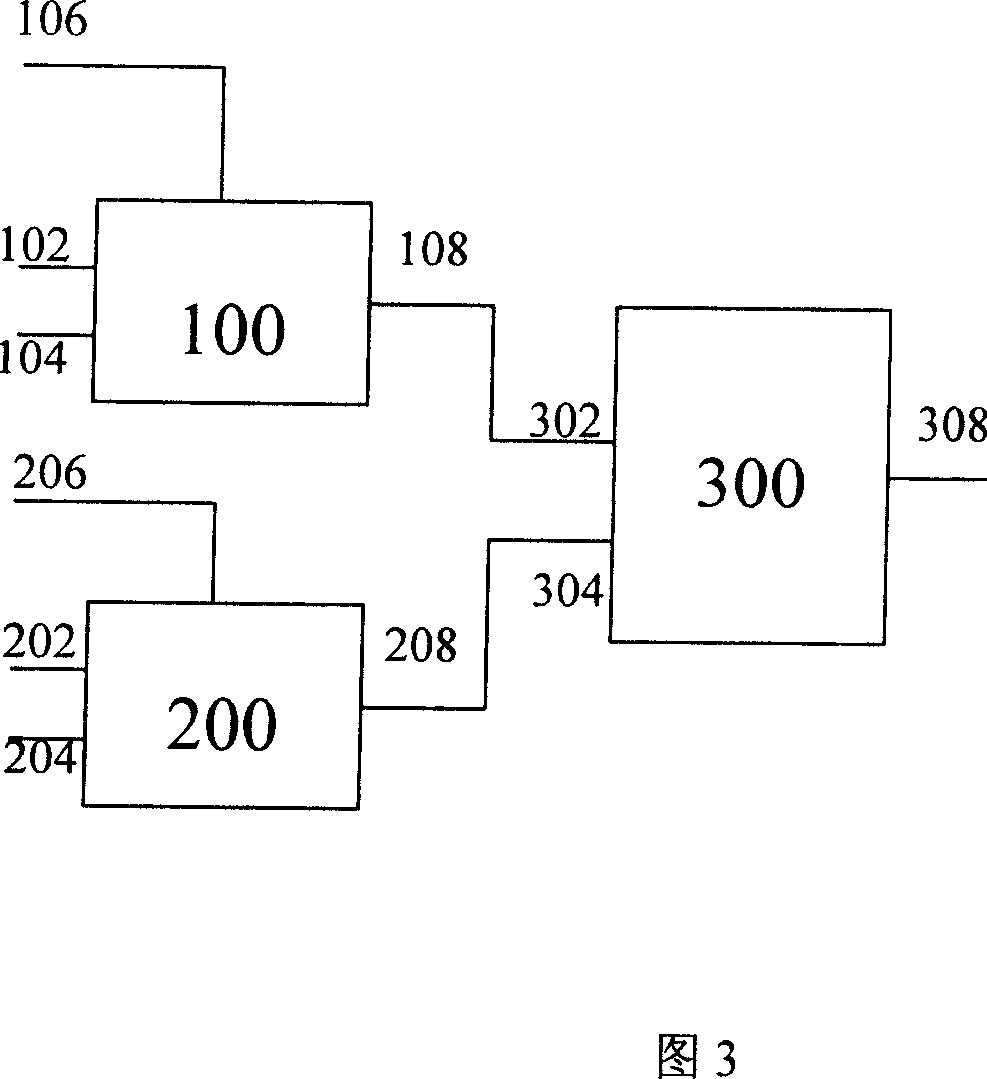

[0038] As shown in Figure 3 is a block diagram of the reset circuit of the present invention, as shown in the figure, the circuit includes: a first trigger unit 100 for triggering an asynchronous reset signal, including a clock port 102, a digital input port 104, an asynchronous reset port 106 and output port 108; The second trigger unit 200 for triggering a synchronous reset signal includes clock port 202, digital input port 204, asynchronous reset port 206 and output port 208; a combinational logic unit 300 includes several input ports 302, 304 and an output port 306; wherein: the output port 108 of the first trigger unit 100 is connected to the asynchronous reset port 206 of the second trigger unit 200, and the output port 108 of the first trigger unit 100 The output port 208 of the second trigger unit 200 is connected wit...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap