Hierarchical parallel pipelined operation of analog and digital circuits

a pipelined operation and analog and digital circuit technology, applied in the field of high-throughput discrete-time systems with parallel pipelined architectures, can solve the problems of front-end bandwidth not being scaled down to match the slow clock, backend limiting system clock frequency,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Reference will now be made in detail to embodiments of the present invention, examples of which are illustrated in the accompanying drawings.

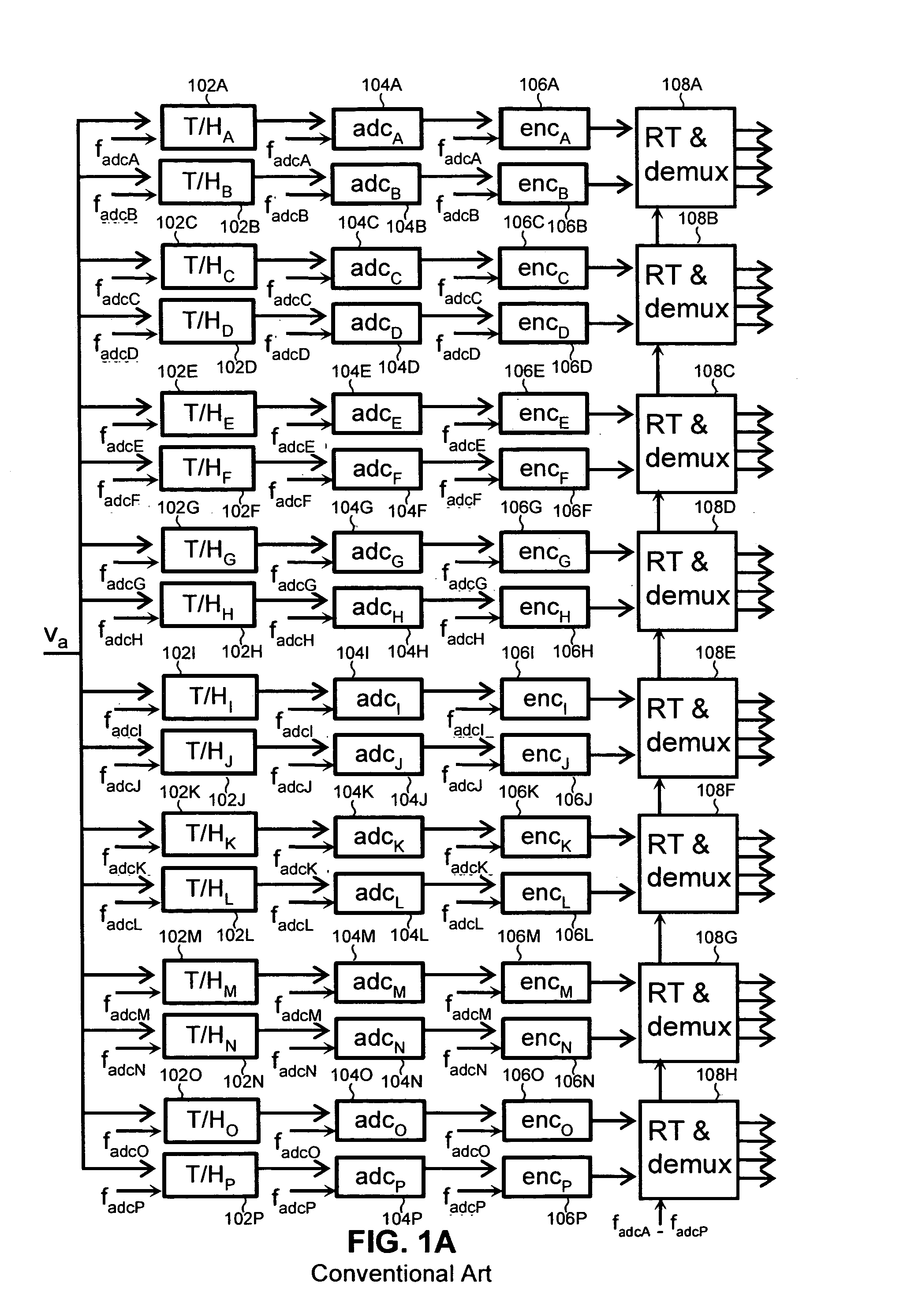

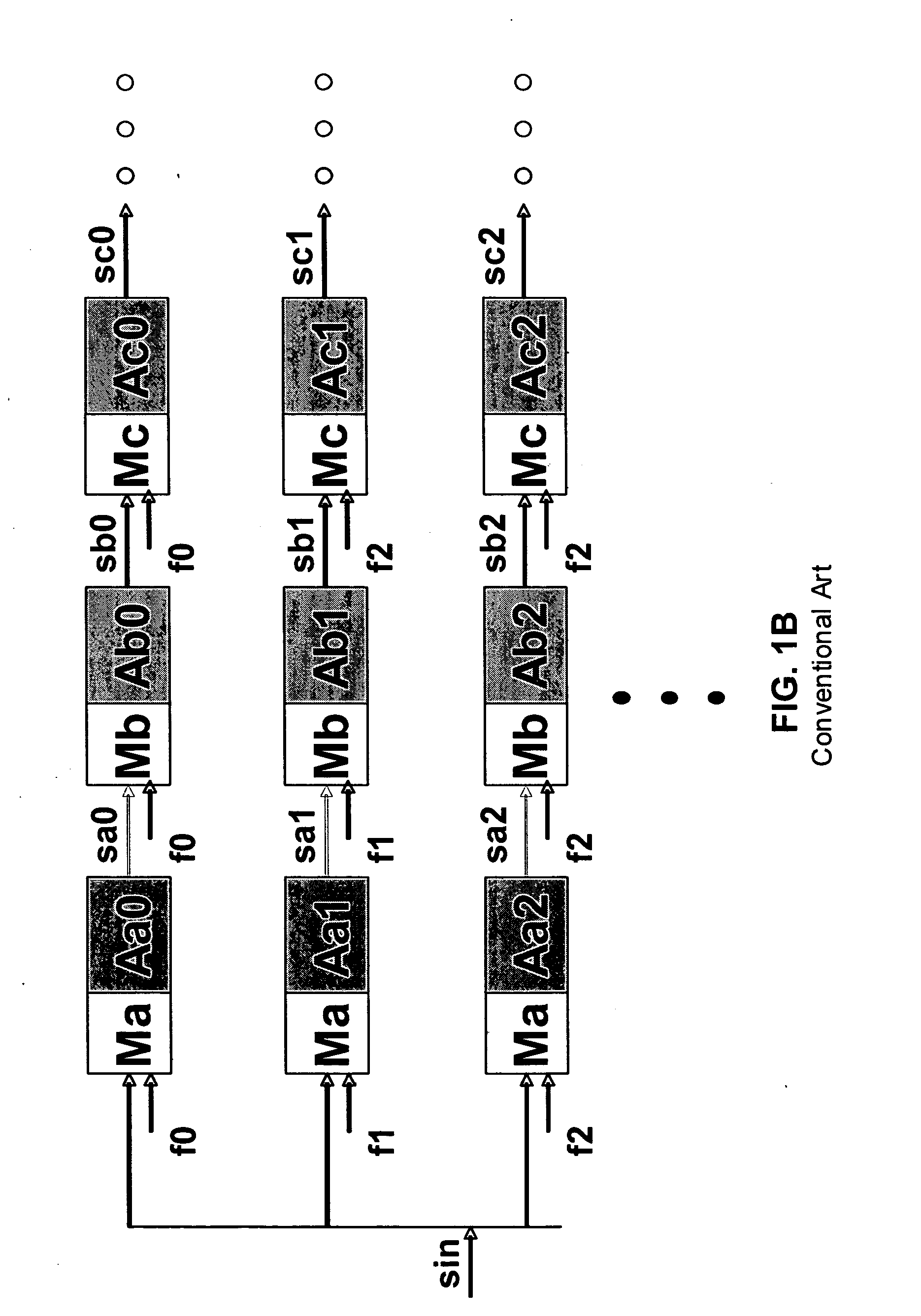

[0026]FIG. 2 shows the present invention in a generalized form. Shown in FIG. 2 are two stages “a” and “b” (of what can be a parallel hierarchy with more than two stages) of a device, with each stage having sampling devices M (Ma, Mb), analog or digital circuits A (Aa0-Aa2, Ab0-Ab5), clocked by the clock signals fa0-fa2 and fb0-fb5, with the data outputs sa0-sa2 and sb0-sb5, as shown in the figure. It will be appreciated that the number of devices in each stage is not limited to what is shown in FIG. 2.

[0027] The phase and frequency relationships between the various signals are illustrated in FIG. 3.

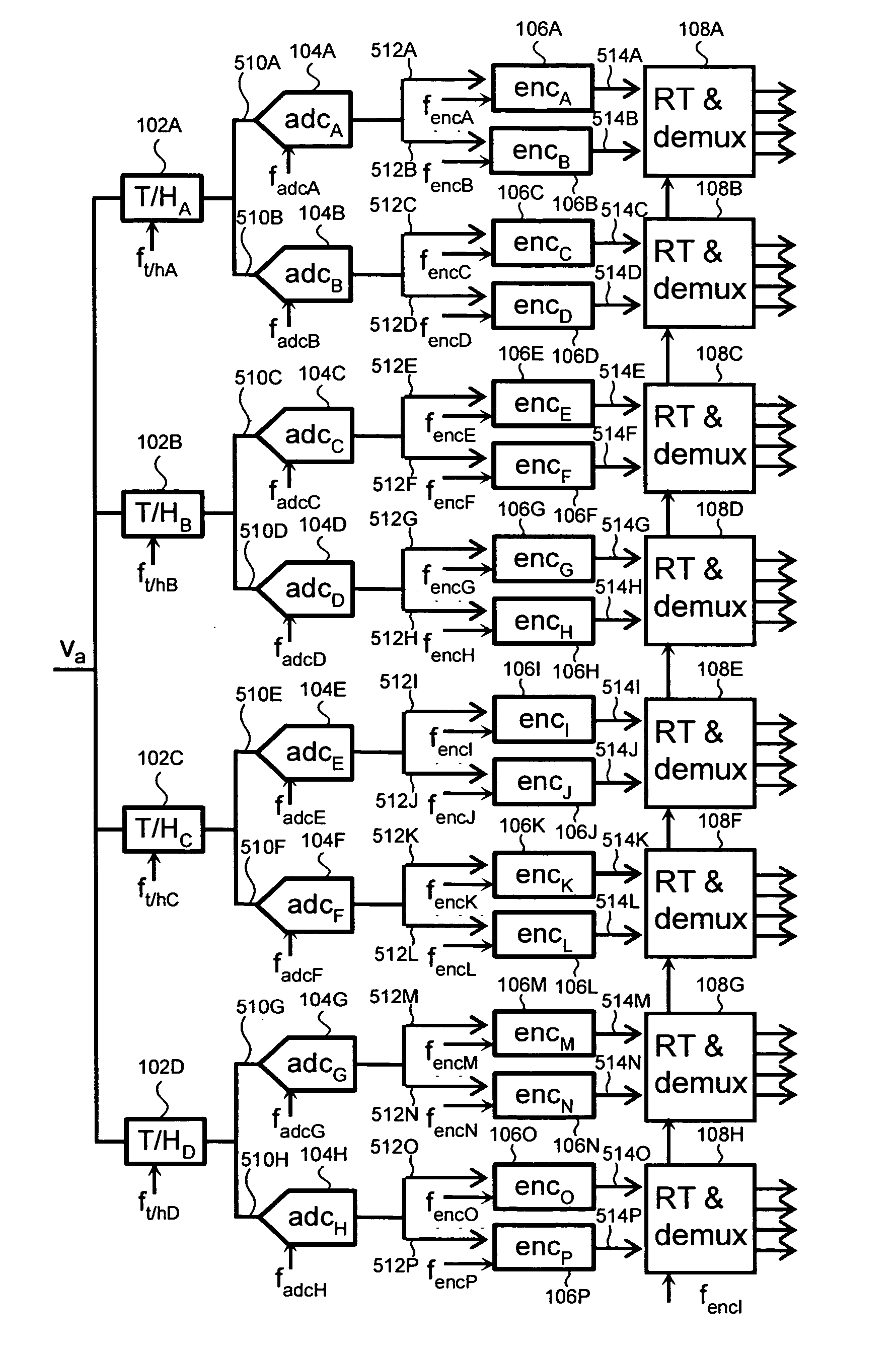

[0028]FIG. 4 illustrates how the multi-frequency multi-phase clock approach of FIGS. 2-3 may be applied to a programmable gain array, which, for example, can be one element of an ADC. Shown in FIG. 4 is a first stage comprising track-and-h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More