Alpha particle shields in chip packaging

a technology of alpha particles and chip packaging, which is applied in the direction of semiconductor devices, electrical equipment, semiconductor/solid-state device details, etc., can solve the problems of large soft errors in the chip during the normal operation of the chip, and achieve the effect of reducing the number of alpha particles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

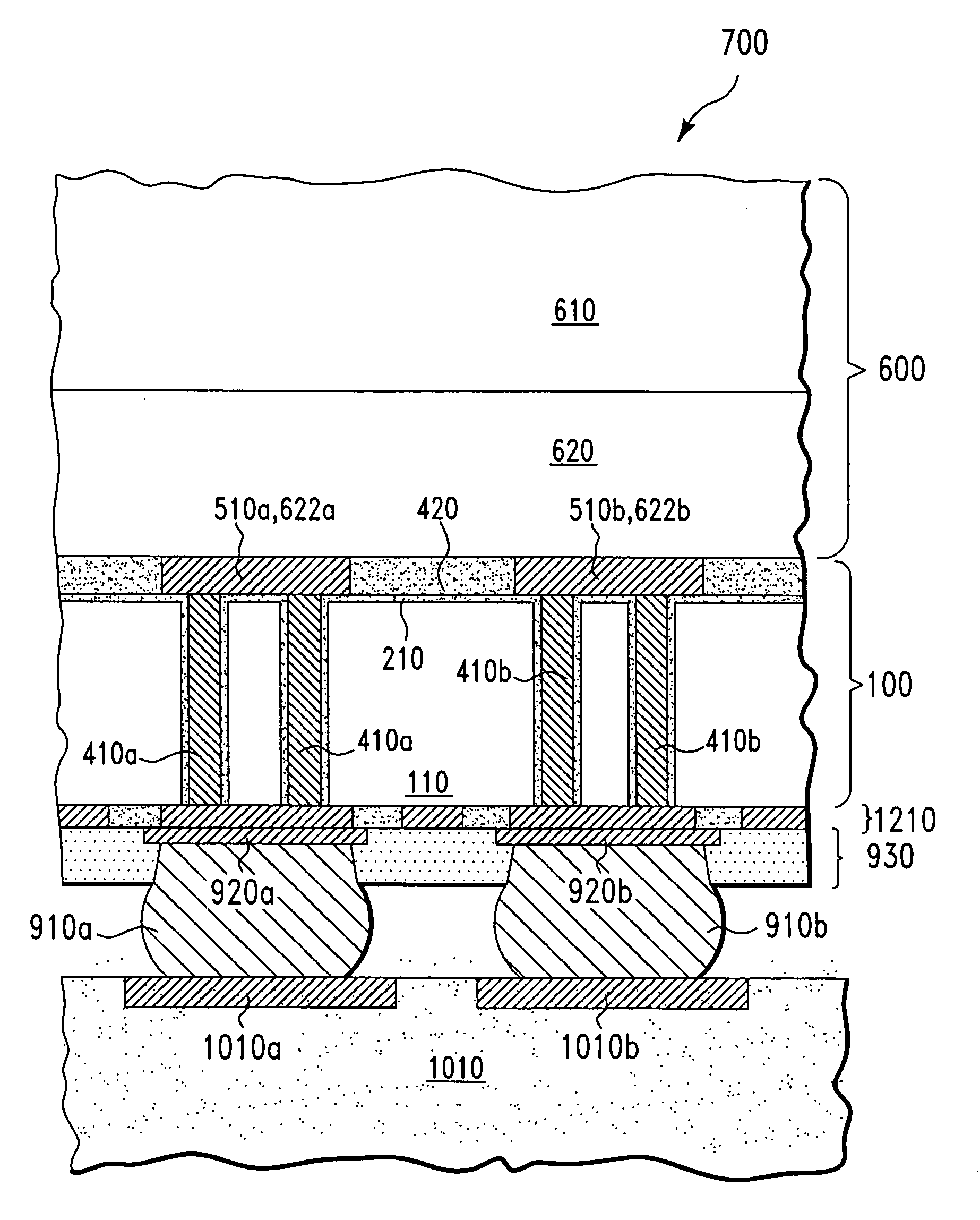

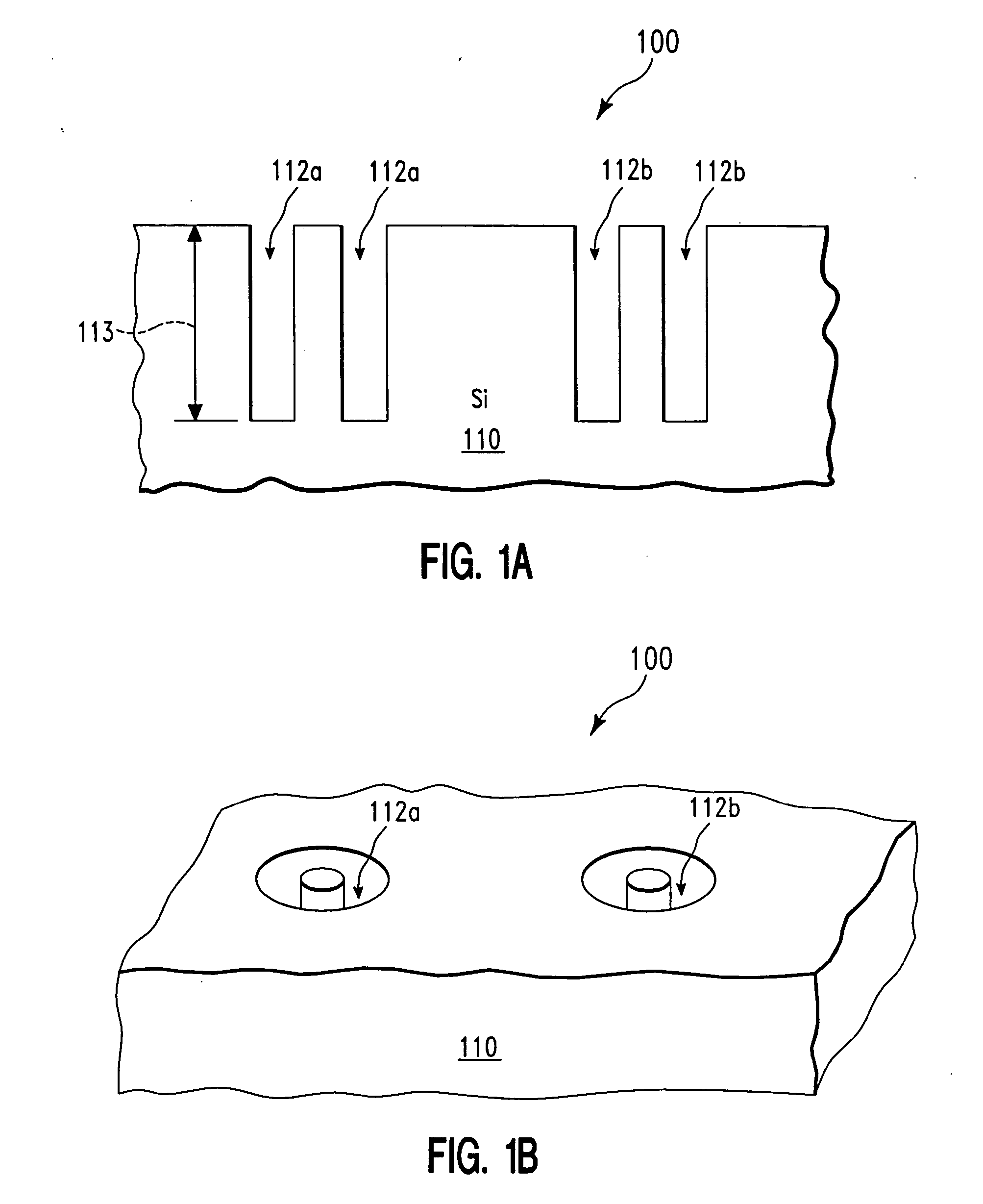

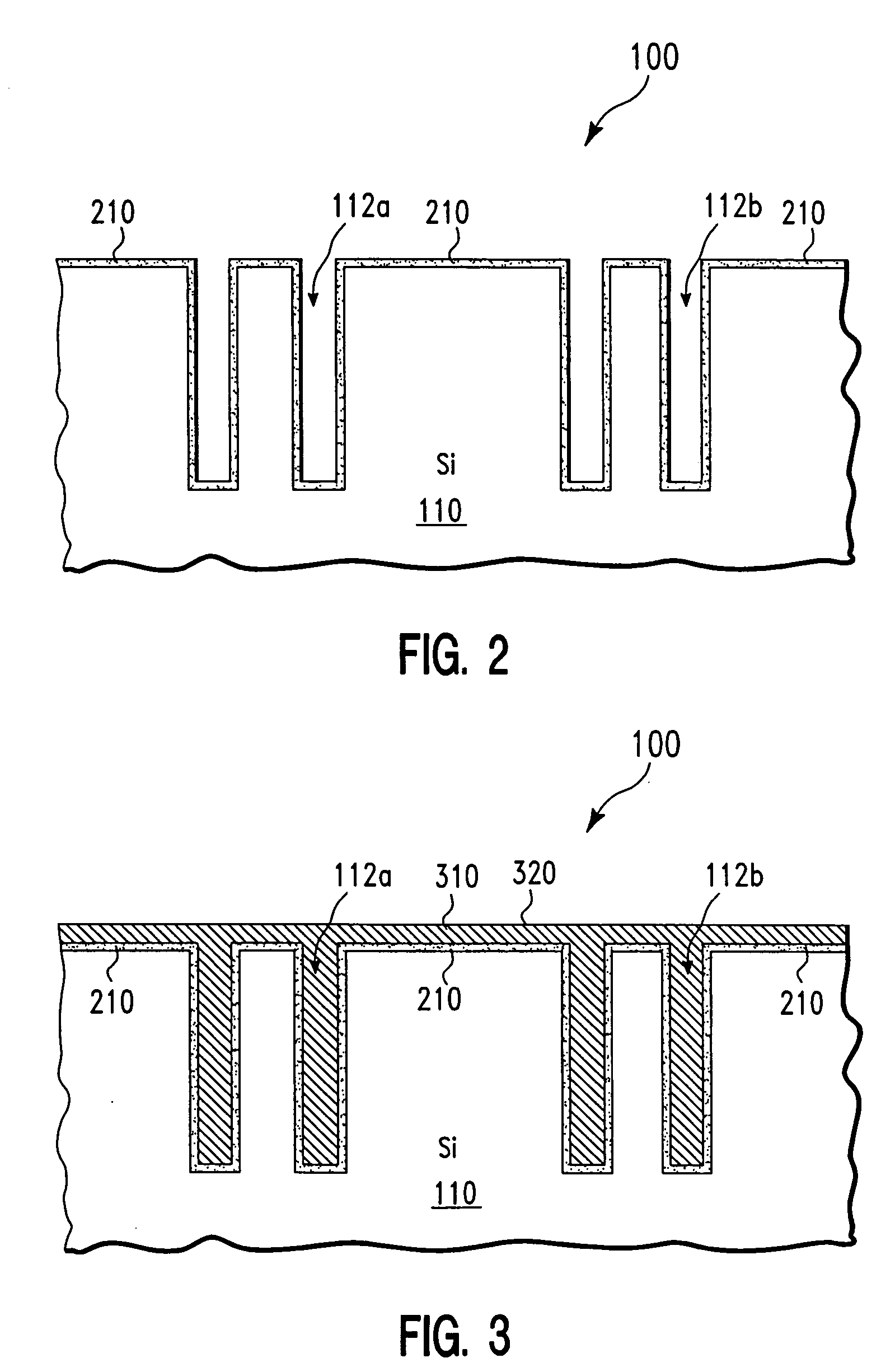

[0012]FIGS. 1-10 show the fabrication process for forming a structure 700 (FIG. 10), in accordance with embodiments of the present invention. More specifically, with reference to FIG. 1A, in one embodiment, the fabrication process starts out with an interposing shield 100 that comprises a semiconductor (e.g., silicon, germanium) layer 110. Next, in one embodiment, annular trenches 112a and 112b are formed in the semiconductor layer 110. Illustratively, the annular trenches 112a and 112b are formed using a photolithographic process. In one embodiment, the annular trenches 112a and 112b have a depth 113 of around 50-70 μm. FIG. 1B shows a perspective view of the interposing shield 100 of FIG. 1A.

[0013] Next, with reference to FIG. 2, in one embodiment, a dielectric film 210 is formed on exposed-to-ambient silicon surfaces of the interposing shield 100 of FIG. 1A. As a result, the dielectric film 210 forms on, among other places, bottom walls and side walls of the annular trenches 112...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More