Apparatus and method for testing electronic systems

a technology of electronic systems and apparatus, applied in the direction of digital circuit testing, testing circuits, instruments, etc., can solve the problems of increasing effort, reducing the consuming a lot of resources, so as to reduce the required amount of memory on the test chip, reliably validate system behavior, and eliminate redundant or unnecessary test cycles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

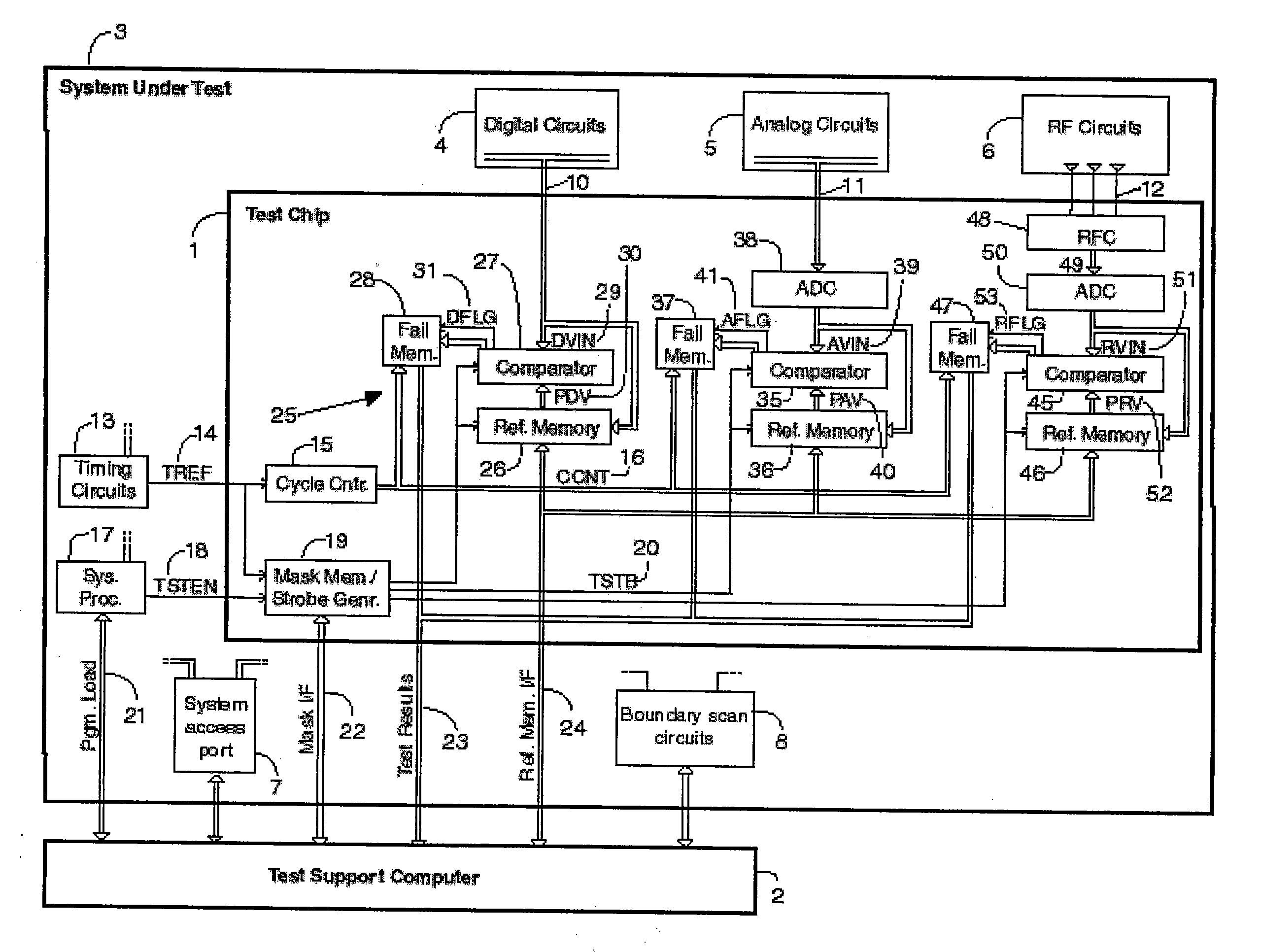

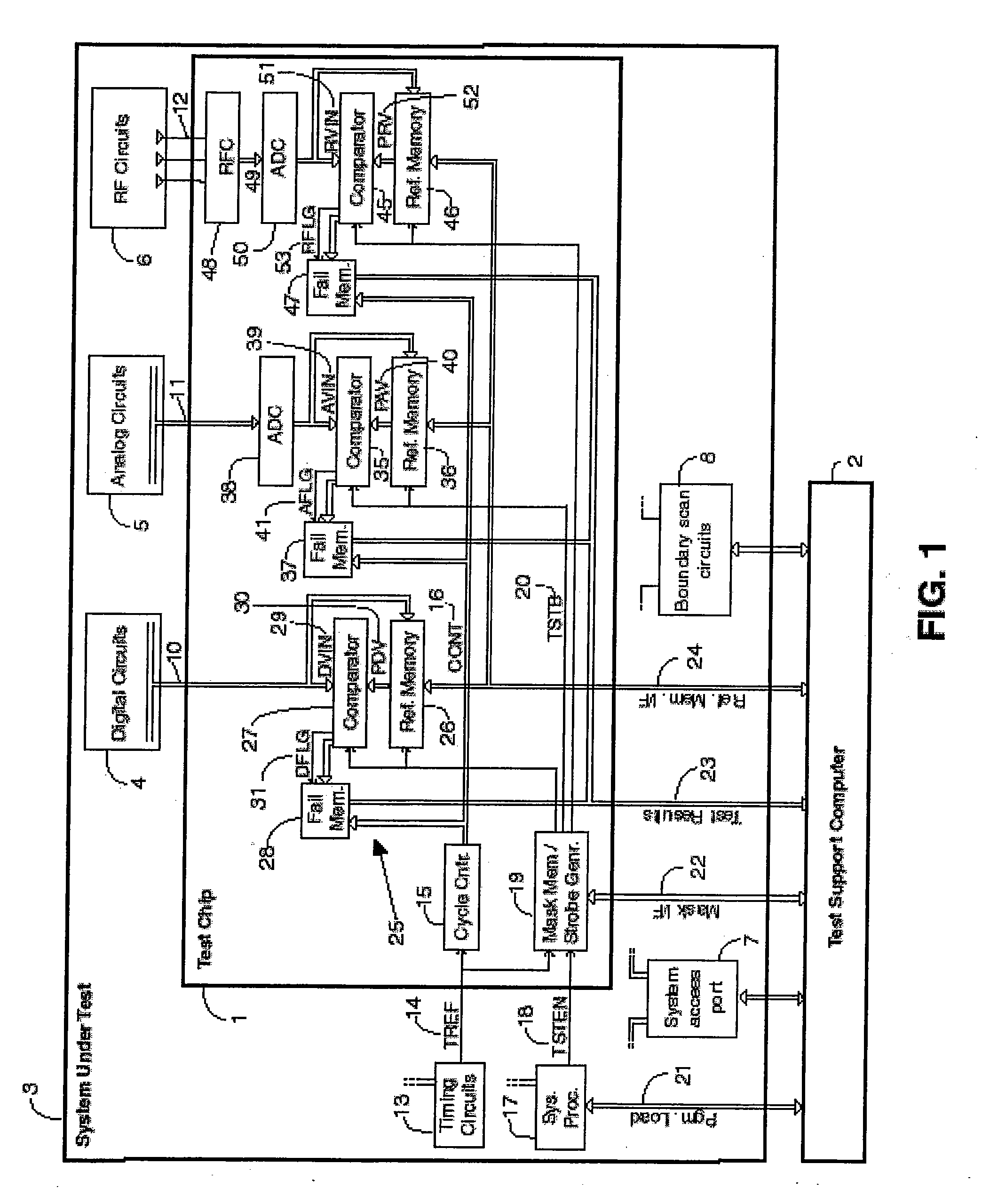

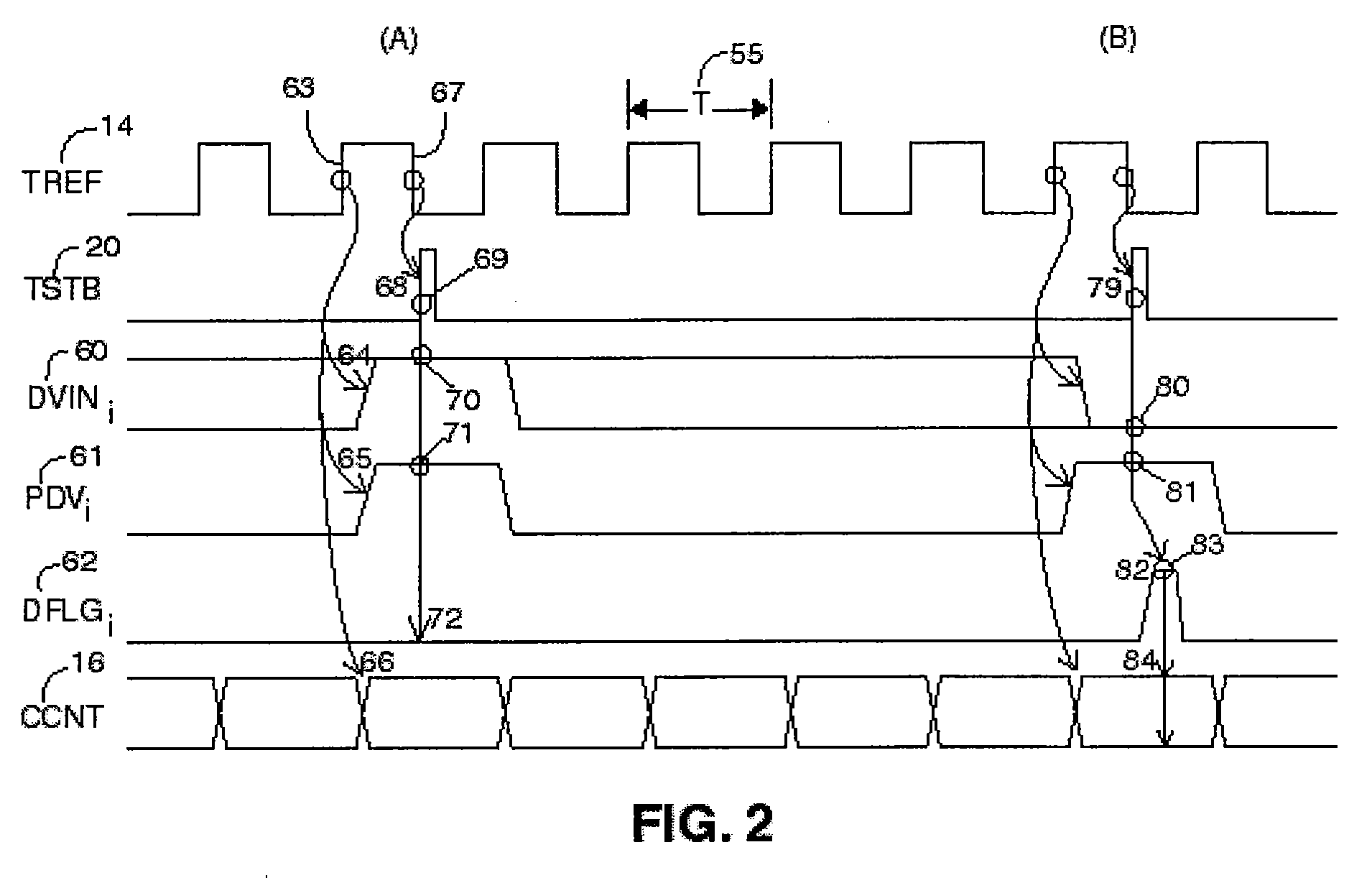

[0017]FIG. 1 shows a high-level block diagram of a test apparatus of the current invention including a test chip 1 and a test support computer 2 connected to the system under test (SUT) 3. SUT 3 includes digital circuits 4, analog circuits 5, and RF circuits 6. System access port 7 is preferably a high-density connection between SUT 3 and test support computer 2. This port is preferably used to validate the interconnection circuits of the SUT using continuity-testing circuits typically provided on a plug-in board within test support computer 2. Similarly, another plug-in board within test support computer 2 may include circuits for testing boundary scan circuits 8 of SUT 3. Plug-in boards can be used for these tests because the clock rates are typically slower than for functional testing; the test hardware is less demanding and is typically available as a commercial-off-the-shelf (COTS) item. Also, connecting wires or cables can be tolerated at the lower test frequencies. In combina...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More