Microprocessor protected against stack overflow

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

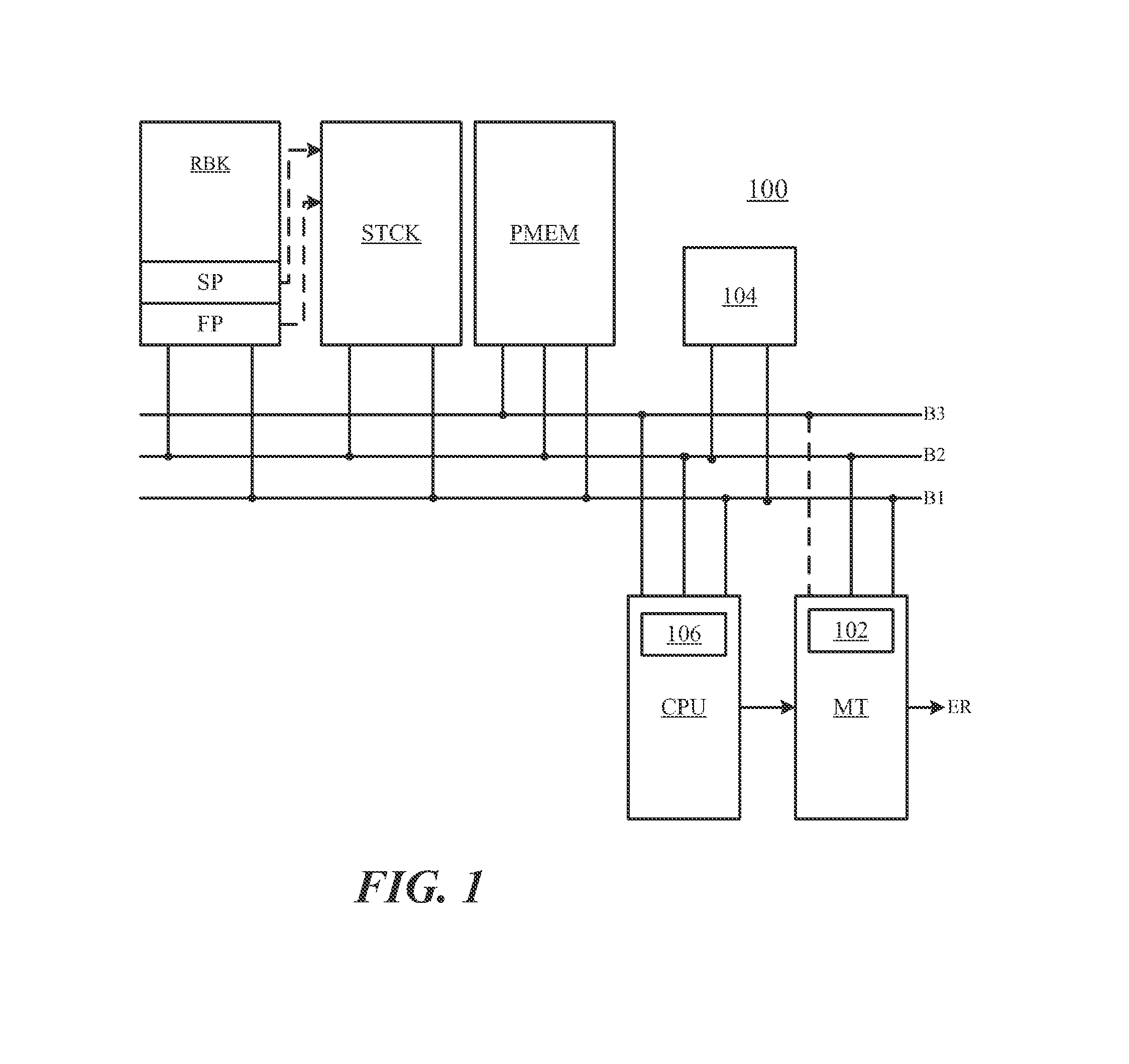

[0026]FIG. 1 shows a microprocessor 100 according to one embodiment. The microprocessor 100 includes a central processing unit CPU, hereinafter “the CPU”, a program memory PMEM, a call stack STCK, and a registry bank RBK. These different elements are linked by an address bus B1, a data bus B2, and an instruction bus B3.

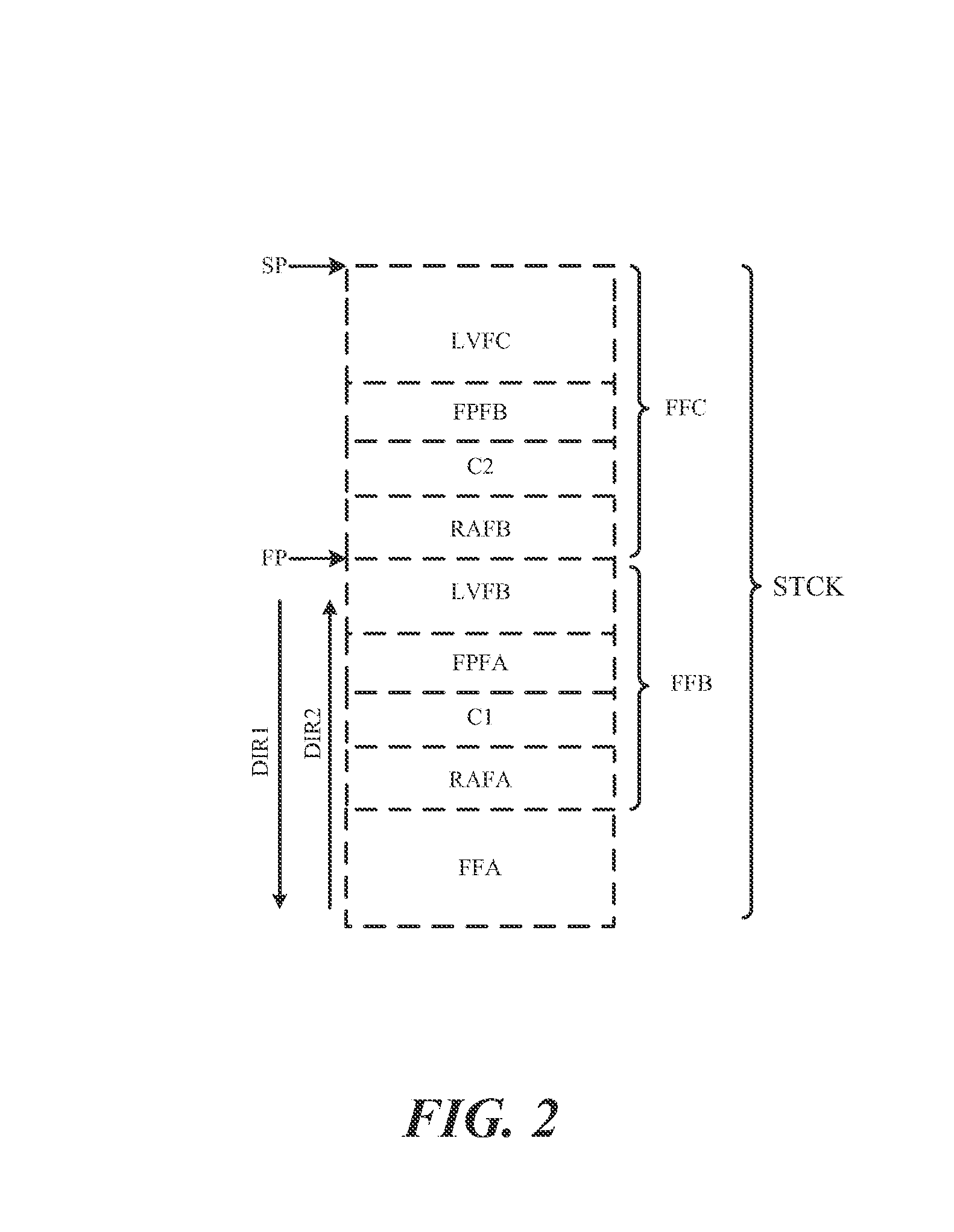

[0027]Registry bank RBK includes a stack pointer register SP and a frame pointer register FP. The stack pointer contains the address of the top of the stack STCK and the frame pointer contains the start address of a frame of a function being executed. Program memory PMEM contains a program executed by the CPU.

[0028]It will be noted that instruction bus B3 is an optional microprocessor element, its provision particular to the architecture used, here the Harvard architecture. A Von Neumann architecture only includes bus B2 to convey both the data and the instructions.

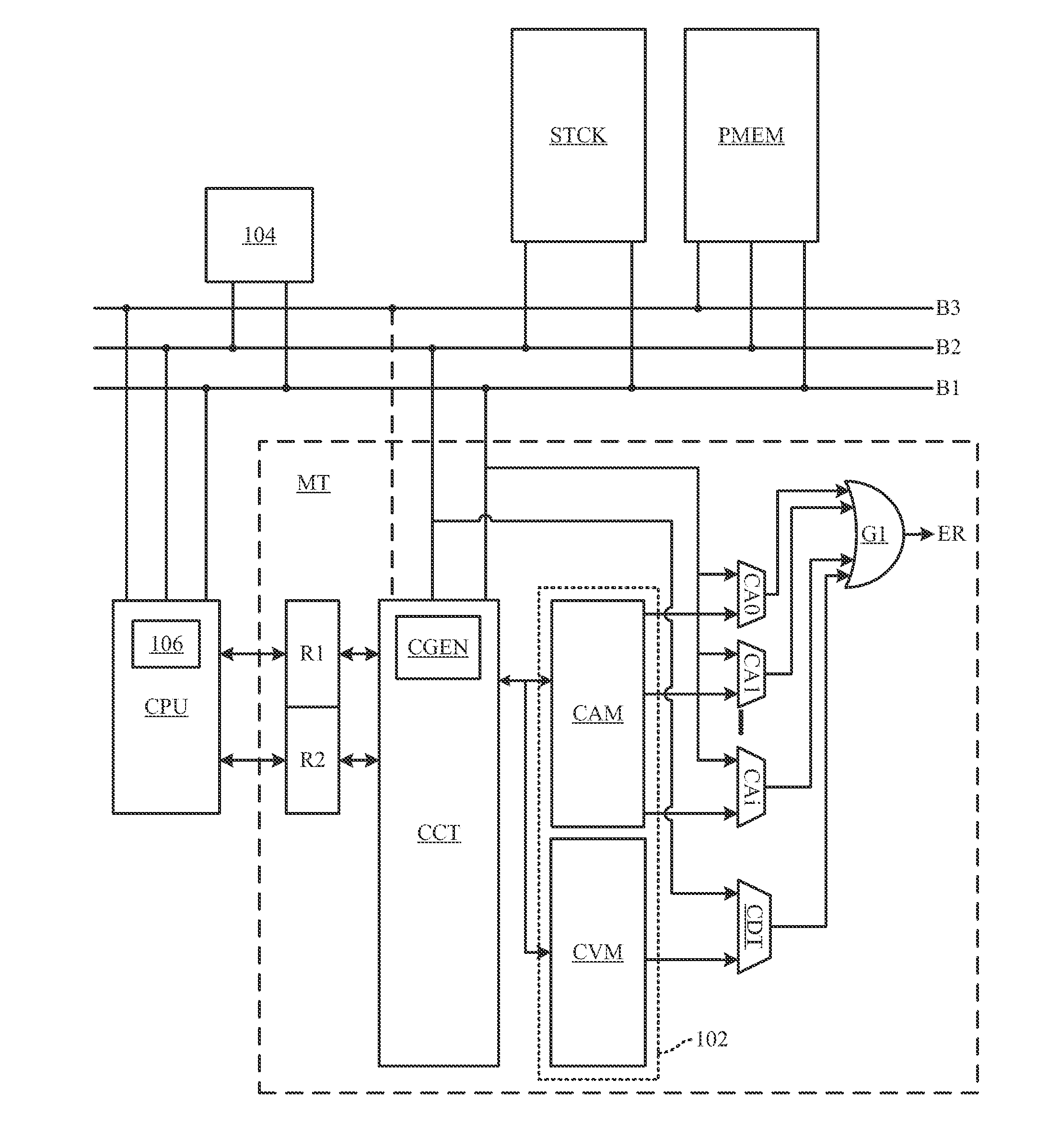

[0029]The microprocessor 100 also includes a stack monitor MT according to one embodiment. Monitor MT is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More