Physical unclonable function generation and management

a technology of function generation and management, applied in logic circuits, pulse techniques, reliability increasing modifications, etc., can solve problems such as process variations of integrated circuits that present a fundamental reliability challenge, process variability degrades the performance of measurement circuits, and inherent contradictions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

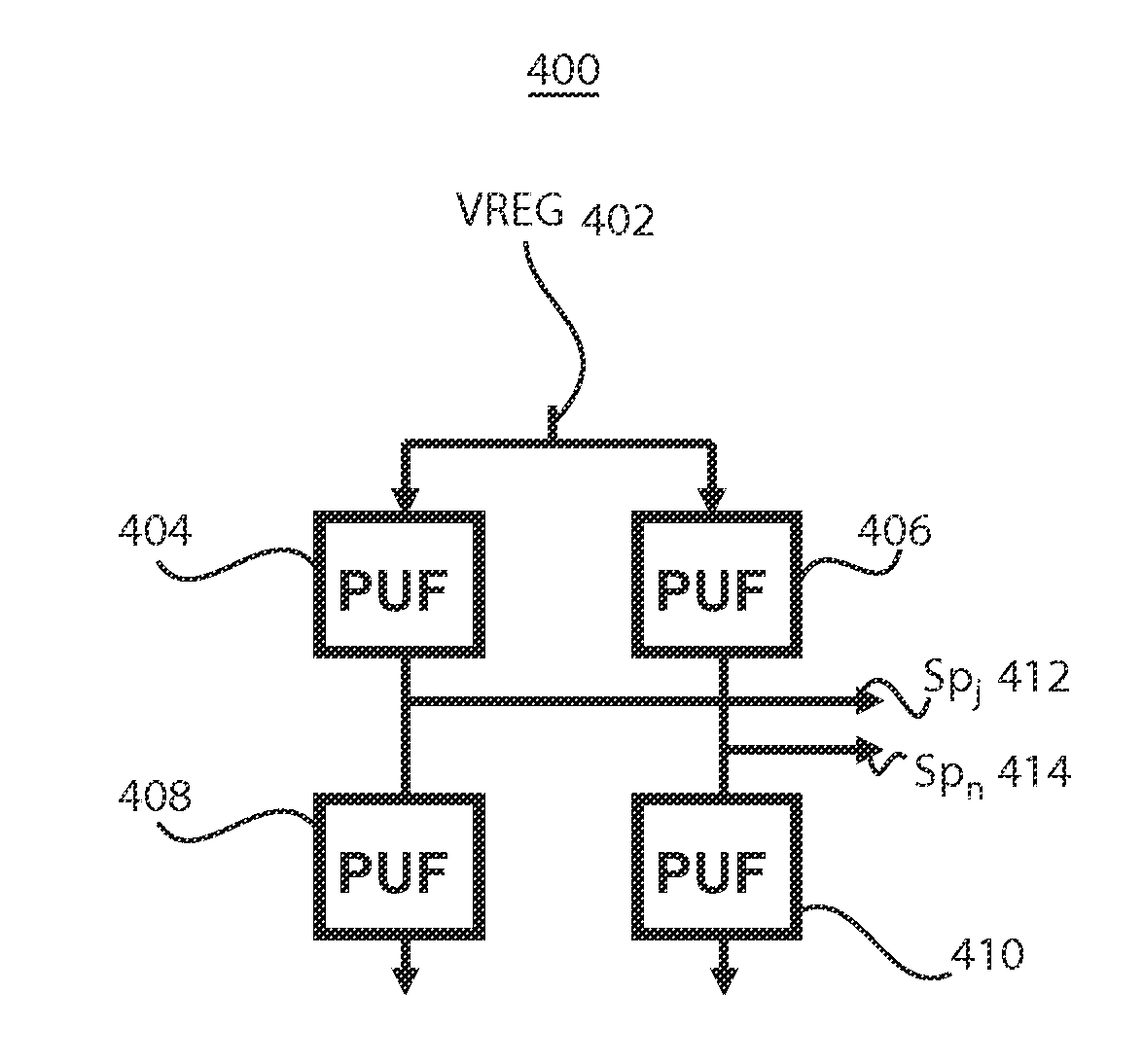

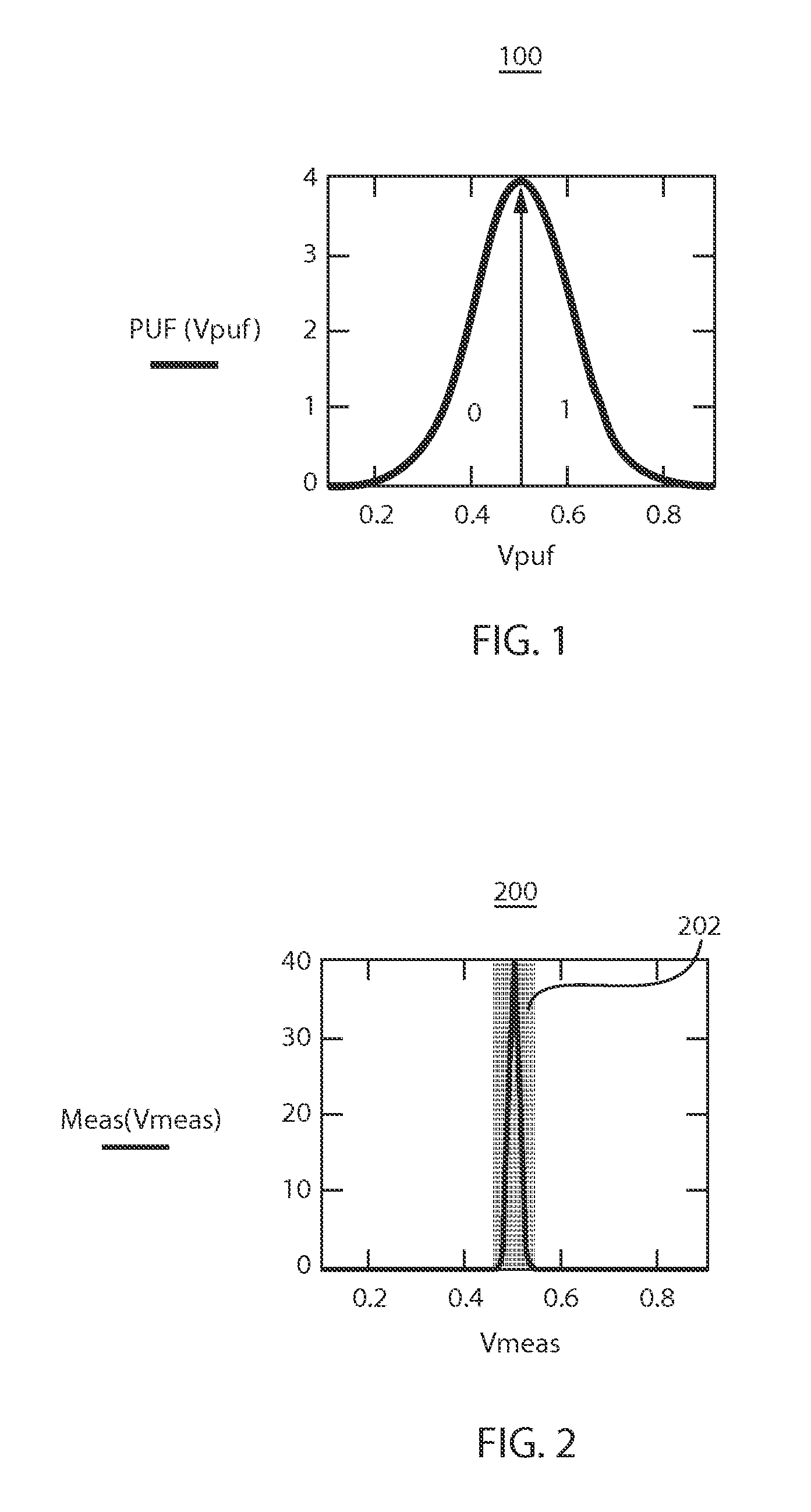

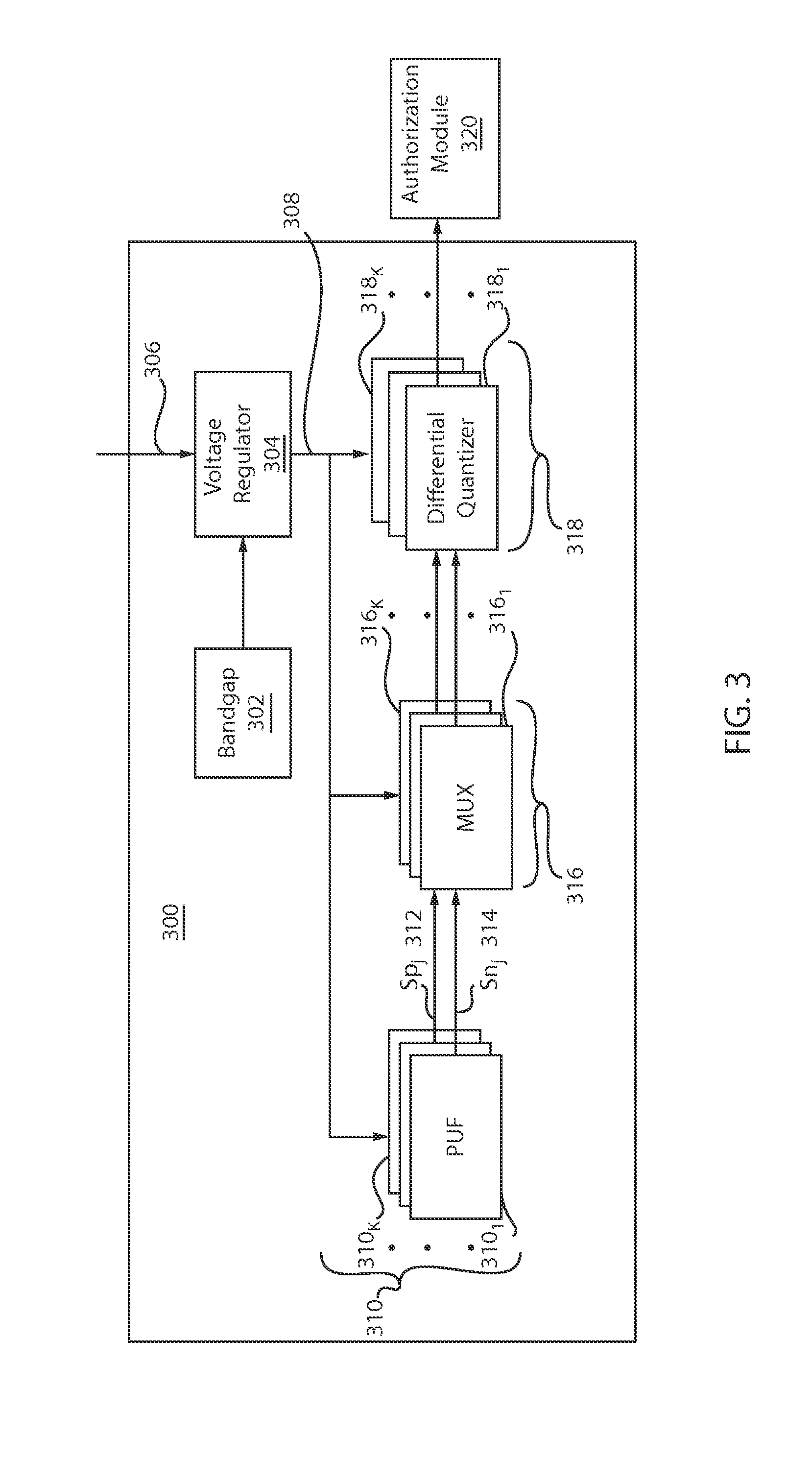

[0026]As noted above, process variability leads to an inherent incertitude in measurement of PUF states. However, other factors also contribute to measurement error. For example, the temperature of circuit elements, noise, aging effects, radiation and supply voltage variations can lead to a drift in the PUF probability distribution function (PDF) and also to an expansion of the measurement error. For example, these additional factors can cause a drift of the PDF 102 in FIG. 1 to the right or left and can cause an expansion of the incertitude zone 202 in FIG. 2 to the right and / or to the left. Thus, these additional factors can decrease the effectiveness of on-chip PUF systems.

[0027]The exemplary embodiments described herein incorporate features that can mitigate the dependence of a PUF on temperature, noise, aging, radiation and / or supply voltage variations to provide a robust and reliable PUF scheme. For example, PUF variability can be reduced by employing a differential of PUF sta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More