Manufacturing method of power semiconductor

a manufacturing method and technology of power semiconductor, applied in the direction of semiconductors, electrical devices, transistors, etc., can solve the problems of unlimited characteristics of power semiconductors, reduce the processing efficiency of power semiconductors, limit the melting point of surface metals, etc., to achieve the effect of reducing the drawbacks of phenomenon, reducing the thickness of wafers, and reducing the processing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016]The present invention will now be described more specifically with reference to the following embodiments. It is to be noted that the following descriptions of preferred embodiments of this invention are presented herein for purpose of illustration and description only. It is not intended to be exhaustive or to be limited to the precise form disclosed.

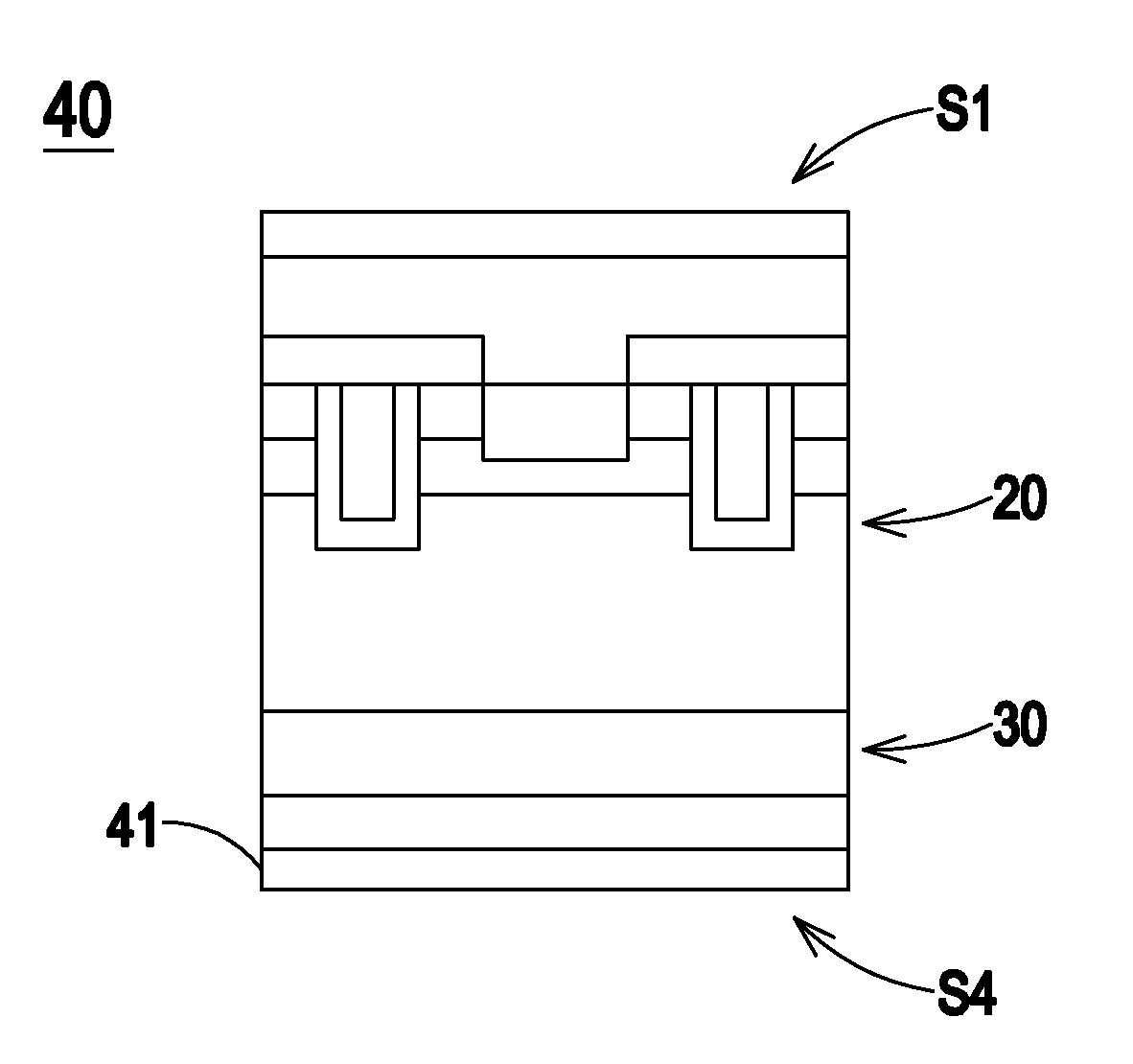

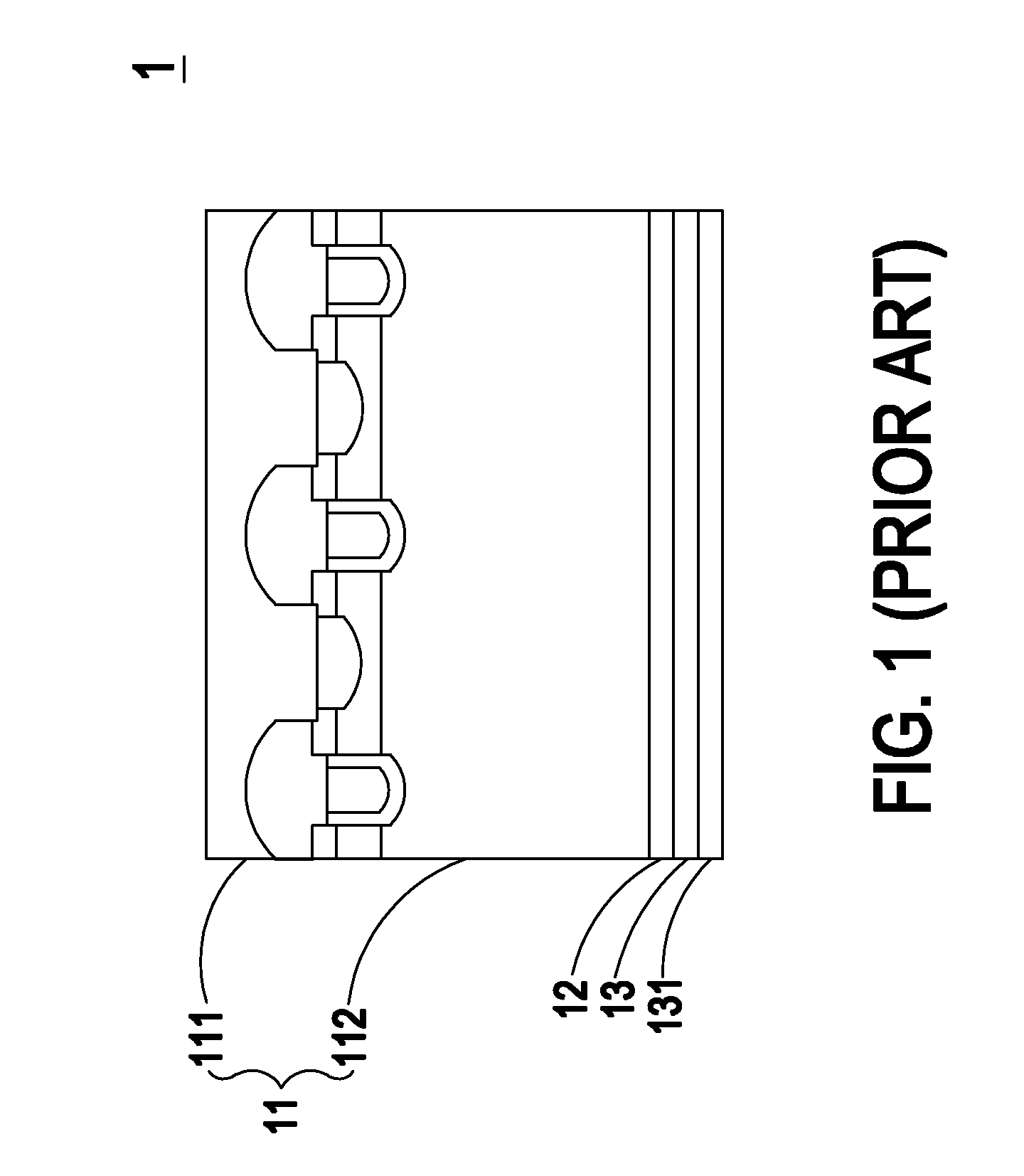

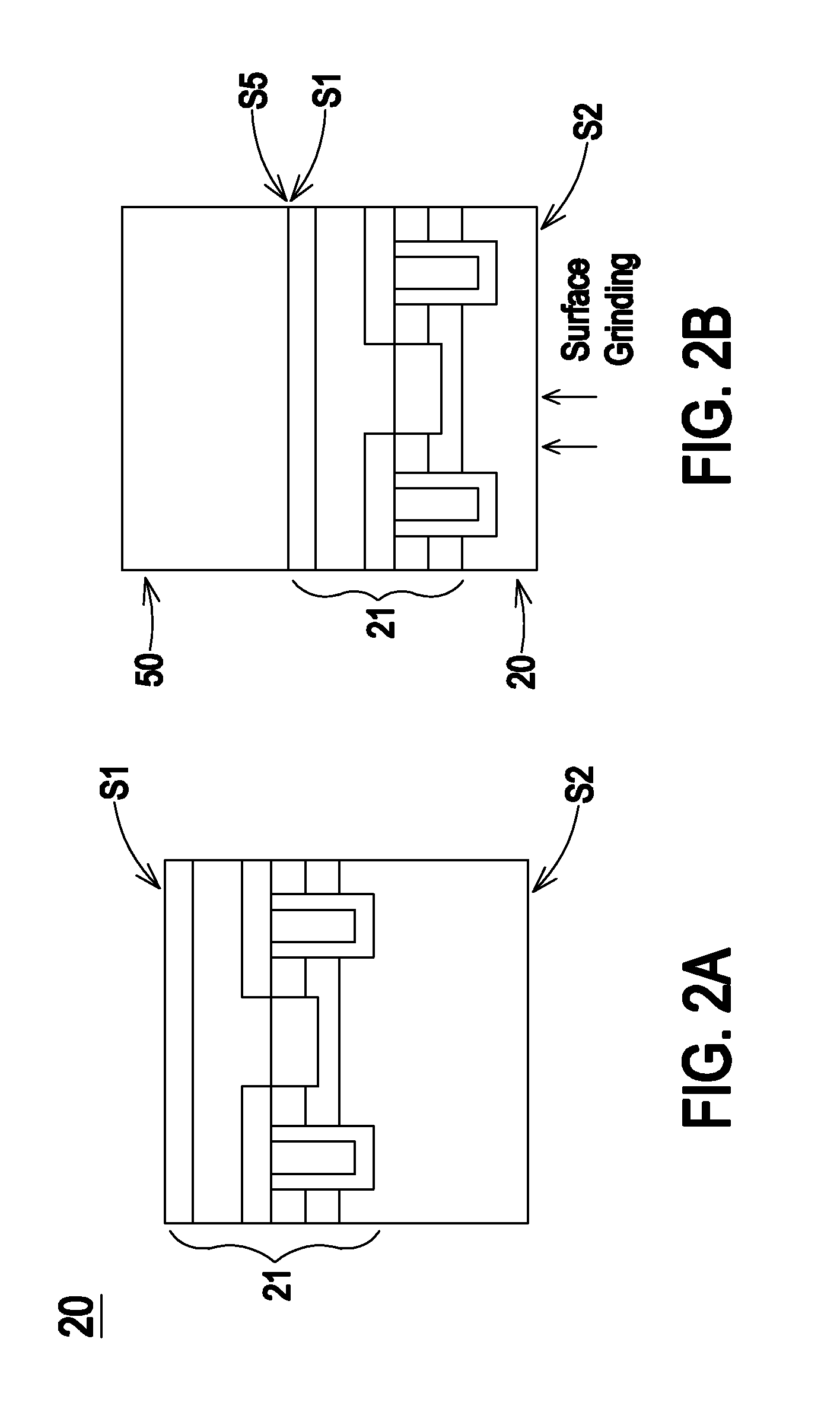

[0017]Please refer to FIG. 2A to FIG. 2GFIG. 2A to FIG. 2G schematically illustrate the structures corresponding to the steps of a manufacturing method of a power semiconductor according to an embodiment of the present invention. A manufacturing method of a power semiconductor of the present invention includes steps as following. First, as shown in FIG. 2A and FIG. 2C, providing a first semiconductor substrate 20 and a second semiconductor substrate 30, among which the first semiconductor substrate 20 is not limited to a N-type semiconductor wafer made of a N-type floating zone substrate, and the first semiconductor substrate 20 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More