Semiconductor package structure and producing method thereof

A packaging structure and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem of incident angle deflection, solder ball 16-size solder ball 16 distance reduction, and affect the accuracy of sensing Degree and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

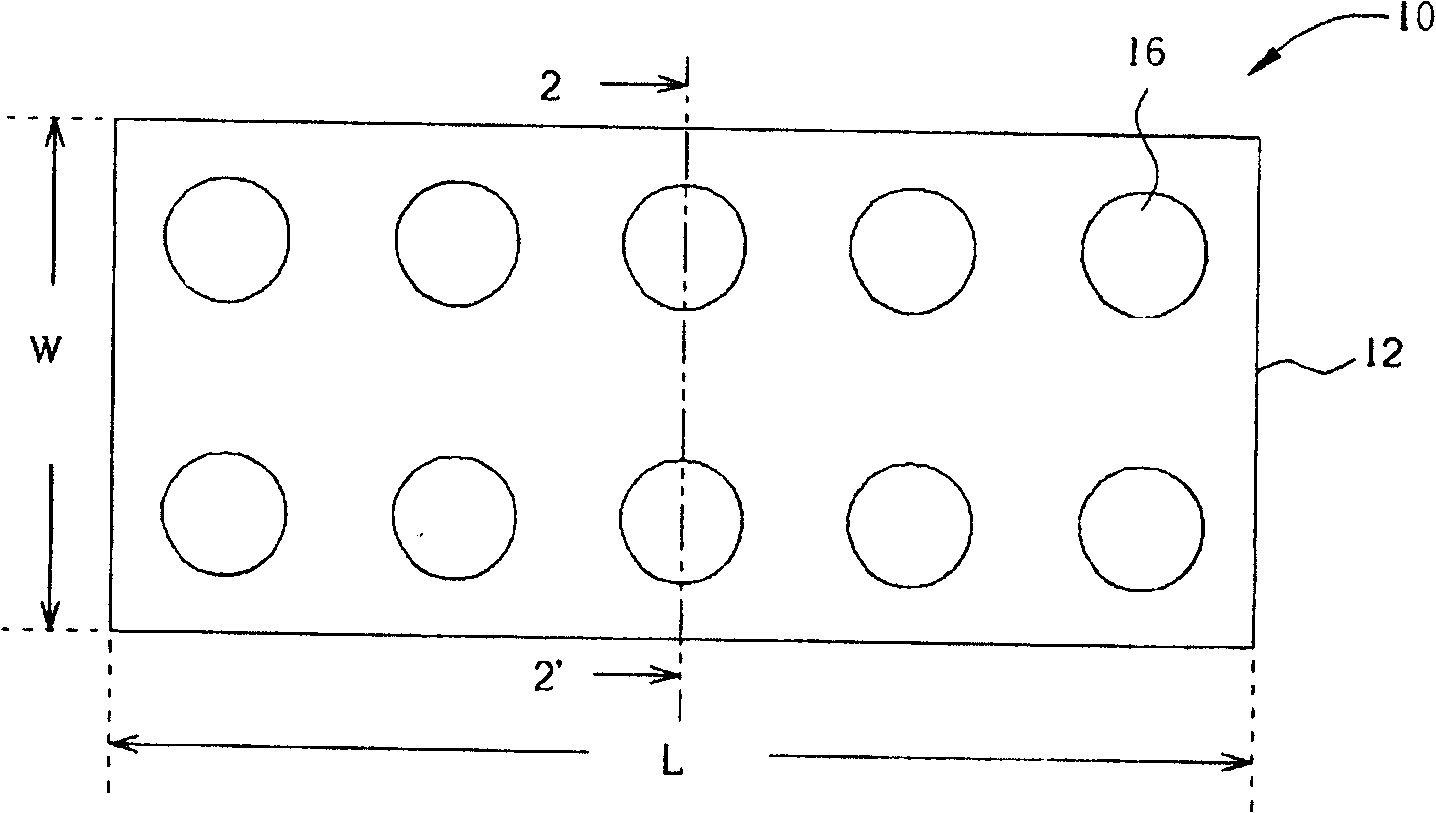

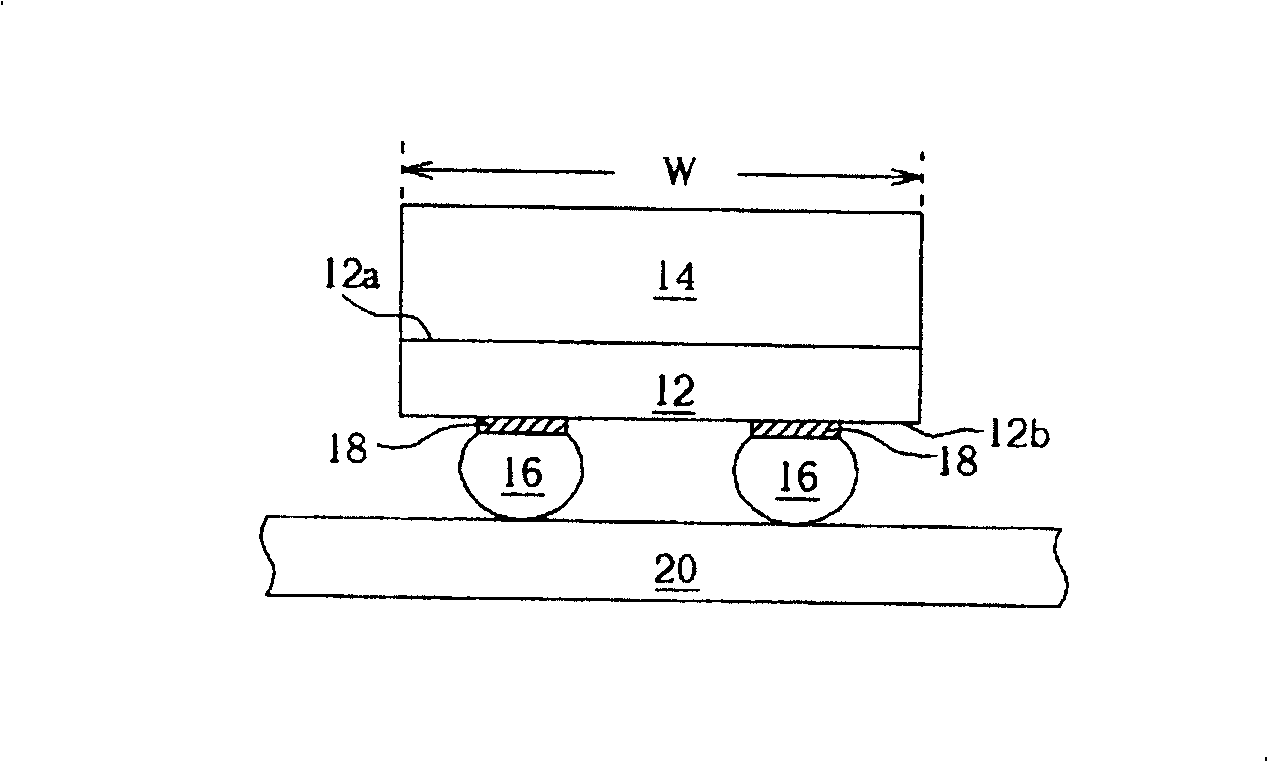

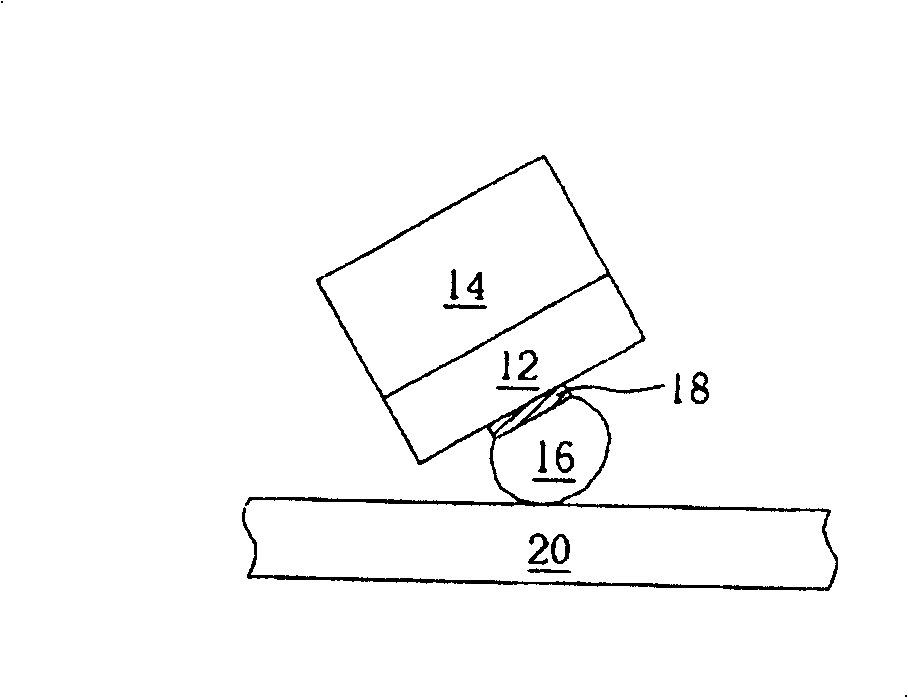

[0030] Please refer to Figure 4 to Figure 6 , Figure 4 It is a bottom view of the semiconductor package structure of the first embodiment of the present invention, Figure 5 for Figure 4 The schematic cross-sectional view of the semiconductor package structure shown along the tangent line 5-5', while Image 6 for Figure 4 The schematic cross-sectional view of the semiconductor package structure shown along the line 6-6'. Such as Figure 4 and Figure 5 As shown, a semiconductor package structure 30 includes a substrate 32 having an upper surface 32a and a lower surface 32b, a chip 34 is disposed on the upper surface 32a of the substrate, a plurality of solder pads 38 are disposed on the lower surface 32b of the substrate 32, and A plurality of bonding balls (bonding balls) 36 are respectively disposed on the surface of each bonding pad 38 . Wherein, the chip 34 is an image sensor chip, such as a CMOS image sensor device or a charge-coupled device, and the chip 34 ca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More