Multiple-core multi-CPU threading dispatch execution method based on hardware resource

A central processing unit and hardware resource technology, applied in the field of thread allocation, can solve problems such as resource conflicts, improve test efficiency and avoid resource competition

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

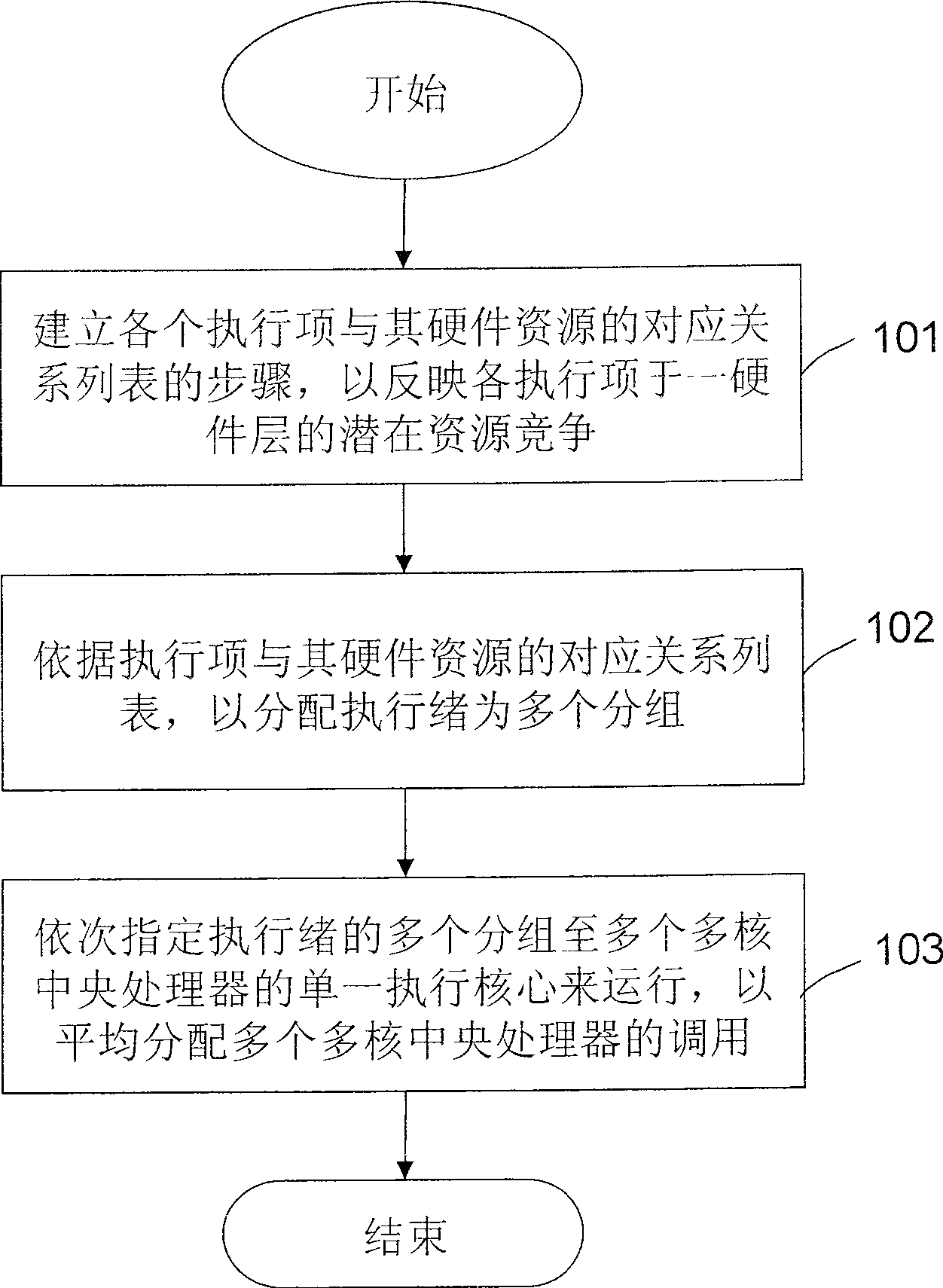

Method used

Image

Examples

Embodiment Construction

[0026] Hereinafter, the preferred embodiments of the present invention will be described in detail with reference to the drawings.

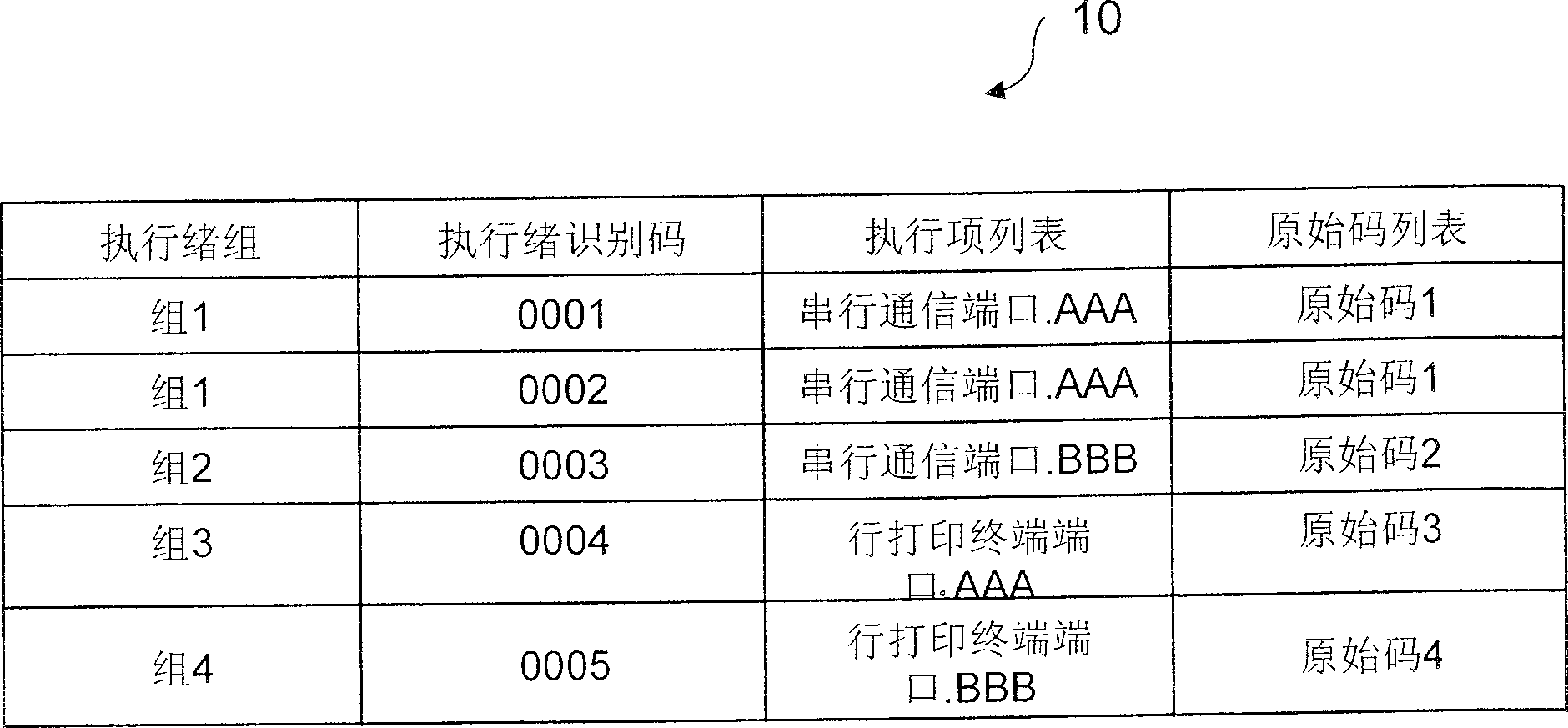

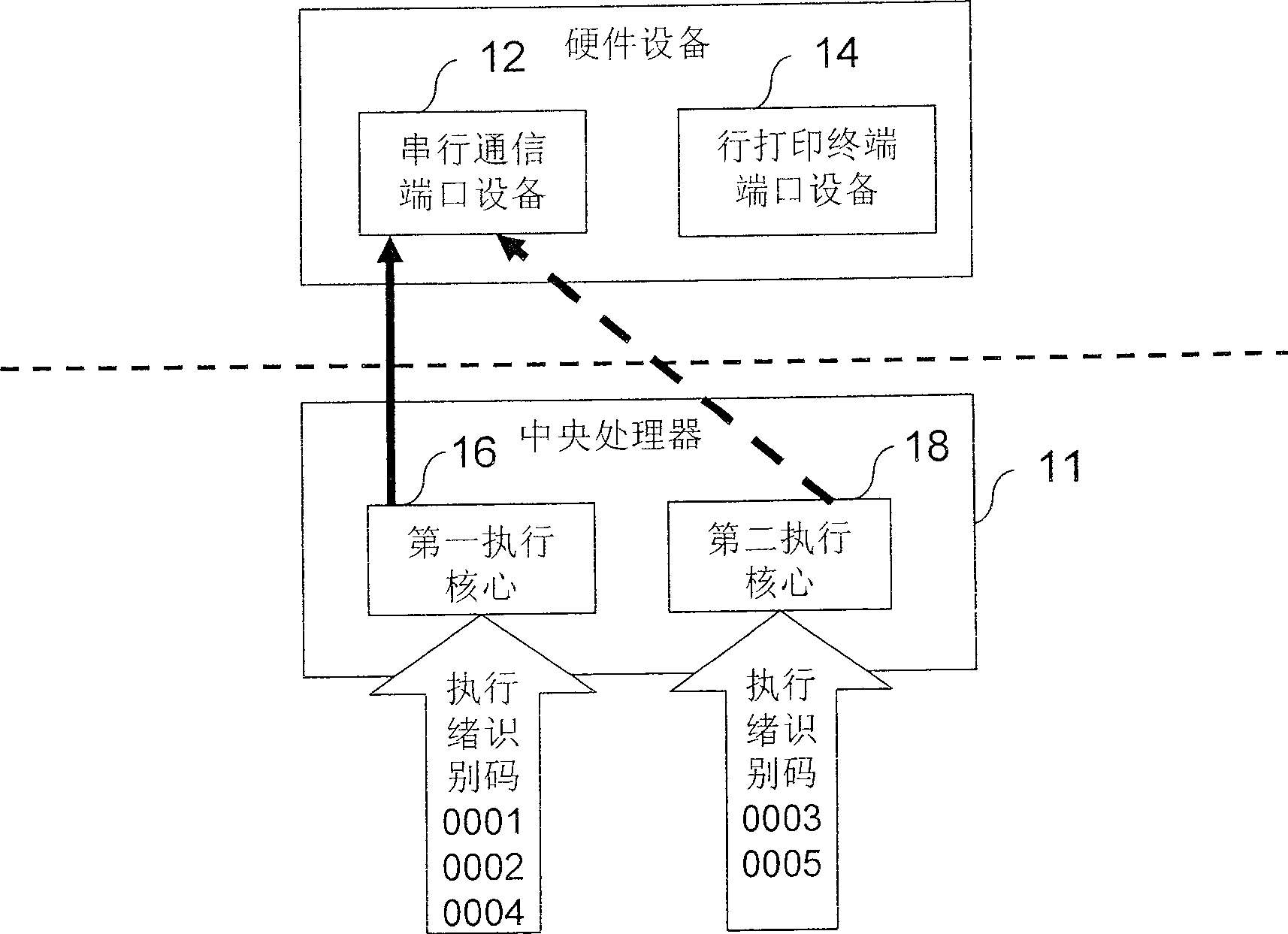

[0027] Please refer first figure 1 versus figure 2 The prior art multi-thread allocation method is described. figure 1 It is an embodiment of the prior art to execute a thread grouping chart when hardware devices are not considered; and figure 2 This embodiment of the prior art is a schematic diagram of the execution of the thread call to the hardware layer when the hardware device is not considered.

[0028] Such as figure 1 As shown, according to an existing thread scheduling allocation mechanism, that is, the thread grouping chart 10 obtained after allocation without considering the hardware device is divided into four groups, among which the threads corresponding to different groups There is no software layer resource competition between. figure 2 Shows the execution of thread scheduling to the hardware layer without considering the hardwar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More