Logic analyzer and its waveshape displaying method

A logic analyzer and waveform display technology, applied in the field of logic analyzers, can solve the problem that waveform data cannot correctly reflect waveform characteristics, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

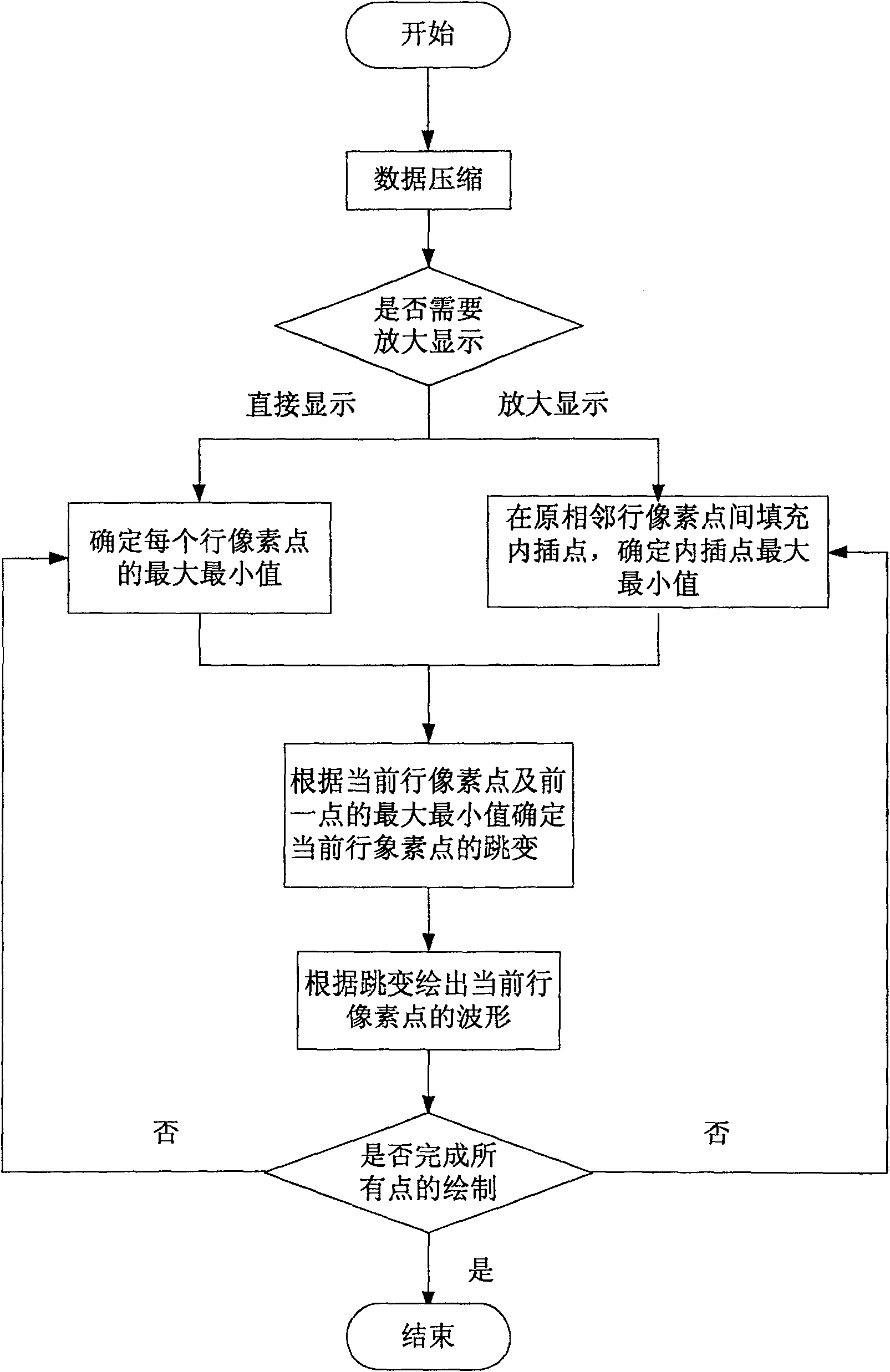

[0031] This embodiment describes in detail the display of the logic analyzer in the running state. At this time, the logic analyzer needs to compress the data and display it while collecting the data.

[0032] Firstly, the logic analyzer stores the collected waveform data points in the storage device, and then fetches the waveform data points from the storage device for display. Generally, the number of stored waveform data points is larger than the row pixels of the screen. If all the stored waveform data points are to be displayed on the display at one time, these data points need to be compressed.

[0033] Firstly, the collected waveform data points are compressed into data points of screen row pixels. At this time, each compressed waveform data point is composed of multiple bits of the collected waveform data points. Then, for each compressed data point, all the bit phases are ORed to obtain a maximum value, and all the bit phases are ANDed to obtain a minimum value, and ...

Embodiment 2

[0056] This embodiment describes in detail the situation that the logic analyzer needs to enlarge and display the compressed waveform. At this time, you can choose the amplification ratio by selecting the gear of the logic analyzer.

[0057] When the number of data points to be displayed is less than the number of screen row pixels, it is necessary to fill the interpolation points between the two row pixel points so that the waveform can be displayed continuously. The present invention provides an interpolation method, which uses the maximum and minimum values of the previous point in adjacent rows of pixel points during compressed display as the maximum and minimum values of the interpolation points to form multiple interpolation points. In this way, the maximum and minimum values of pixels in each row after the enlargement are determined.

[0058] Like the compressed display method, it is also necessary to determine the display mode of the pixels in the current row ac...

Embodiment 3

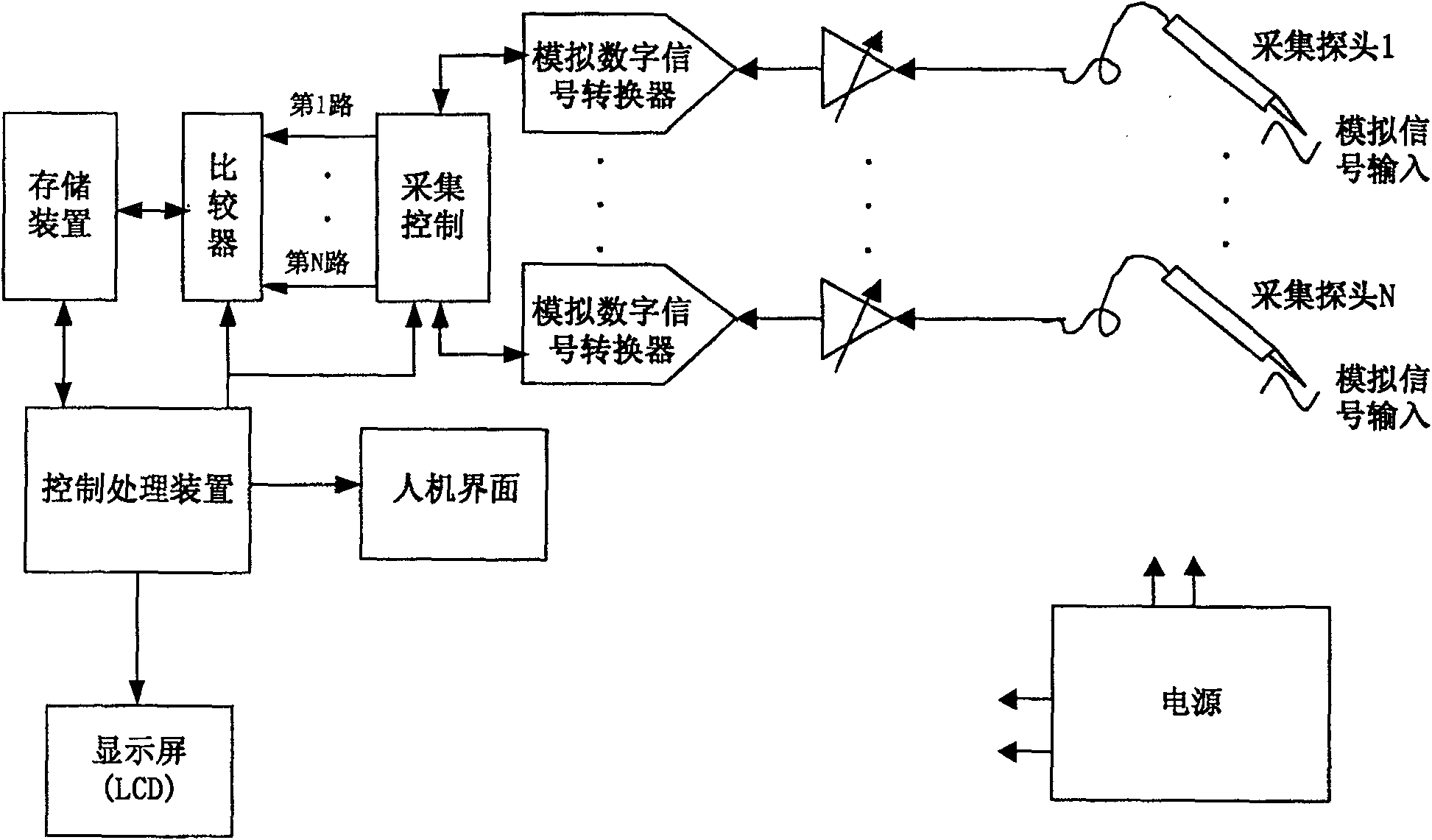

[0061] This embodiment is a logic analyzer. Figure 4 It is the structural diagram of the logic analyzer of this embodiment. As shown in the figure, the logic analyzer of the present invention adds a data scaling device and a display processing device on the basis of the existing logic analyzer, and they are respectively connected with the control processing device. The data scaling device is used to compress and display the collected waveform data points according to the control of the control processing device, or to enlarge and display the compressed points according to an external response instruction. The display processing device determines the display mode of each row of pixels according to the compressed or enlarged maximum and minimum values of each row of pixels, and finally displays it on the screen.

[0062] Such as Figure 5 As shown, the data scaling device further includes a data reduction unit, a data amplification unit and an interpolation unit. The data r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More