Digital phase lock loop and its clock adjusting method

A digital phase-locked loop and clock adjustment technology, used in the clock adjustment of digital phase-locked loops and high-precision digital phase-locked loops, can solve the problems of output clock glitches, short-term clock overlap, etc., to prevent glitches and achieve dynamic compensation. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

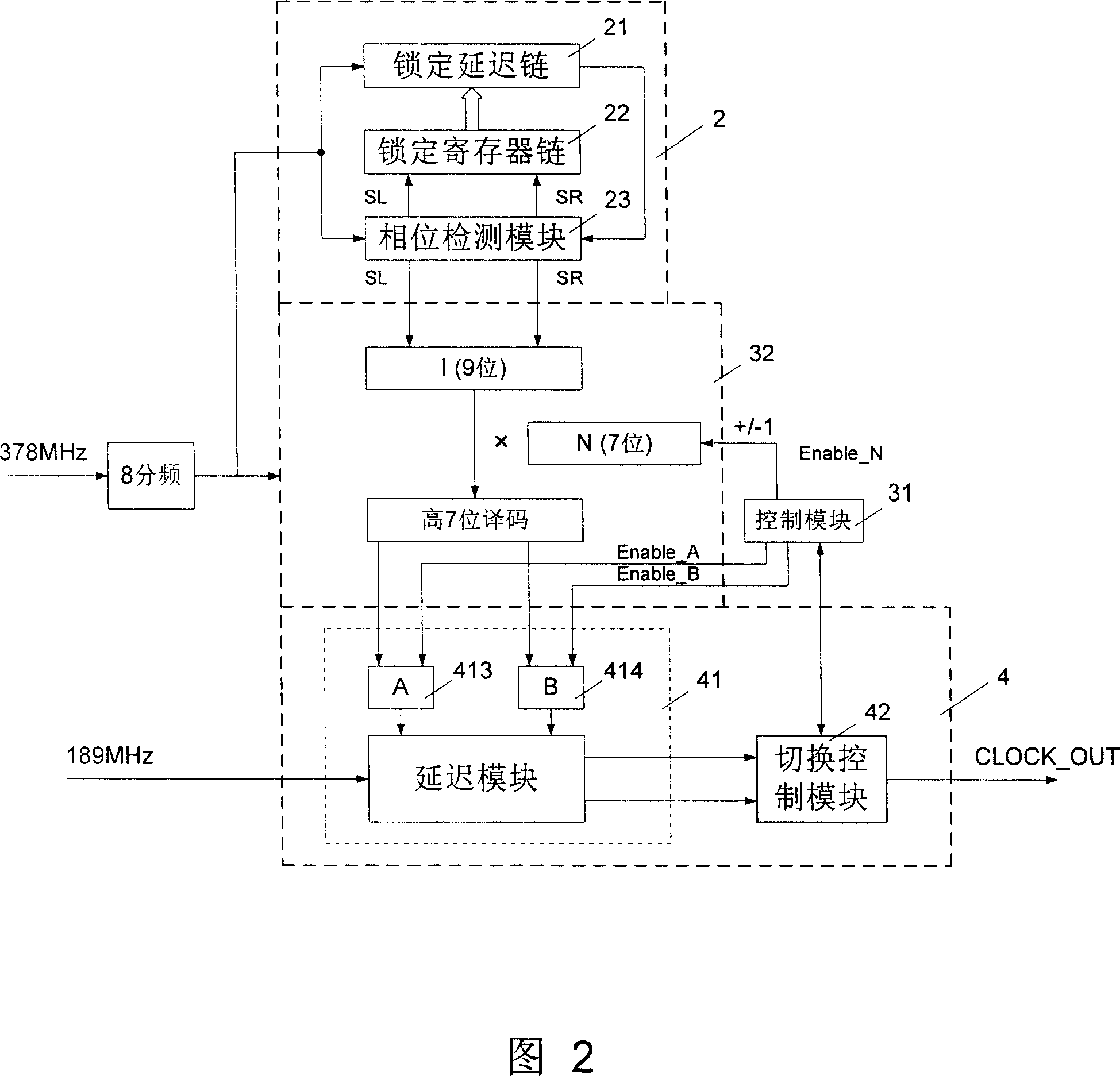

[0051] In this embodiment, the dynamic compensation of the delay chain and the adjustment of the clock are realized by switching between the two delay chains, so as to prevent serious glitches of the clock while providing a high-precision digital phase-locked loop.

[0052] In this embodiment, the digital phase-locked loop of the present invention is described in detail by taking the application of a digital TV decoding chip as an example. However, the present invention is equally applicable to other occasions that require a digital phase-locked loop. The code stream of digital TV programs is sent to the decoding chip at a frequency equivalent to, for example, 27MHz (the allowable error range is 27MHz±800Hz) (hereinafter referred to as the code stream frequency), and some modules inside the decoding chip need to be clocked at 27MHz (hereinafter referred to as local clock) to process the code stream, but as mentioned in the background technology section, the code stream frequen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More