RTOS power optimization method based on discrete Hopfield neural network

A technology of neural network algorithm and optimization method, which is applied in the field of RTOS power consumption optimization based on discrete Hopfield neural network, and can solve problems such as insufficient RTOS-Power division

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The idea of the present invention will be further described in detail below in conjunction with the accompanying drawings.

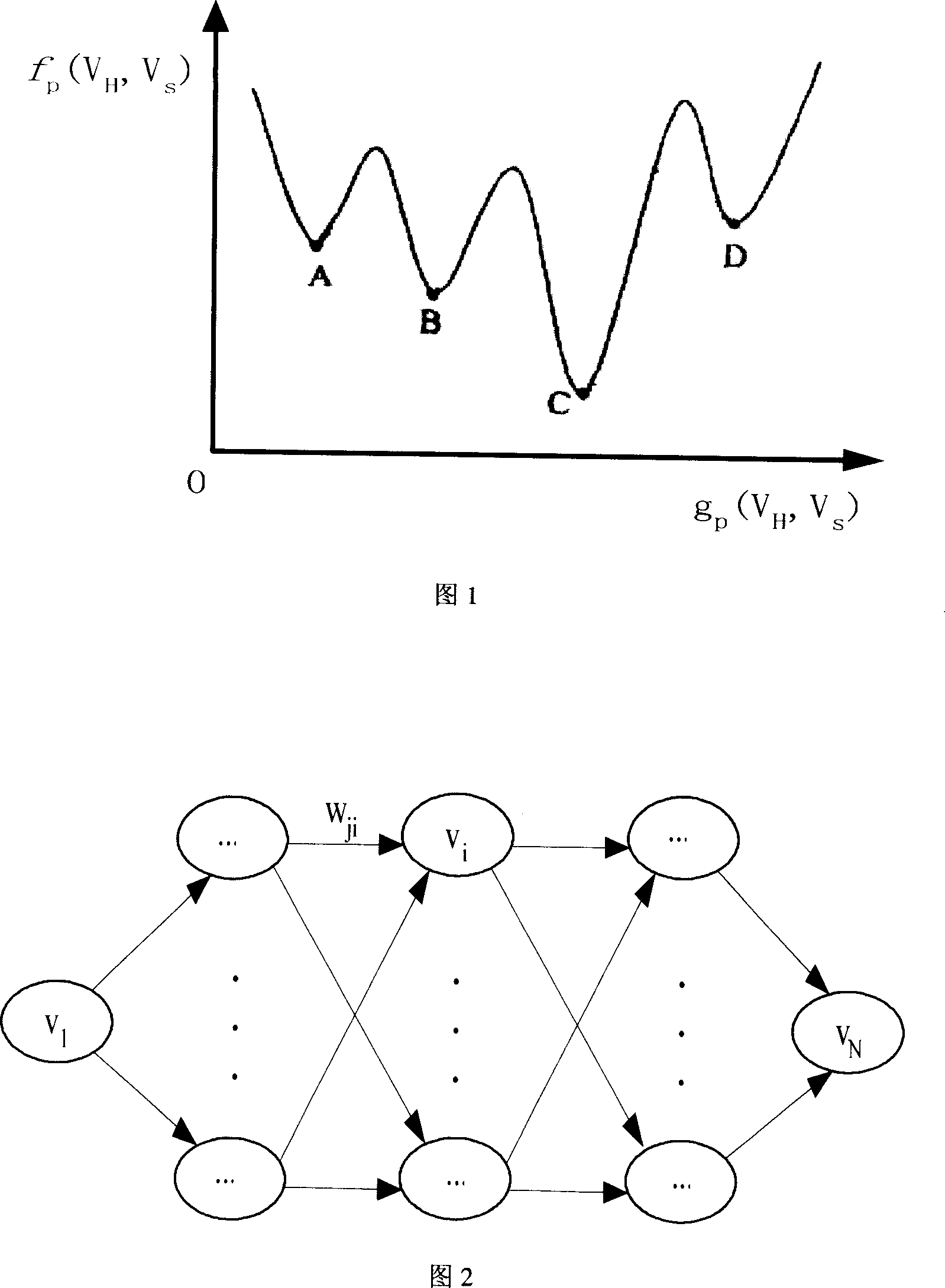

[0031] Fig. 1 is a schematic diagram of the RTOS-Power division problem model of the present invention

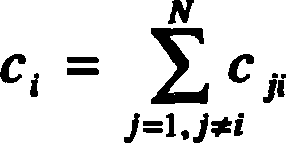

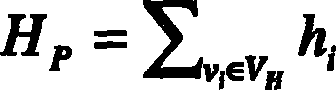

[0032] Definition 1 (k-way division). For a given G=(V,E), k-way partitioning is to find the set of clusters P={p 1 ,p 2 ,...,p k},satisfy:

[0033] p i ⊆ V , 1 ≤ i ≤ k ∪ i = 1 k p i = ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More