Semiconductor chip packaging process and its structure

A chip packaging structure and chip packaging technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of limited application fields and hollowed-out openings of semiconductor chips.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033]In order to further explain the technical means and effects that the present invention adopts to achieve the intended purpose of the invention, below in conjunction with the accompanying drawings and preferred embodiments, the semiconductor chip packaging process and its structure according to the present invention will be described according to its specific implementation, steps, and structure. , features and their effects are described in detail below.

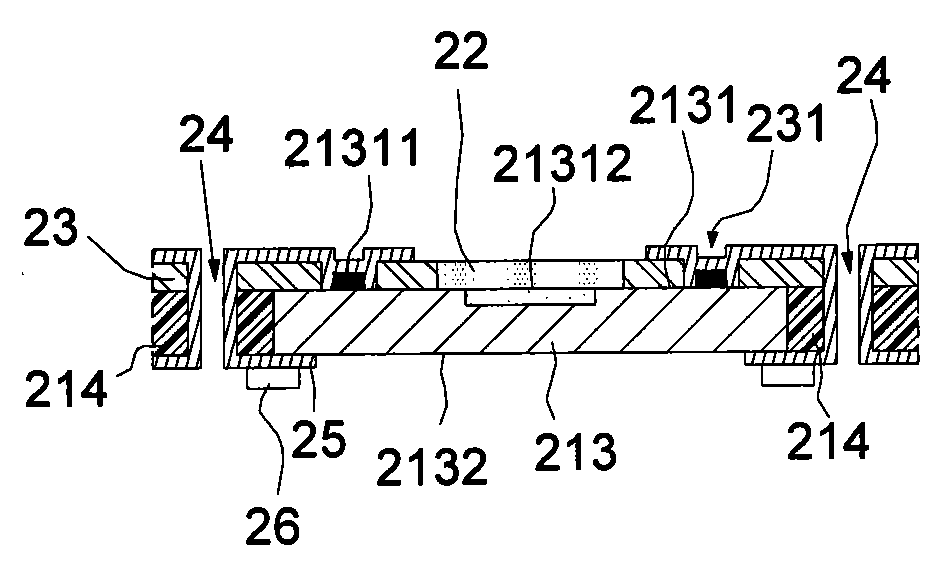

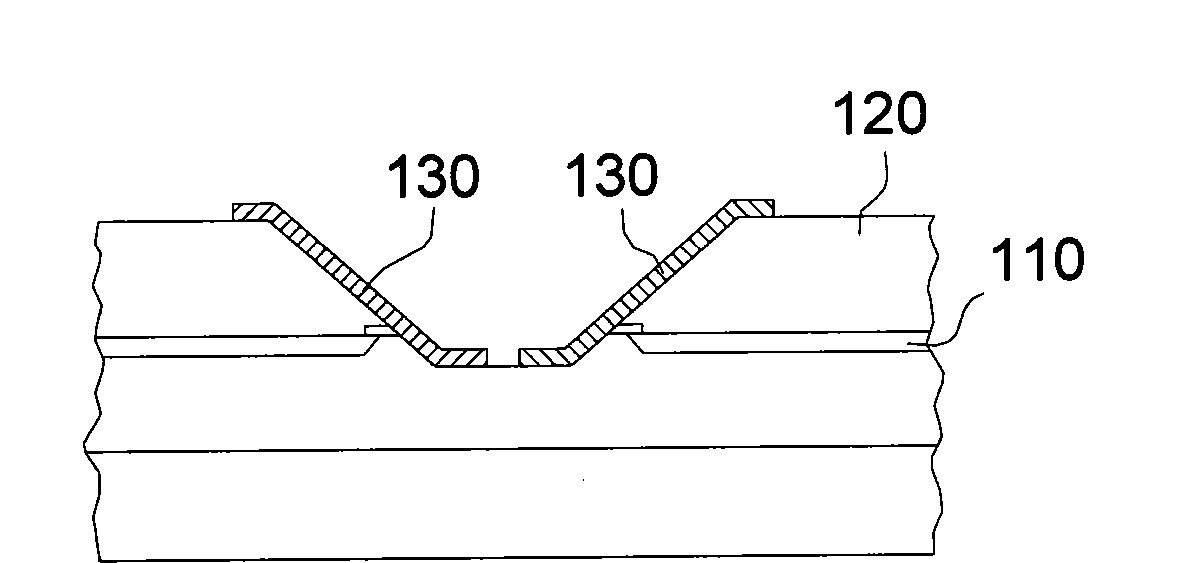

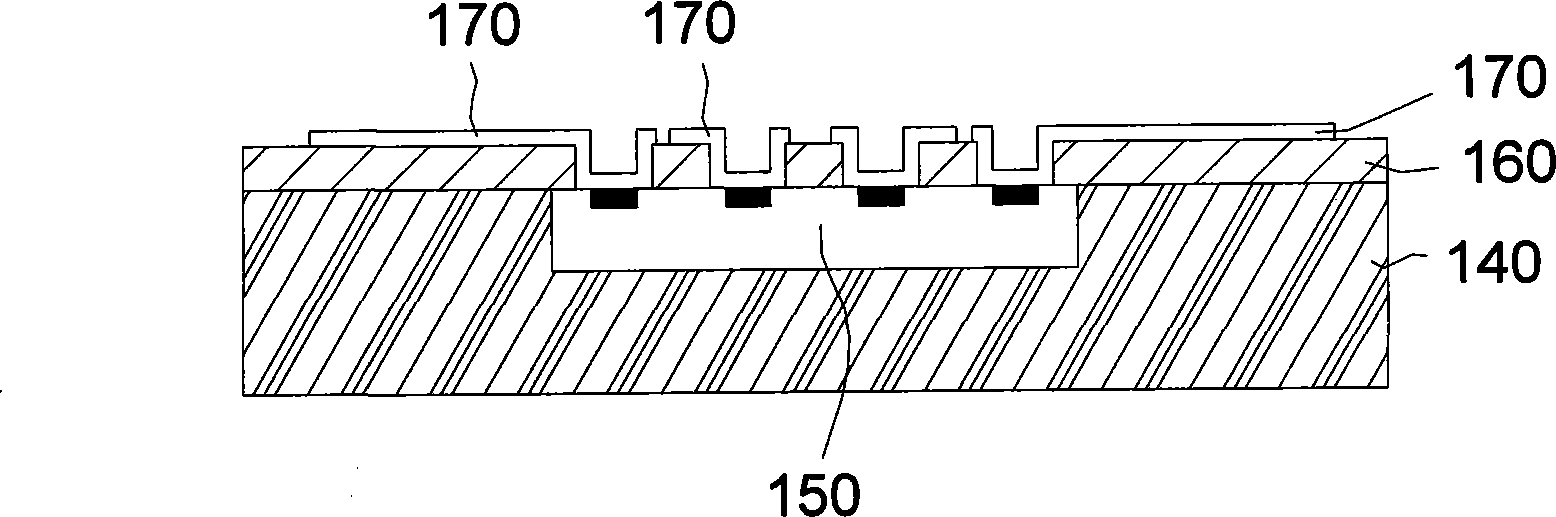

[0034] Please refer to FIG. 2A , FIG. 2B , FIG. 2C , FIG. 2D , FIG. 2E , FIG. 2F , FIG. 2G and FIG. 2H , which are schematic cross-sectional views of the manufacturing process of the first embodiment of the present invention. The manufacturing steps include: providing a substrate 21 in advance, the substrate 21 has an upper surface 211 and a lower surface 212, and the substrate 21 includes a plurality of image sensing chips 213 and an insulating colloid 214 surrounding the image sensing chips 213, Each image sensing ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More