Two-level SiC MOSFET H bridge main circuit topology with low parasitic oscillation

A low parasitic, main circuit technology, applied in the field of converters, can solve the problems that are not conducive to the application of SiC MOSFETs, increase the difficulty and time of circuit development, and achieve the effects of low cost, reduced loss, and reduced switching loss.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

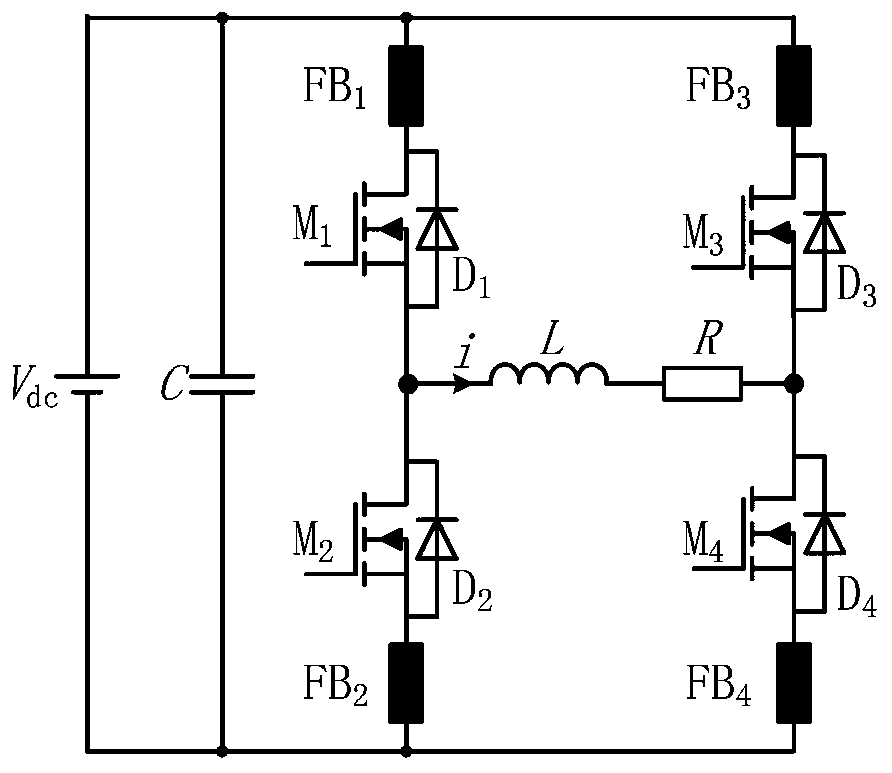

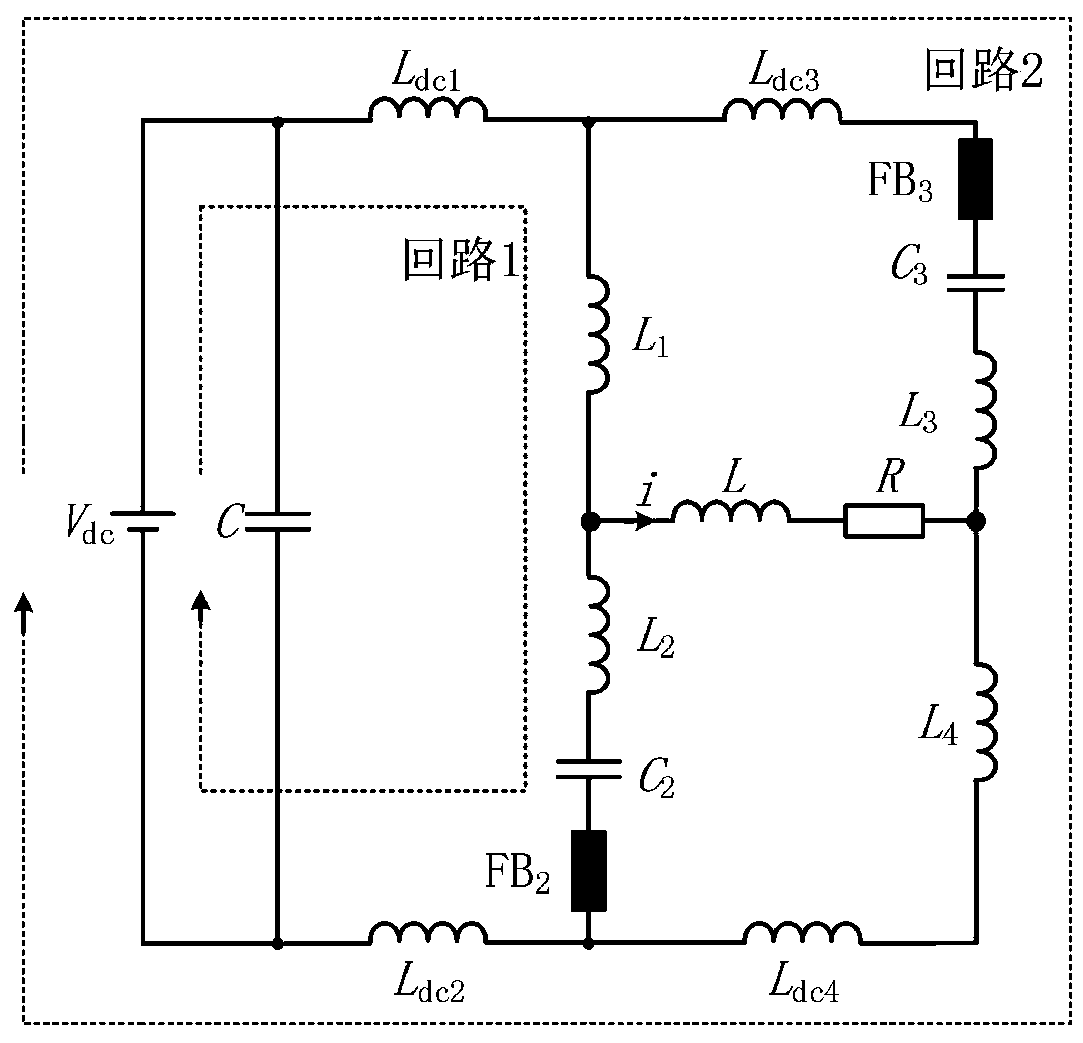

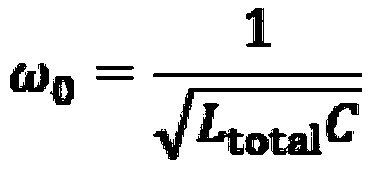

[0028] see Figure 1-2 , the present invention provides a technical solution: a low parasitic oscillation two-level SiC MOSFET H-bridge main circuit topology, characterized in that: the topology is composed of the following components: DC power supply V dc , DC bus capacitor C, load inductance L, load resistance R, 4 ferrite beads, respectively the first ferrite bead FB 1 , the second ferrite bead FB 2 , the third ferrite bead FB 3 , the fourth ferrite bead...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More