Backing store buffer for the register save engine of a stacked register file

A back-up memory and back-up storage technology, applied in the direction of protecting storage content from loss, instruments, machine execution devices, etc., can solve the problems of low application of expensive hardware, increase of physical register file area and complexity cost, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

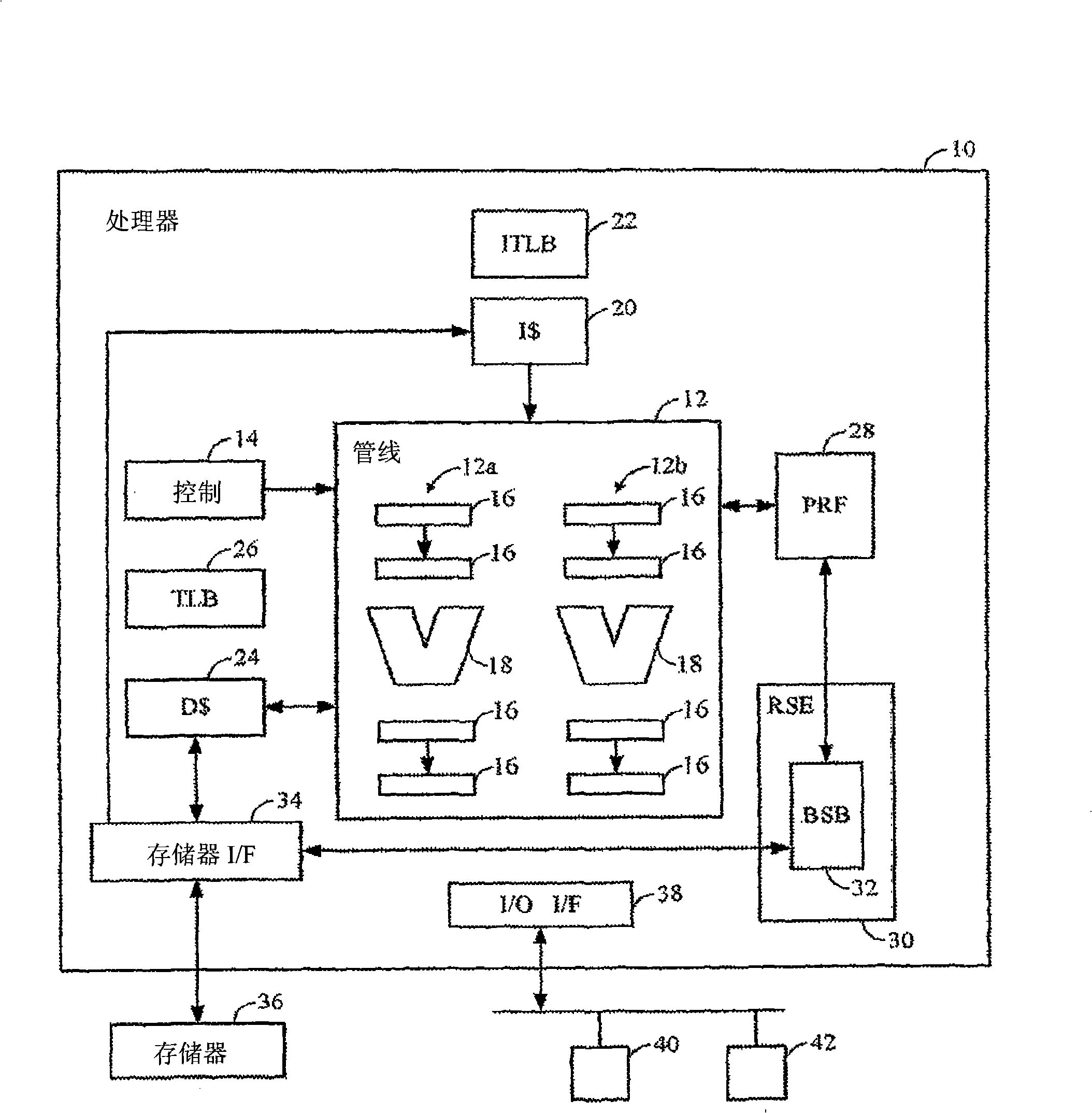

[0020] figure 2 A functional block diagram of the processor 10 is shown. Processor 10 executes instructions in instruction execution pipeline 12 according to control logic 14 . Pipeline 12 may be a superscalar design with multiple parallel pipelines (eg, 12a and 12b). Each pipeline 12a, 12b includes various registers or latches 16 organized into pipeline stages, and one or more arithmetic logic units (ALUs) 18 . The pipelines 12a, 12b fetch instructions from an instruction cache (I-cache or I$) 20 where memory addressing and permissions are managed by an instruction-side translation lookaside buffer (ITLB) 22 .

[0021]Data is accessed from a data cache (D-cache or D$) 24 where memory addressing and permissions are managed by a translation lookaside buffer (TLB) 26 . In various embodiments, ITLB 22 may include a replica of portions of TLB 26 . Alternatively, ITLB 22 and TLB 26 may be integrated. Similarly, in various embodiments of processor 10, I-cache 20 and D-cache 24 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More