Patents

Literature

41 results about "Stack register" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A stack register is a computer central processor register whose purpose is to keep track of a call stack. On an accumulator-based architecture machine, this may be a dedicated register such as SP on an Intel x86 machine. On a general register machine, it may be a register which is reserved by convention, such as on the PDP-11 or RISC machines. Some designs such as the Data General Eclipse had no dedicated register, but used a reserved hardware memory address for this function.

Extending a register file utilizing stack and queue techniques

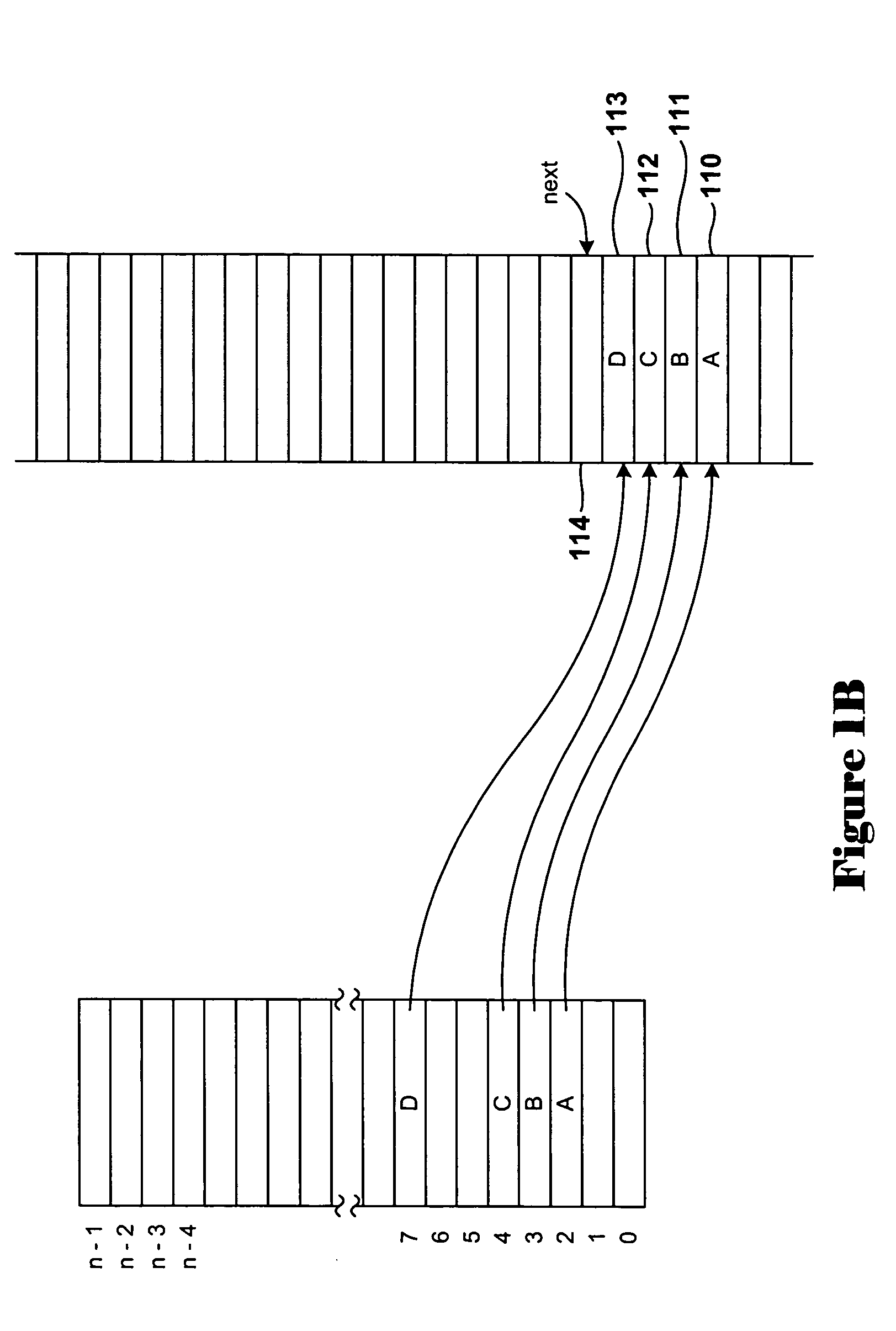

ActiveUS20040003211A1Digital computer detailsSpecific program execution arrangementsSoftwareRegister file

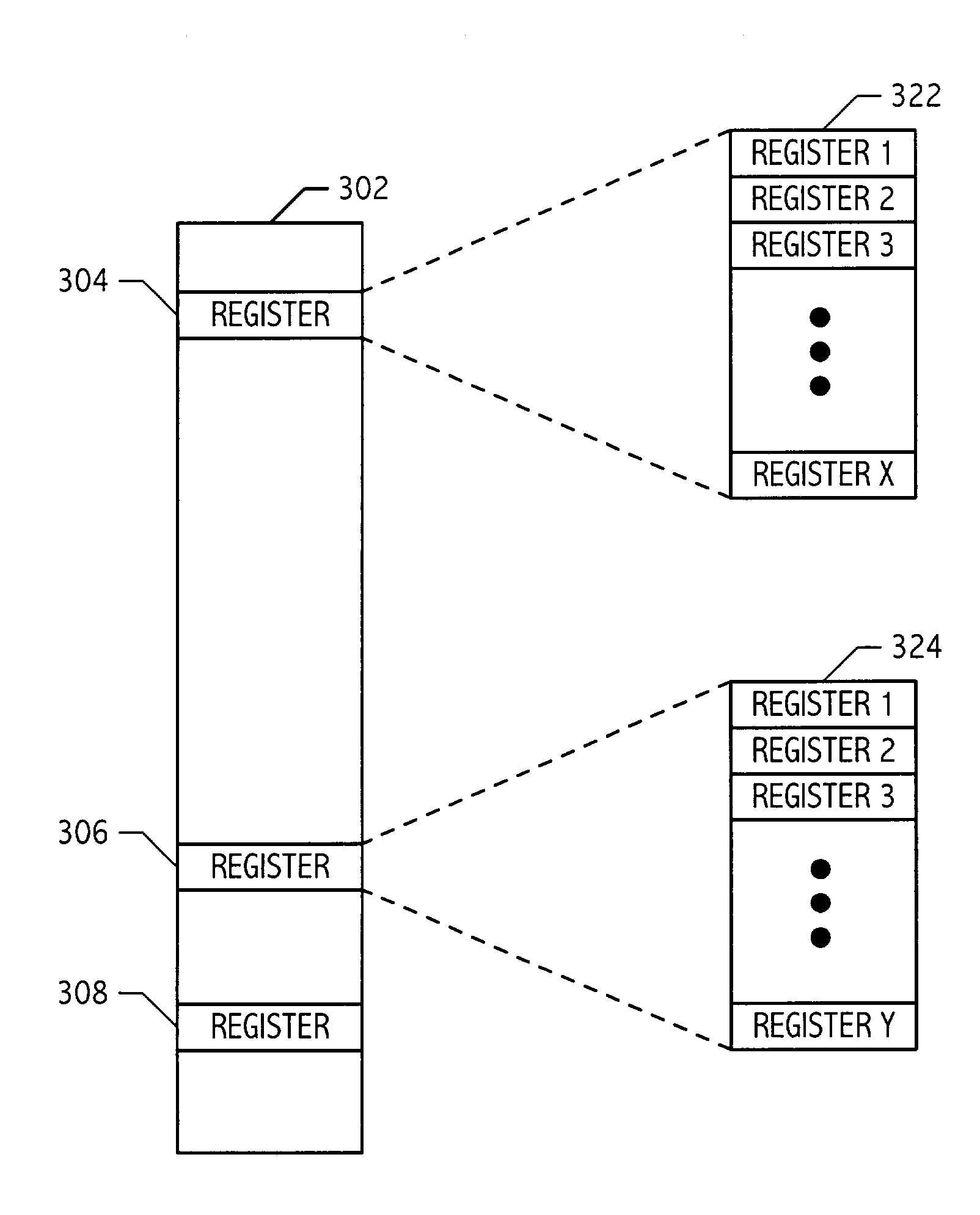

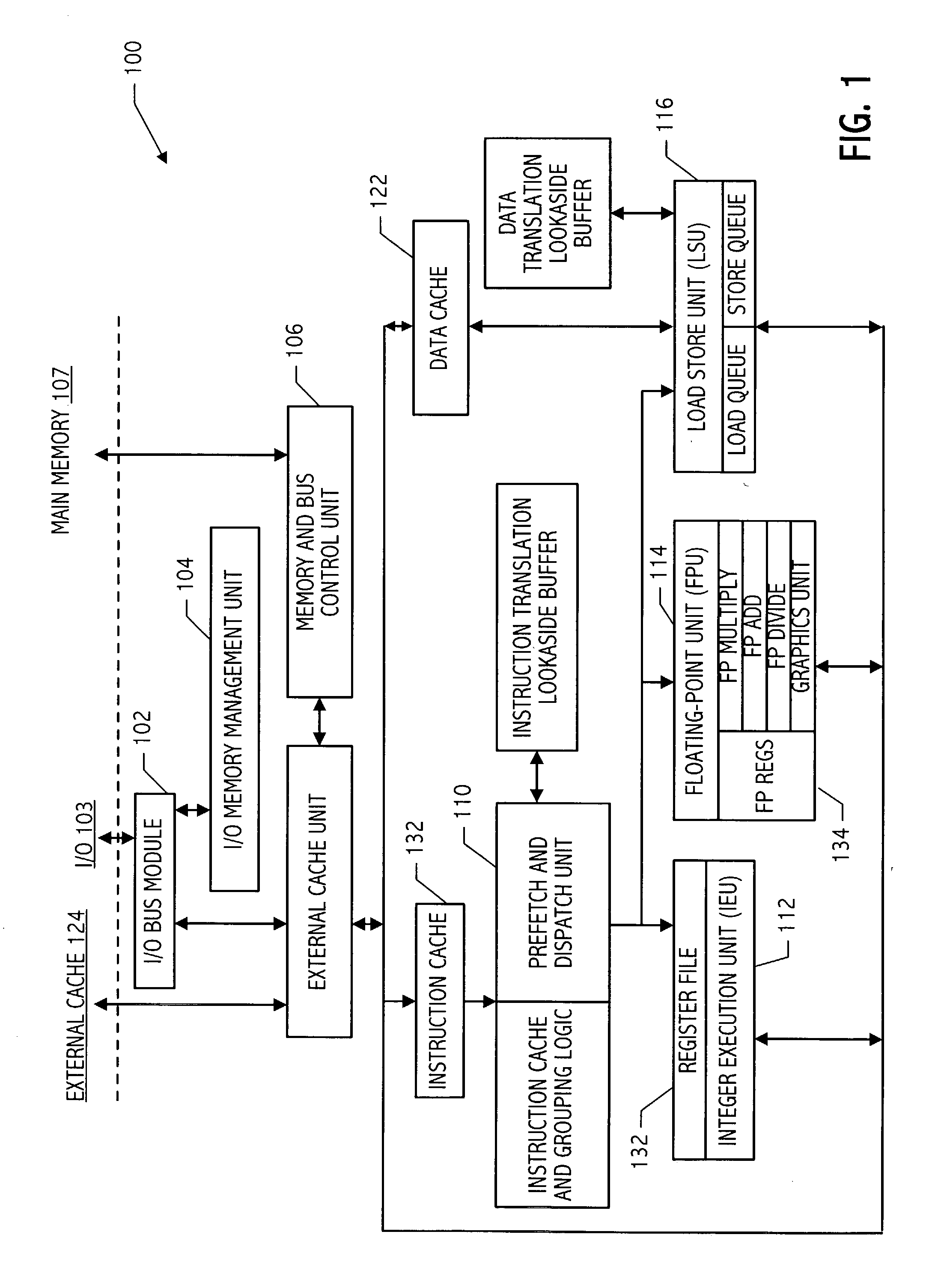

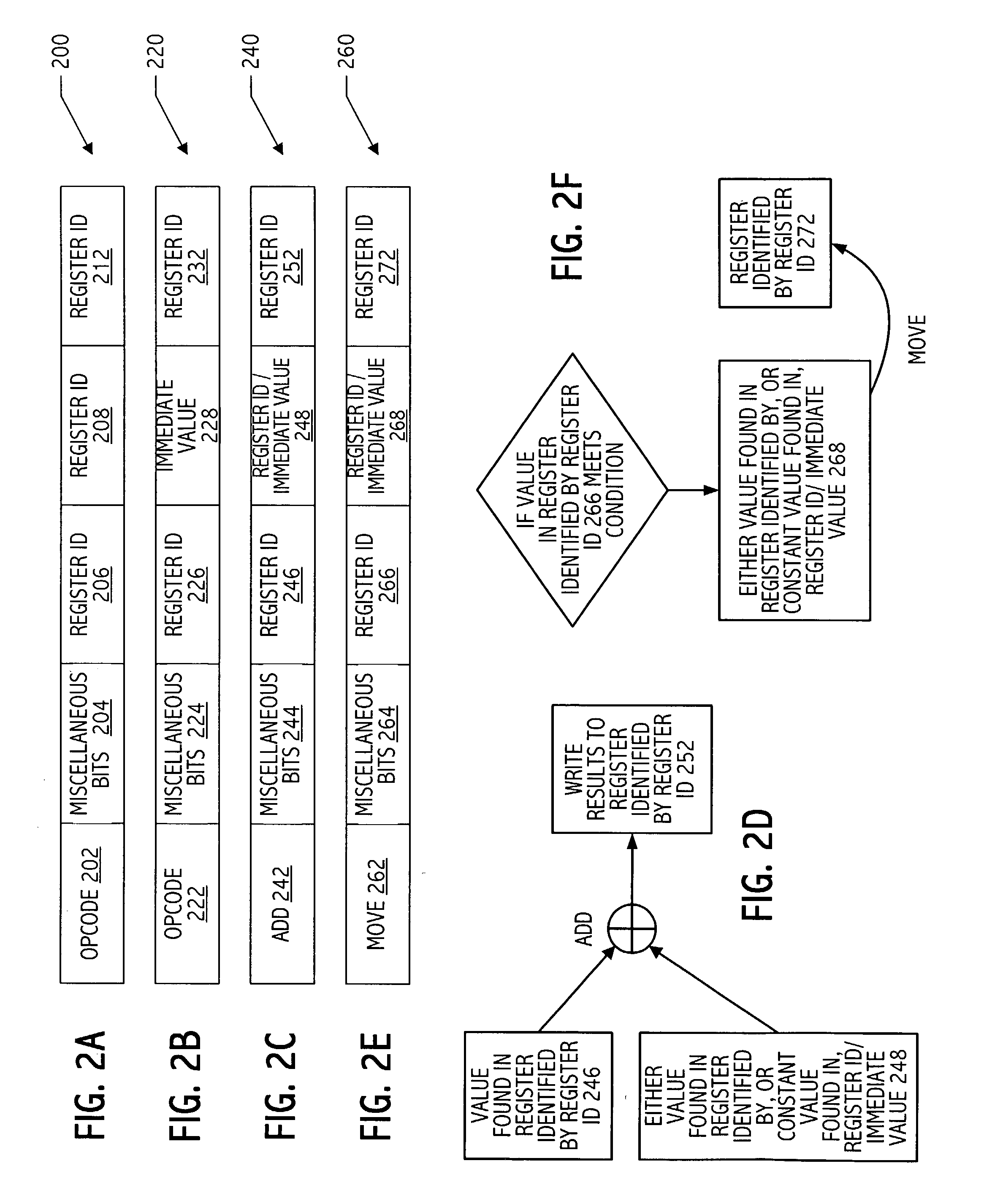

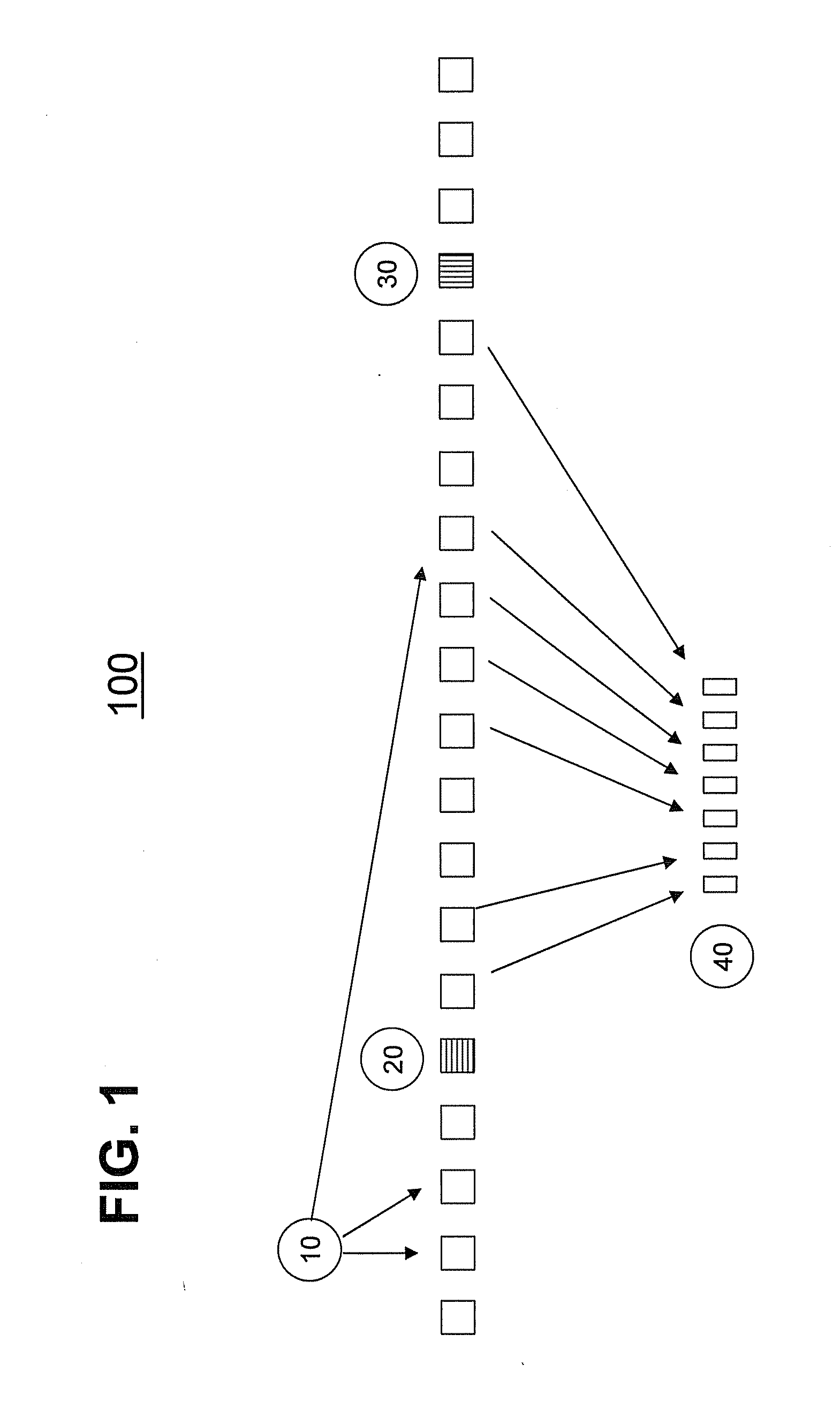

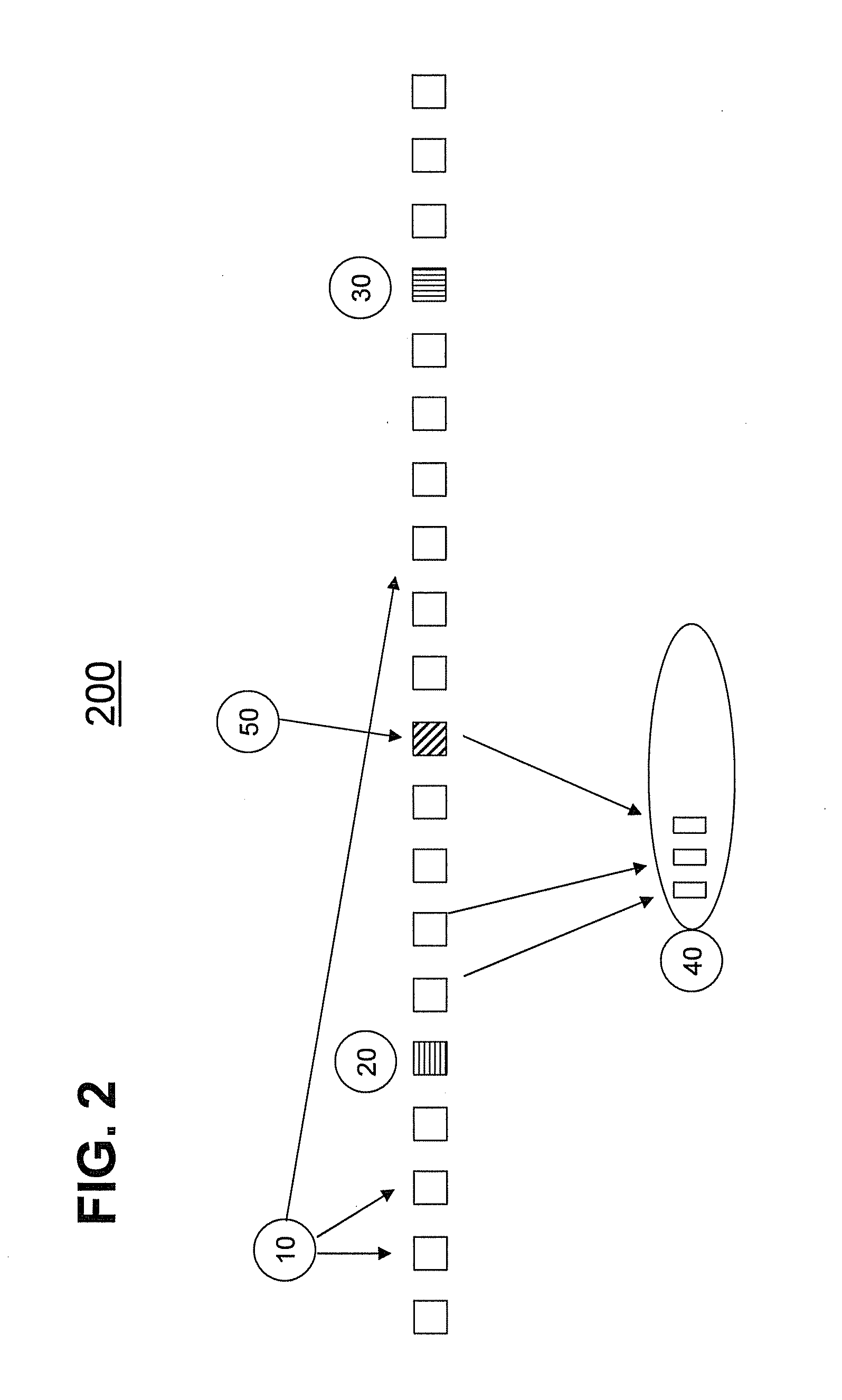

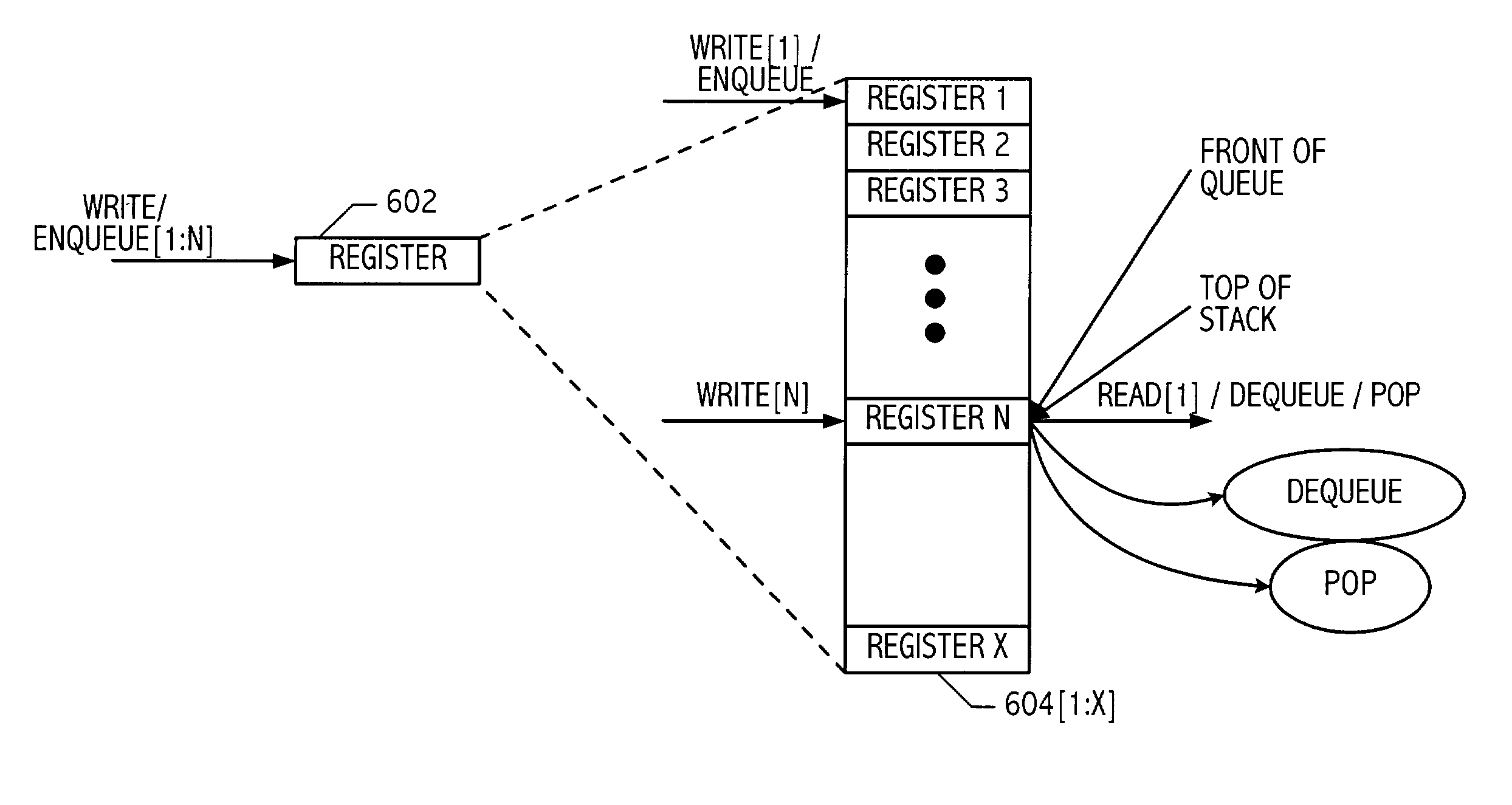

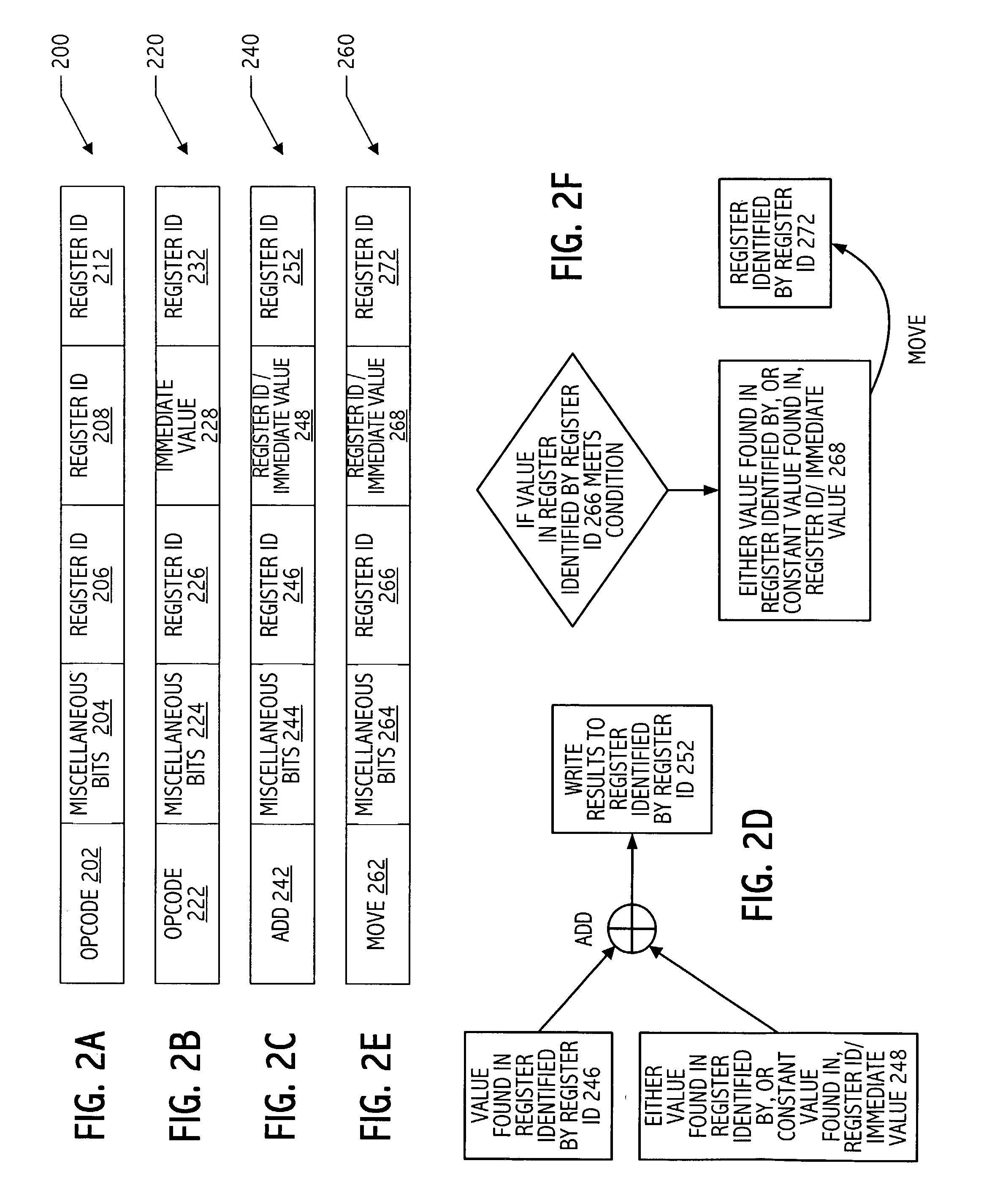

In a set of registers, each individually addressable by register operations using a corresponding register identification, at least one register of the set of registers is an extended register having multiple storage locations. Values stored in the multiple storage locations are accessed, for example, according to the order in which they have been stored. Less than all of the multiple storage locations are accessible by a register operation at a given time. Older versions of software that do not recognize extended registers identify the extended register as having only one storage location. An extended register can be, for example, a stack register, a queue register, or a mixed register and values stored in the multiple storage locations are read and stored according to the characteristics of the register.

Owner:ORACLE INT CORP

Method and apparatus for diagnostic recording using transactional memory

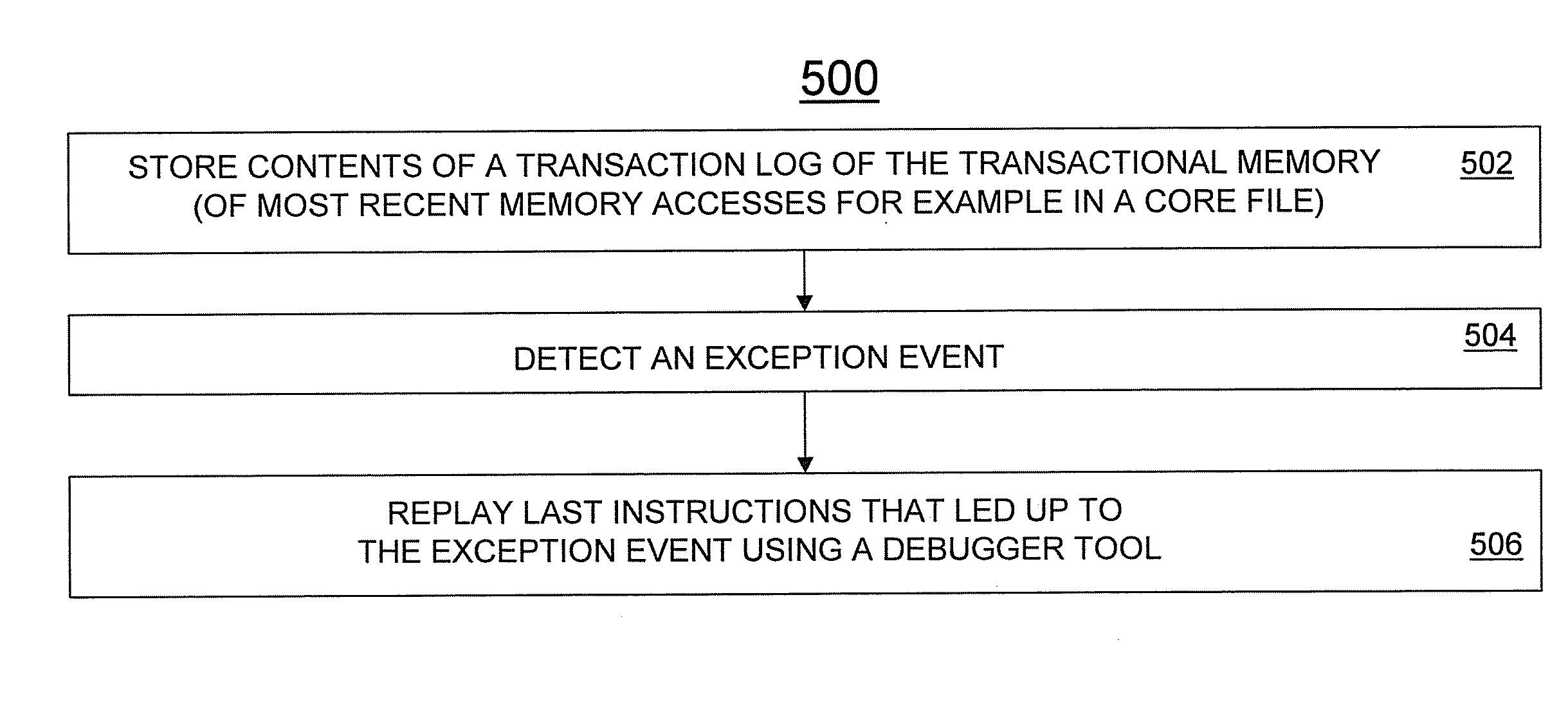

A method (500) or a diagnostic recording device (400) having transactional memory and a processor coupled to the transactional memory can store (502) contents of a transaction log (40) of the transactional memory, detect (504) an exception event, and replay (506) last instructions that led up to the exception event using a debugger tool (80). The transactional memory can be hardware or software based transactional memory. The processor can also store the transaction log by storing the contents of the transaction log in a core file (302) which can include a stack (60), a register dump (70), a memory dump (75), and the transactional log. The debugger tool can be used to load up the core file, an executable file (95), and a library (90) to enable the diagnostic recording device to retrace transactions occurring at the diagnostic recording device up to the exception event.

Owner:IBM CORP

Method and system for generating stacked register dumps from backing-store memory

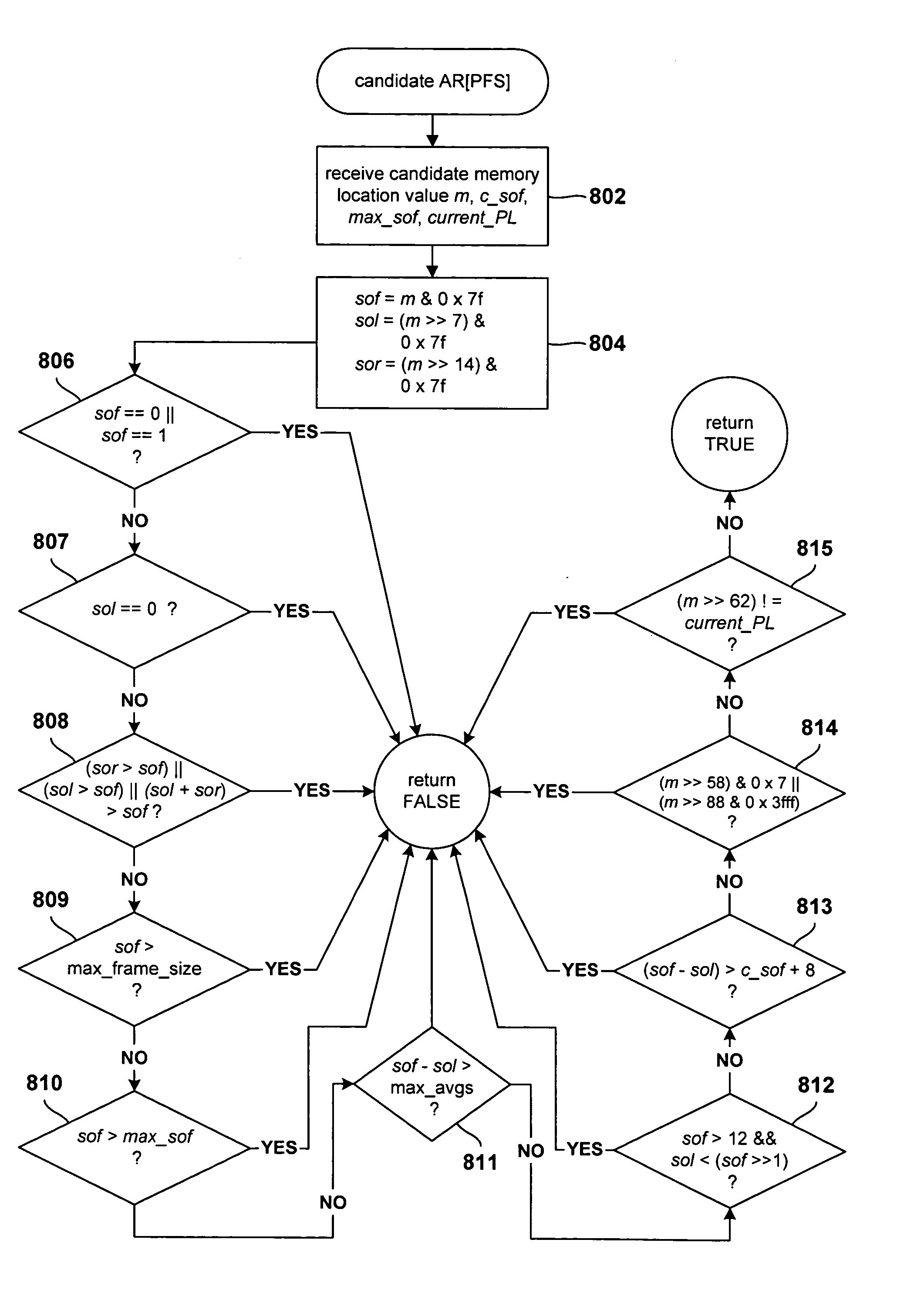

In various embodiments of the present invention, debugging and program-behavior-analysis software can reconstruct register-based processor states for nested routine calls from the backing-store memory employed by a modern processor, and by processors of similar architectures, to automatically spill and restore register values via a register stack engine. Sufficient information resides in the backing-store memory to reconstruct the stack frames for all nested routines. However, reconstructing the stack frames from the backing-store memory depends on identifying stored register vales in the backing-store memory containing saved values of the previous-frame-marker application register. Various embodiments of the present invention employ a set of heuristic tests to evaluate stored values in the backing-store memory in order to identify those values corresponding to the stored contents of the previous-frame-marker application register.

Owner:VALTRUS INNOVATIONS LTD +1

Apparatus for exchanging two stack registers

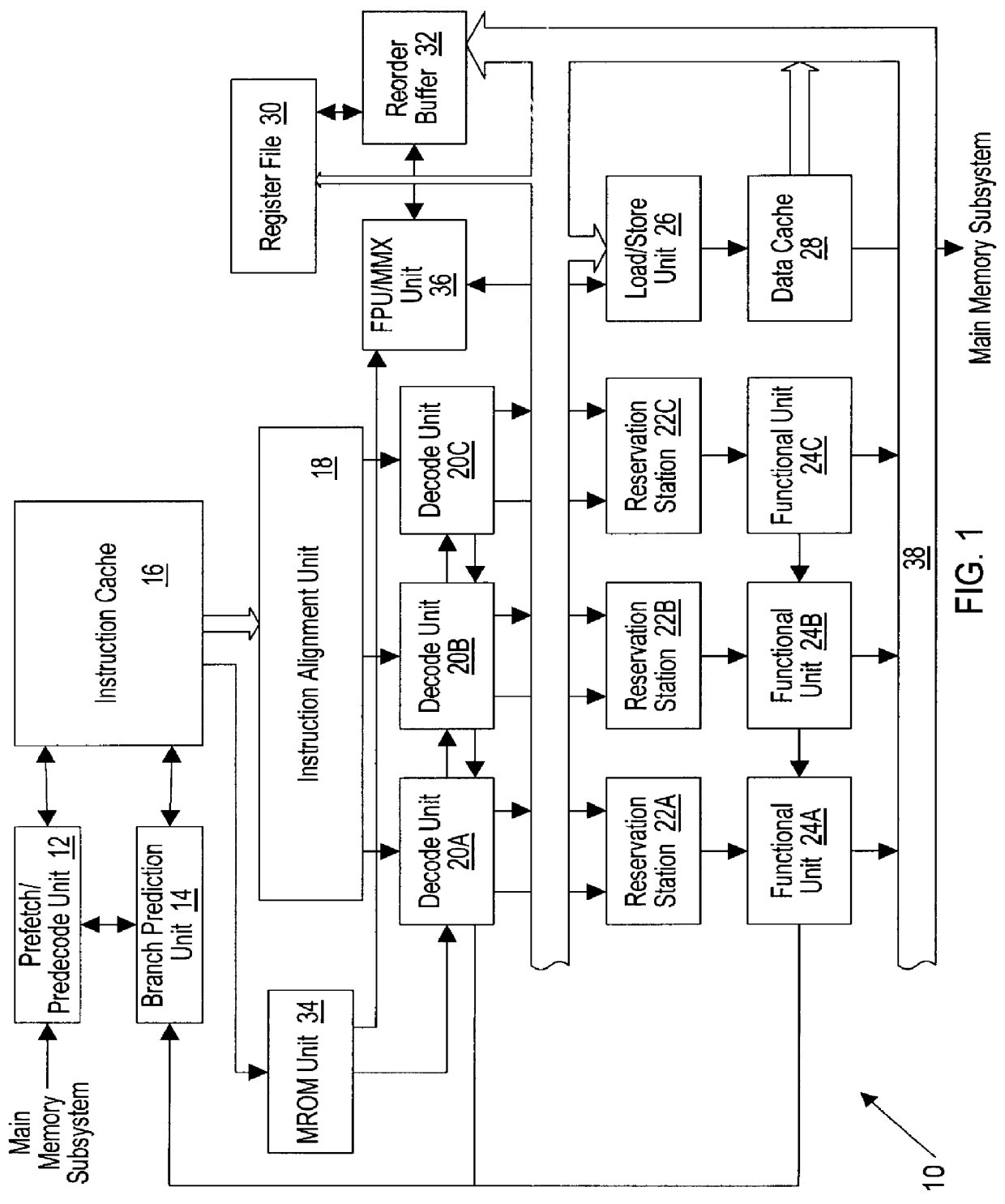

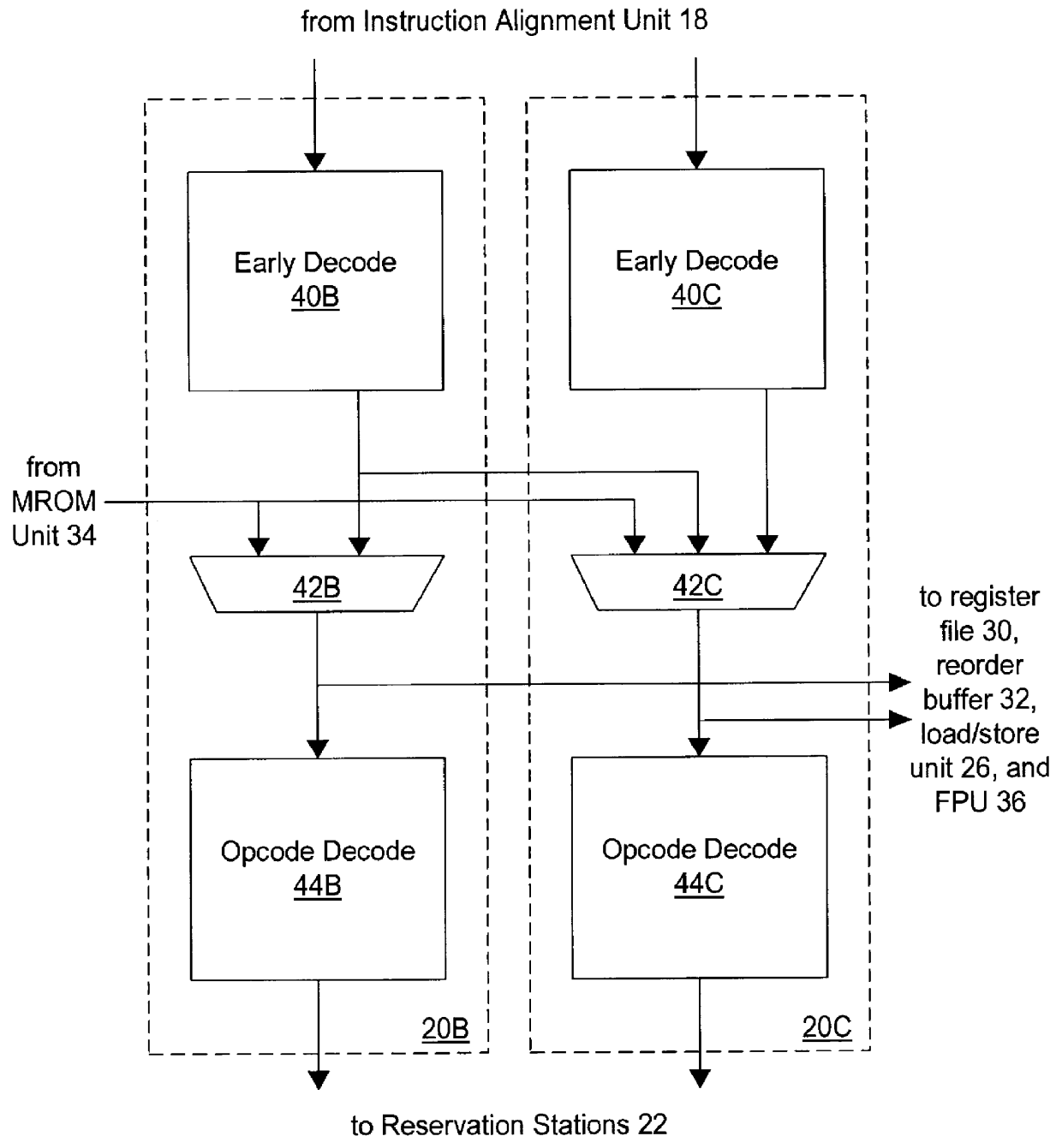

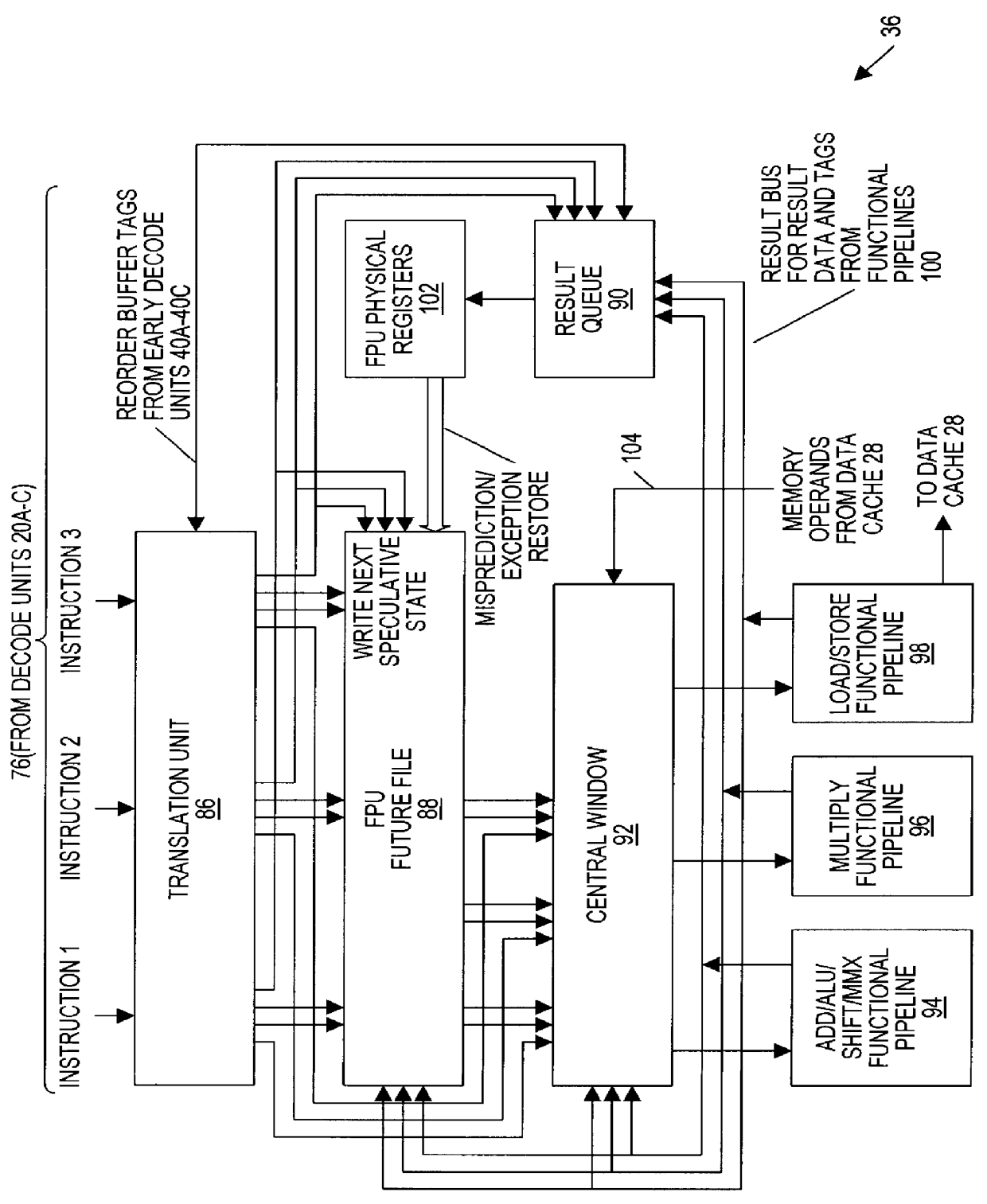

InactiveUS6112018AImprove performanceSpeed memory access timeDigital computer detailsConcurrent instruction executionWindow selectionFloating-point unit

A floating point unit capable of executing multiple instructions in a single clock cycle using a central window and a register map is disclosed. The floating point unit comprises: a plurality of translation units, a future file, a central window, a plurality of functional units, a result queue, and a plurality of physical registers. The floating point unit receives speculative instructions, decodes them, and then stores them in the central window. Speculative top of stack values are generated for each instruction during decoding. Top of stack relative operands are computed to physical registers using a register map. Register stack exchange operations are performed during decoding. Instructions are then stored in the central window, which selects the oldest stored instructions to be issued to each functional pipeline and issues them. Conversion units convert the instruction's operands to an internal format, and normalization units detect and normalize any denormal operands. Finally, the functional pipelines execute the instructions.

Owner:ADVANCED MICRO DEVICES INC

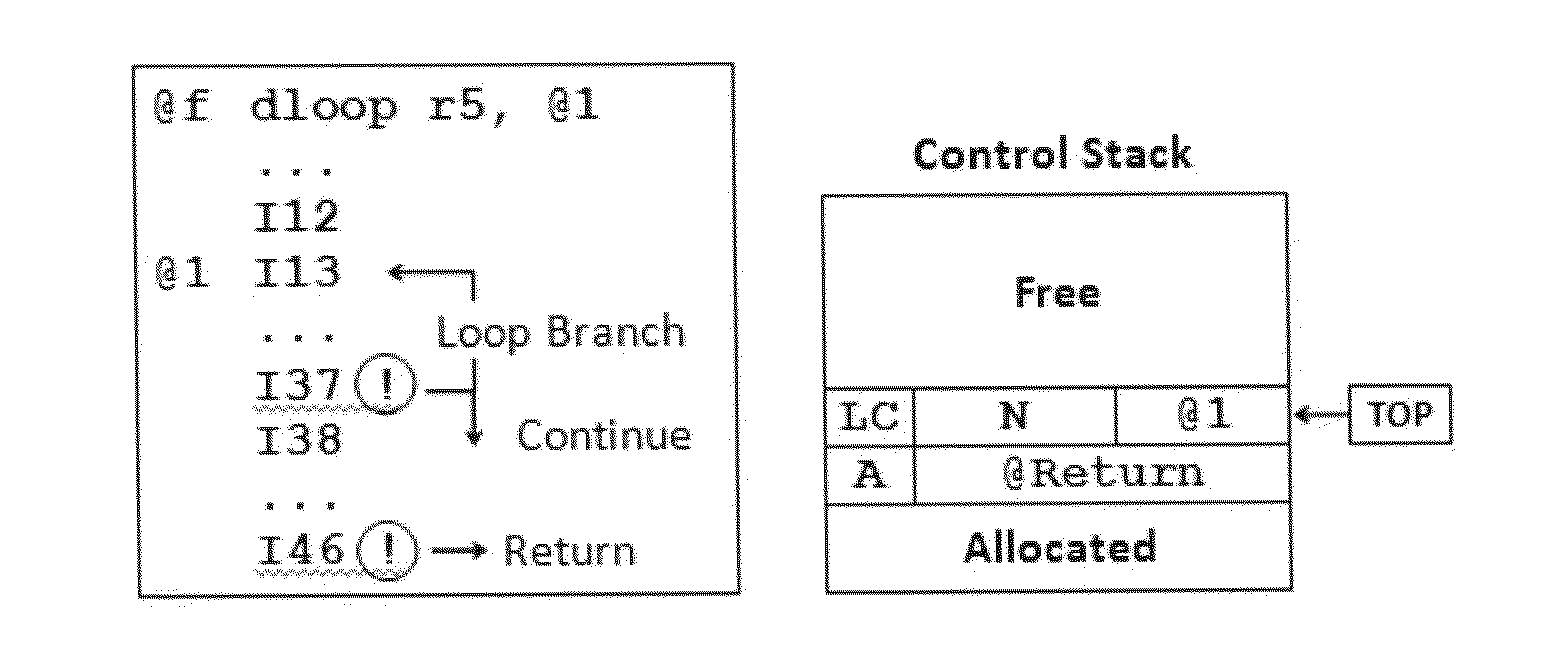

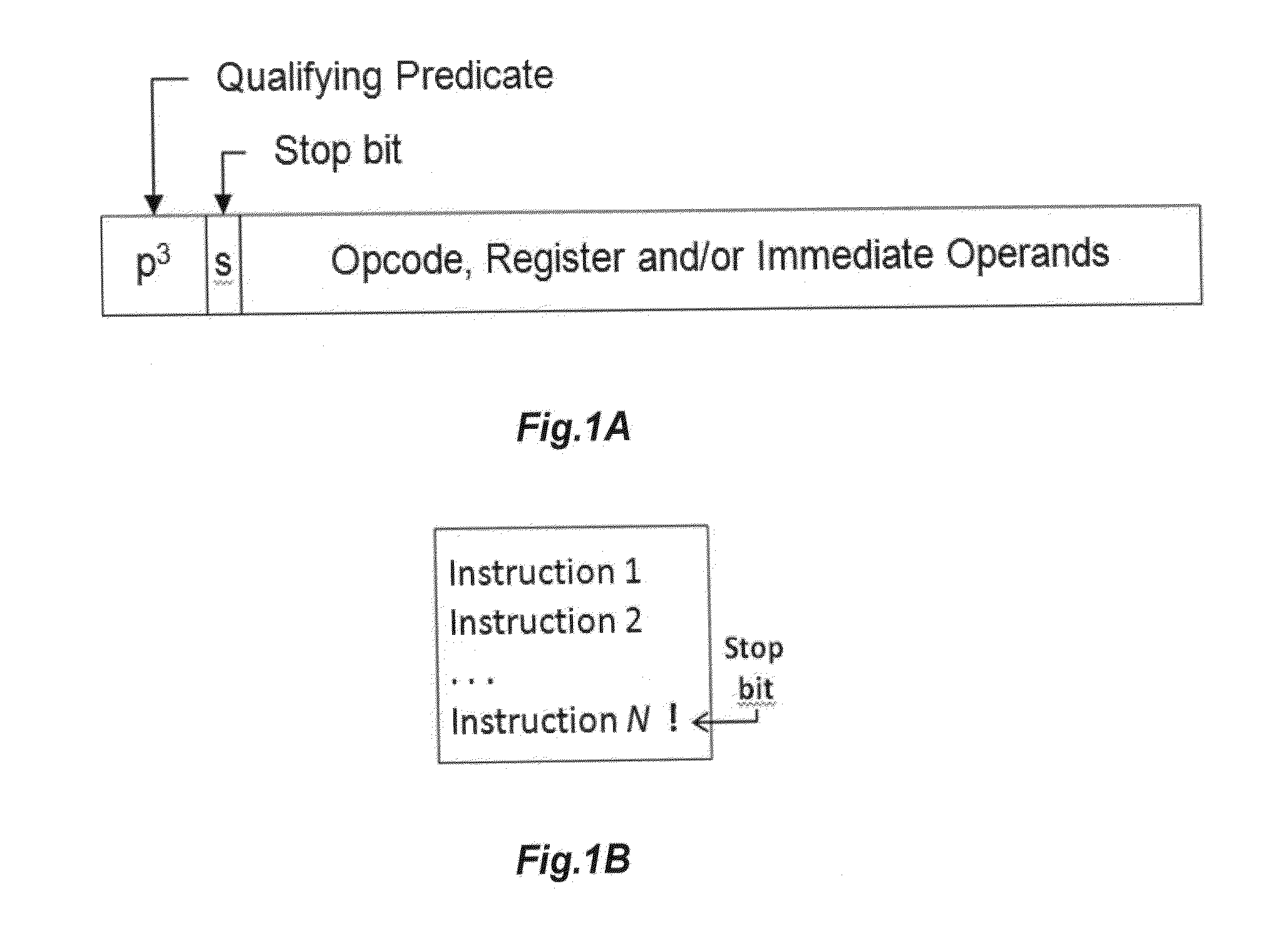

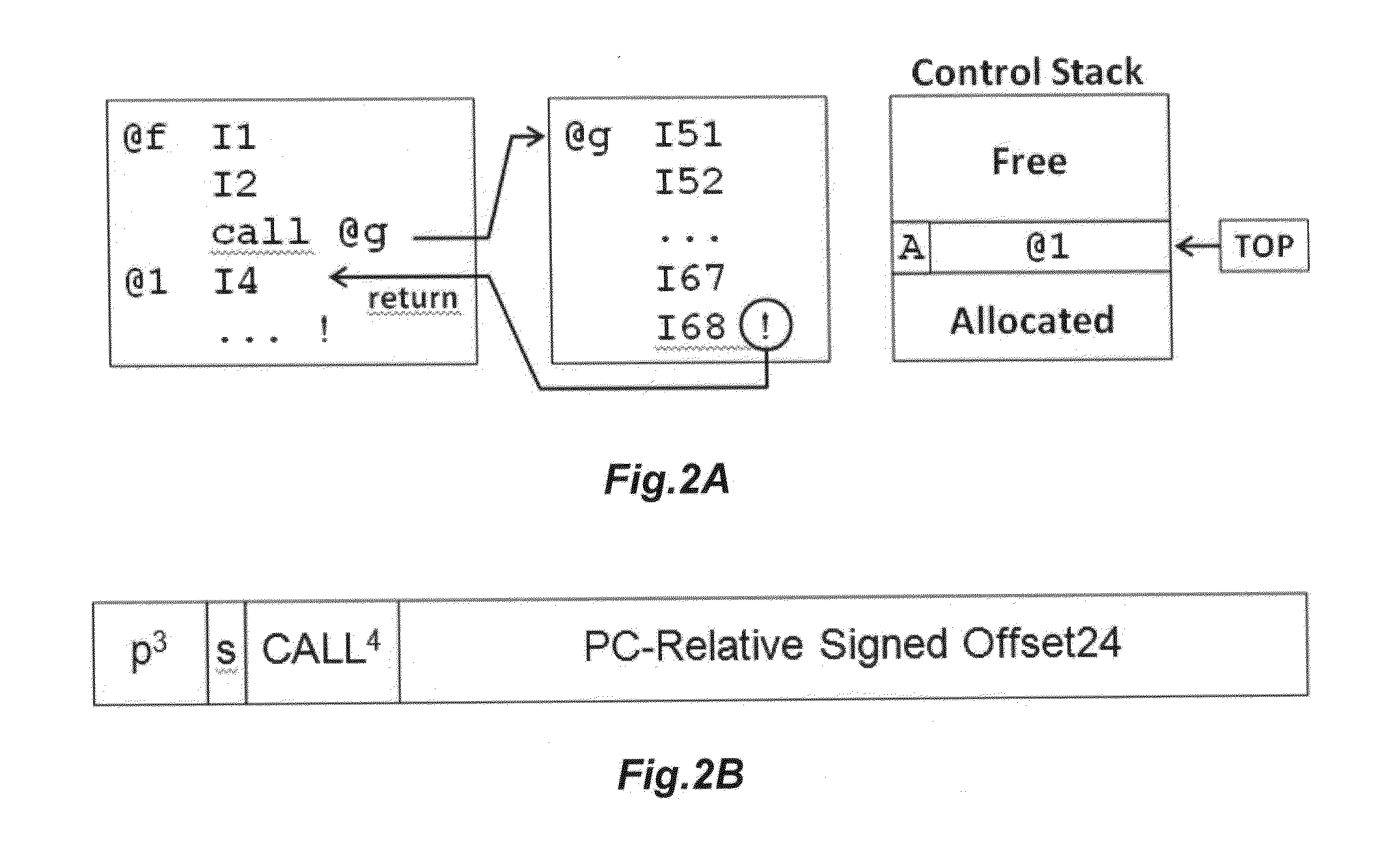

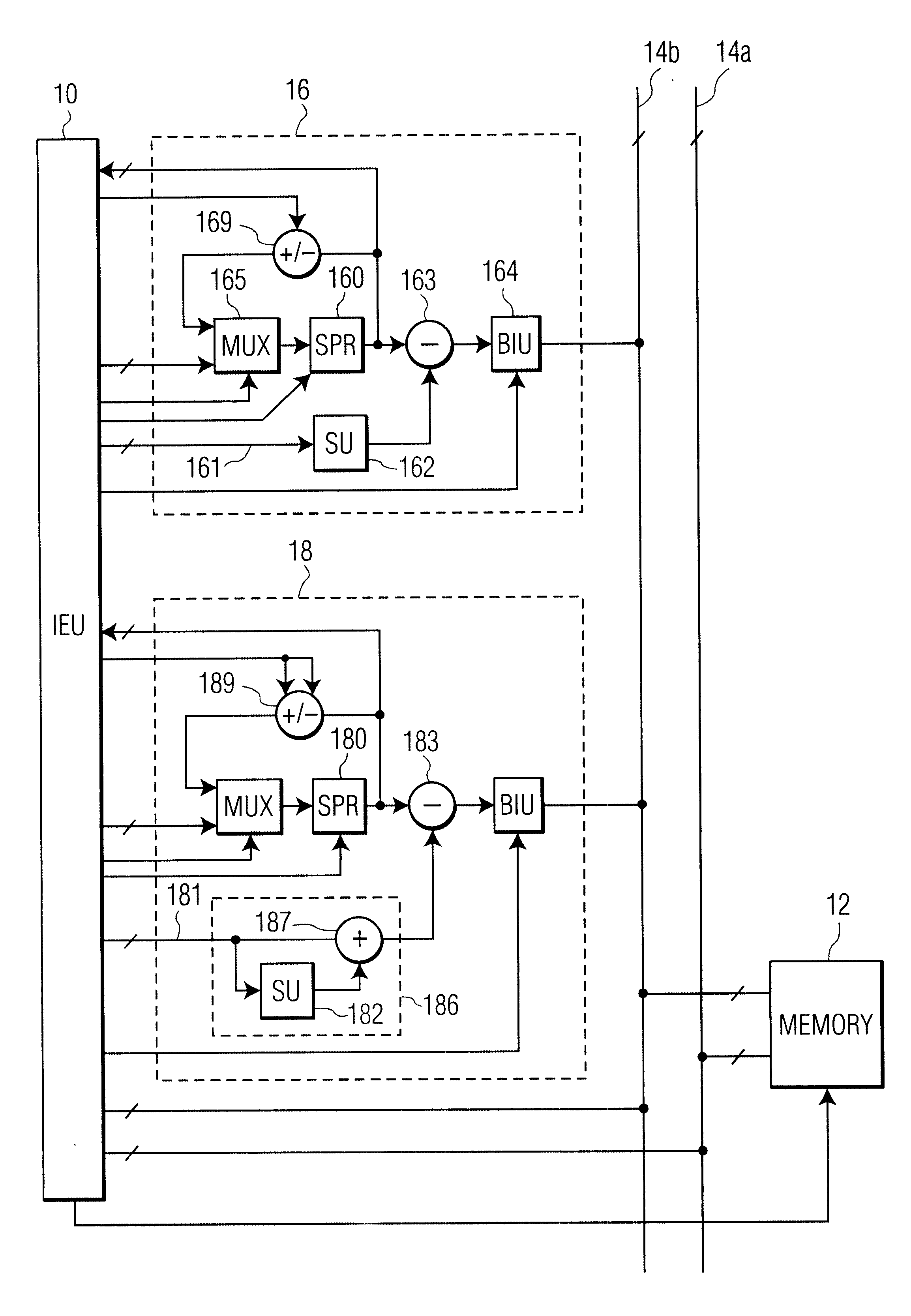

Stop bits and predication for enhanced instruction stream control

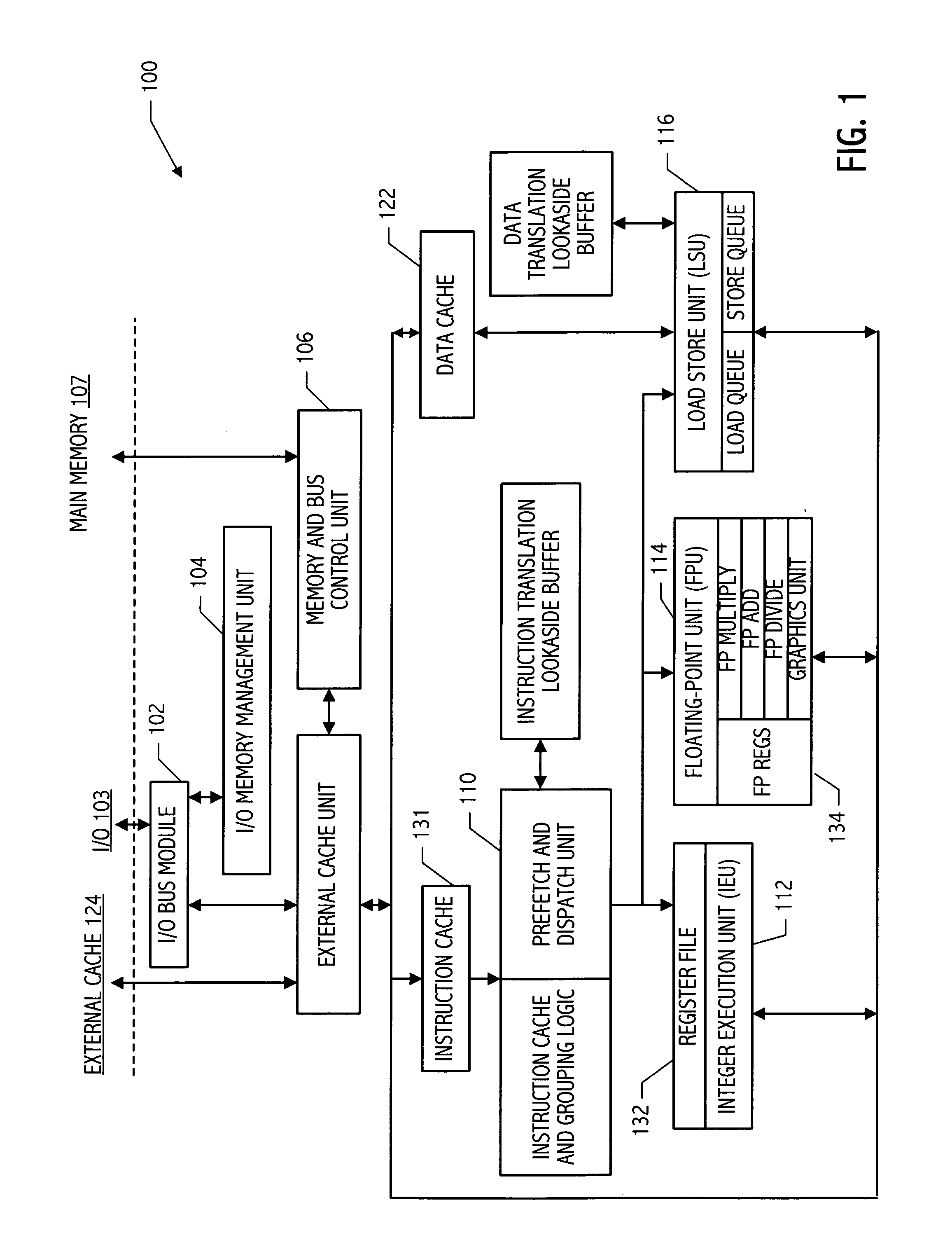

InactiveUS20150227373A1Reduces the conditional branch instructionsConditional code generationInstruction analysisOperandTerm memory

A microprocessor including an instruction set architecture includes: a decode and fetch control; a instruction cache; a data cache; a control stack; and an instruction set including a stop bit; a qualifying predicate; an opcode, a register and / or an immediate operand. A data processing method includes: fetch instructions encoded with a stop bit from an instruction set architecture of the microprocessor; popping, a top address off a control stack and transfer control back to a caller function, to an indirect function, or to a top of a loop block when the stop bit indicate a function return, an indirect function call, or a loop branch; save control stack registers on a backing store after the stop bit indicate the call or loop branch function when a number of used control stack registers exceeds a HI threshold; overflow a control stack signal when the number of the used and the saved entries exceeds the backing store size; allocate more memory to increase a size of the backing store from a data cache or terminate the execution; restoring, the control stack registers from the data cache when the number of the used control stack registers drops below a LO threshold.

Owner:KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS

Stack oriented data processing device

InactiveUS6557093B2Reduce the amount of memoryResource allocationRegister arrangementsParallel computingStack register

The data processing device maintains two stacks. The length of the basic unit of information is different for each stack. Pops and pushes cause a change in the stack pointer which differs dependent on which stack is used. Instructions refer to different locations on the stack as registers defined by an offset of a number of basic units relative to the top of stack. In an embodiment a reference to registers is normally interpreted as a reference to one of a set of registers (including the top of stack register) without push or pop, but a reference to one register is interpreted as a reference to top of stack including a push or pop.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

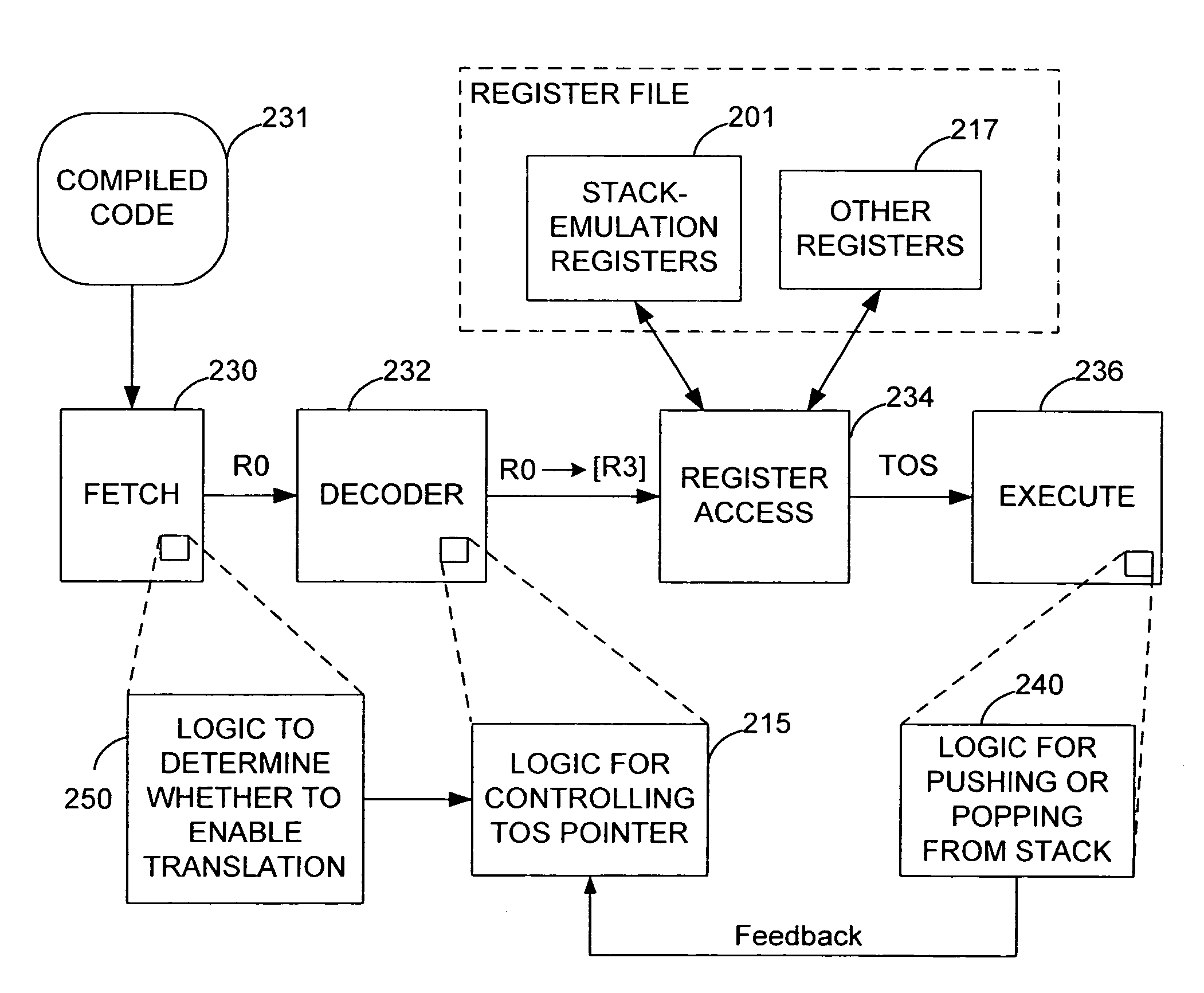

Apparatus and method for managing registers in a processor to emulate a portion of stack

ActiveUS20050235093A1Memory adressing/allocation/relocationDigital computer detailsParallel computingStack register

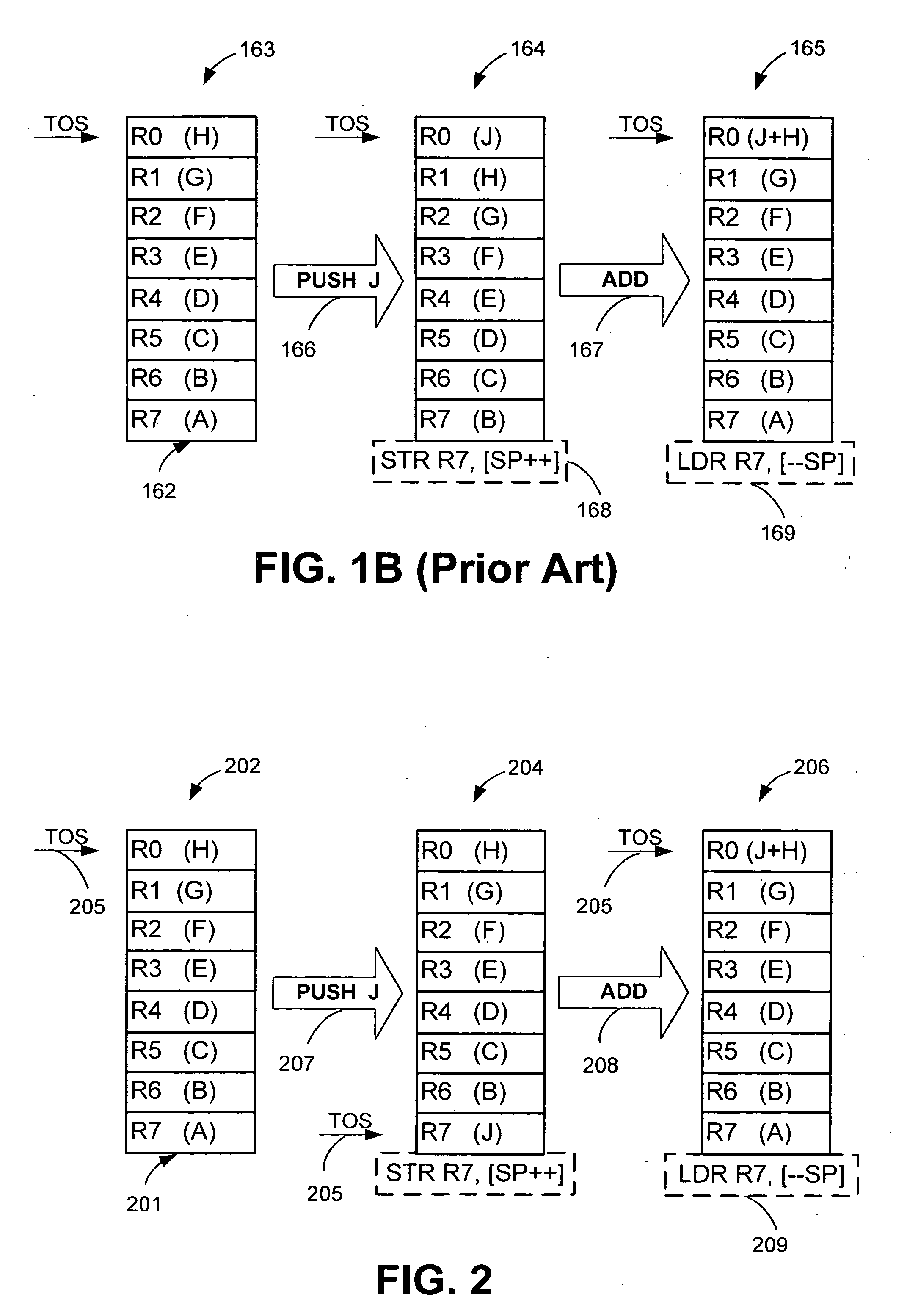

The present invention is generally directed to method and apparatus for emulating a portion of a stack. Certain embodiments of the invention manage a plurality of processor registers to store the top portion of the stack. Data is managed in these registers by managing a pointer that points to a current top-of-stack register. As data is pushed or popped from the stack, the top-of-stack point is incremented or decremented accordingly.

Owner:VIA TECH INC

Apparatus and method for checking floating point stack overflow on non-CISC processor

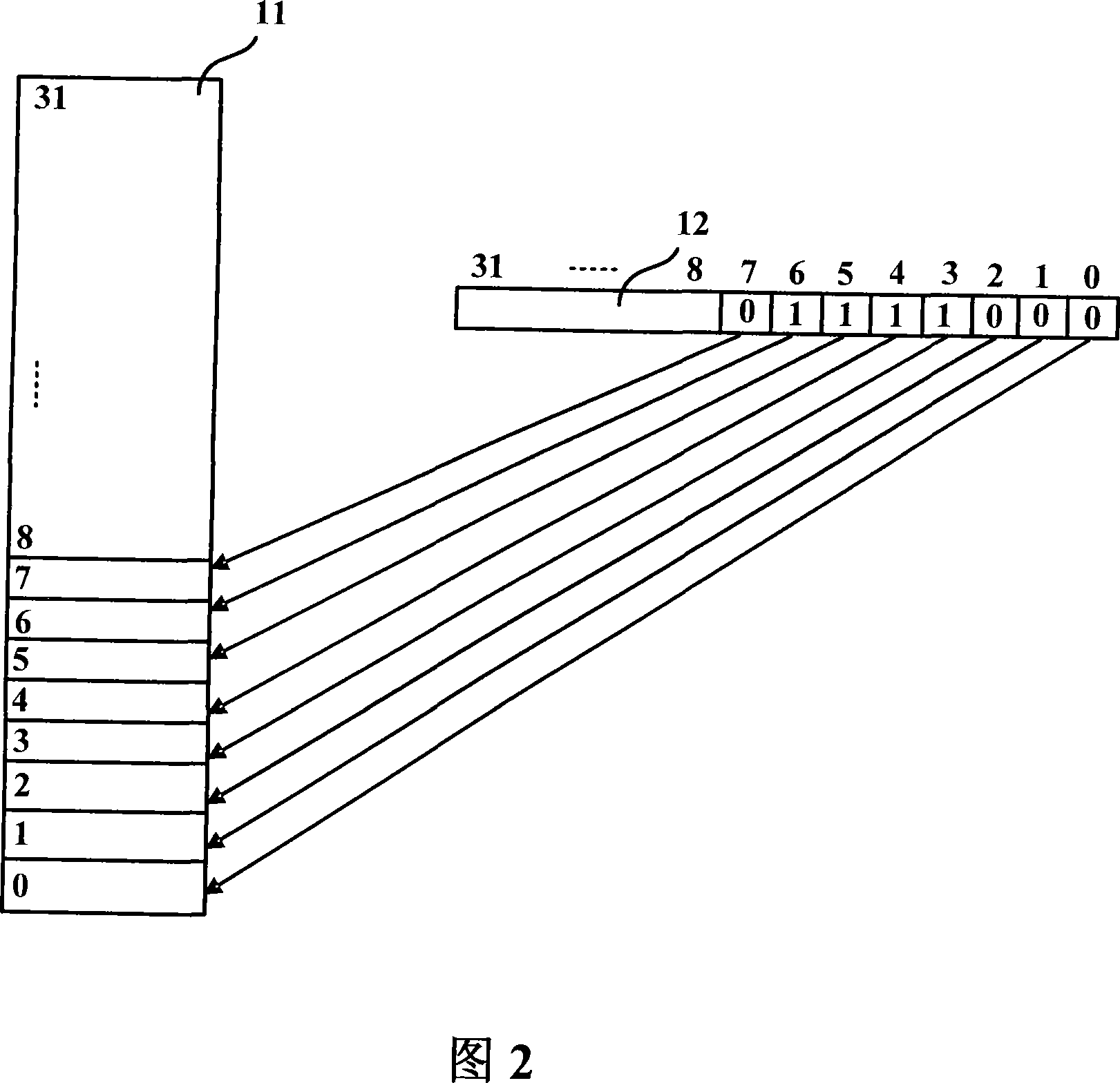

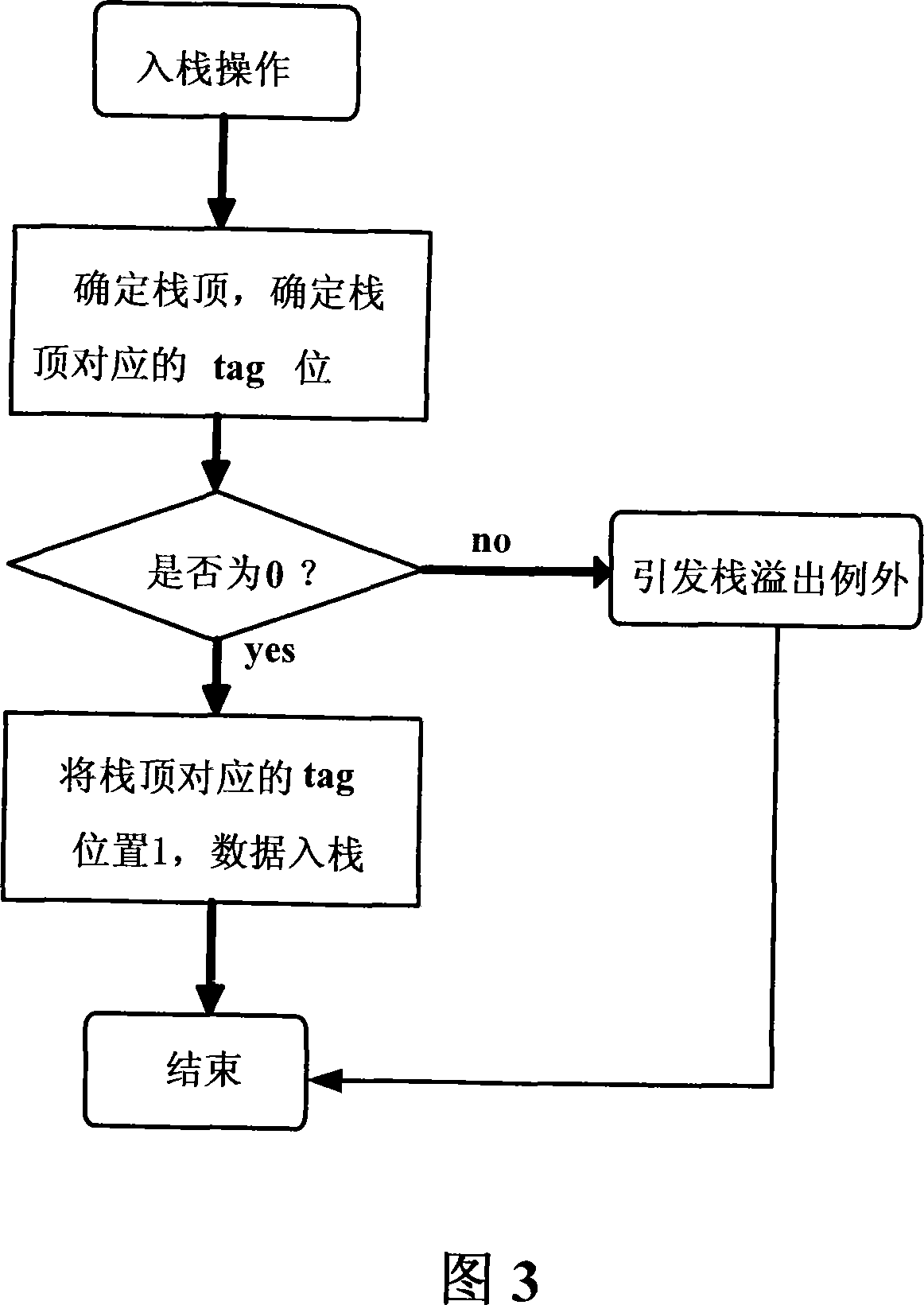

ActiveCN101158891AImprove compatibilityFacilitate binary translation workDigital data processing detailsFloating pointWorkload

The invention discloses a device and a method conducting floating-point stack overflow check on a non-complex instruction set computer processor. The device comprises a floating-point register stack, which comprises a plurality of stack registers, which can conduct floating-point calculation; an overflow check register used for stack overflow exceptional check when conducting floating-point access, which comprises a plurality of bits corresponding to the stack registers, and all the bits separately indicate the states of corresponding stack registers; a stack overflow judge module, which is used for checking the stack registers in the specified floating-point register stack, conducting operation to the overflow check register in accordance with the values of the stack registers, and carry out the floating-point stack overflow check. The invention can greatly reduce the workload and improve efficiency of a virtual machine.

Owner:LOONGSON TECH CORP

Method for dynamically acquiring process descriptors in client Linux by adopting VMM (Virtual Machine Monitor)

InactiveCN101872312AOvercome integrityOvercoming Performance DrawbacksMemory adressing/allocation/relocationSoftware simulation/interpretation/emulationOperational systemGNU/Linux

The invention relates to a method for efficiently and dynamically acquiring process descriptors of a client Linux operation system according to requirements by adopting a VMM (Virtual Machine Monitor). On the premise of not changing the client operation system, the process descriptors of the client operation system in the current process can be dynamically acquired by a stack pointer register in the VMM, and members of a tasks linked table of the process descriptor are then traversed so as to directly and dynamically acquire all process descriptors in the client Linux operation system according to requirements. By fully utilizing Linux core characteristics, the operation of searching a client page table in the acquisition process and the operation of acquiring the process descriptor in the current client process by the stack pointer register at a time are eliminated, thereby reducing the influence on the VMM performance to minimum.

Owner:张纪胜

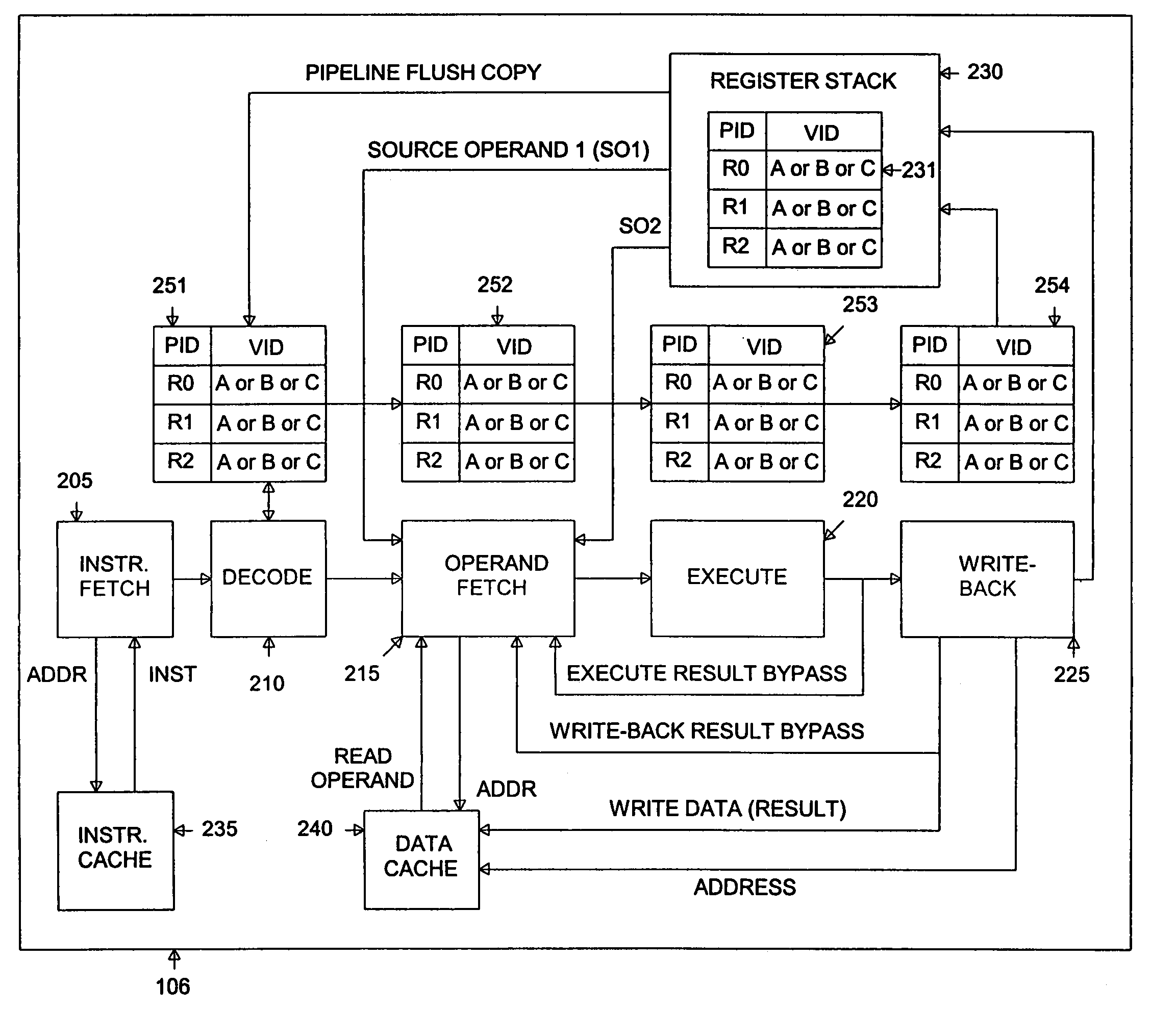

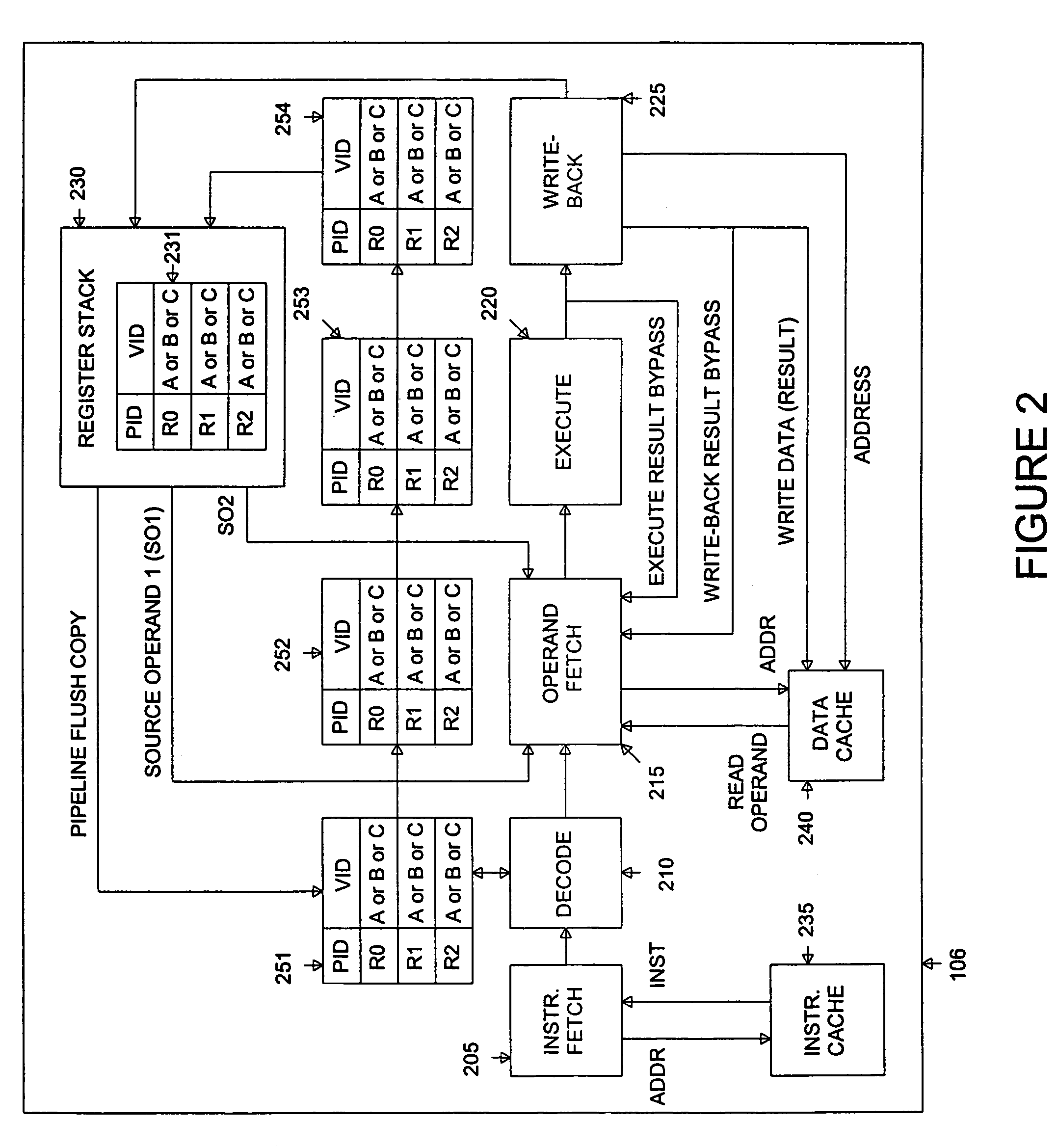

System and method for handling register dependency in a stack-based pipelined processor

InactiveUS7496734B1Digital computer detailsConcurrent instruction executionProcessing InstructionOperand

There is disclosed a data processor comprising 1) a register stack comprising a plurality of architectural registers that stores operands required by instructions executed by the data processor; 2) an instruction execution pipeline comprising N processing stages, where each processing stage performs one of a plurality of execution steps associated with a pending instruction being executed by the instruction execution pipeline; and 3) at least one mapping register associated with at least one of the N processing stages, wherein the at least one mapping register stores mapping data that may be used to determine a physical register associated with an architectural stack register accessed by the pending instruction.

Owner:STMICROELECTRONICS SRL

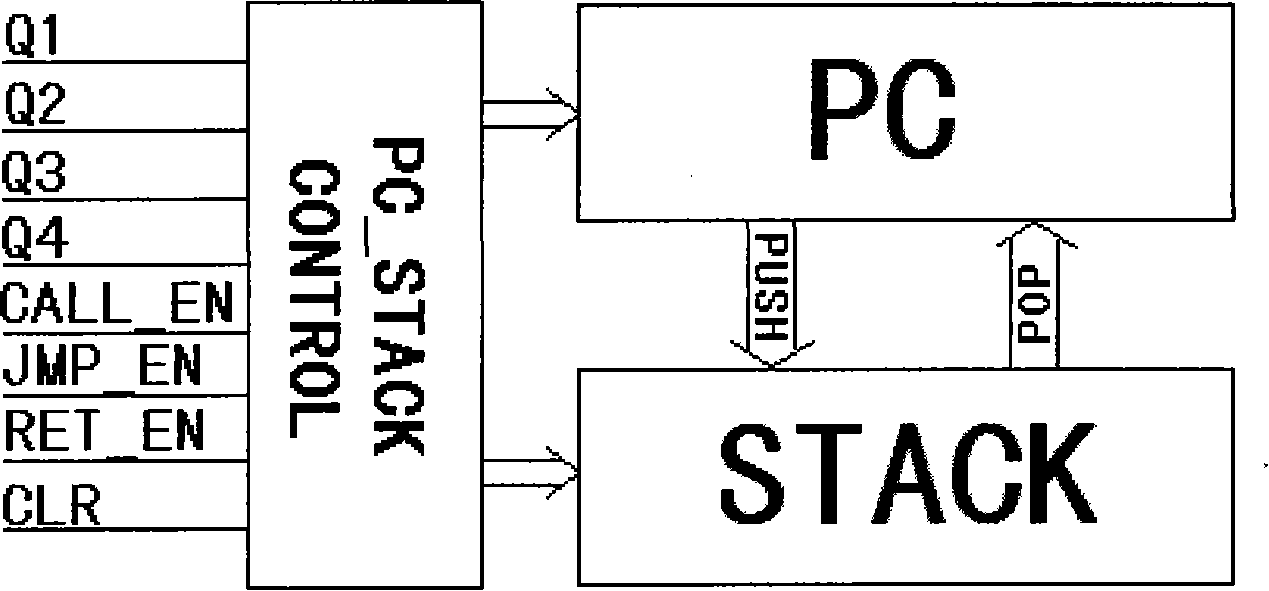

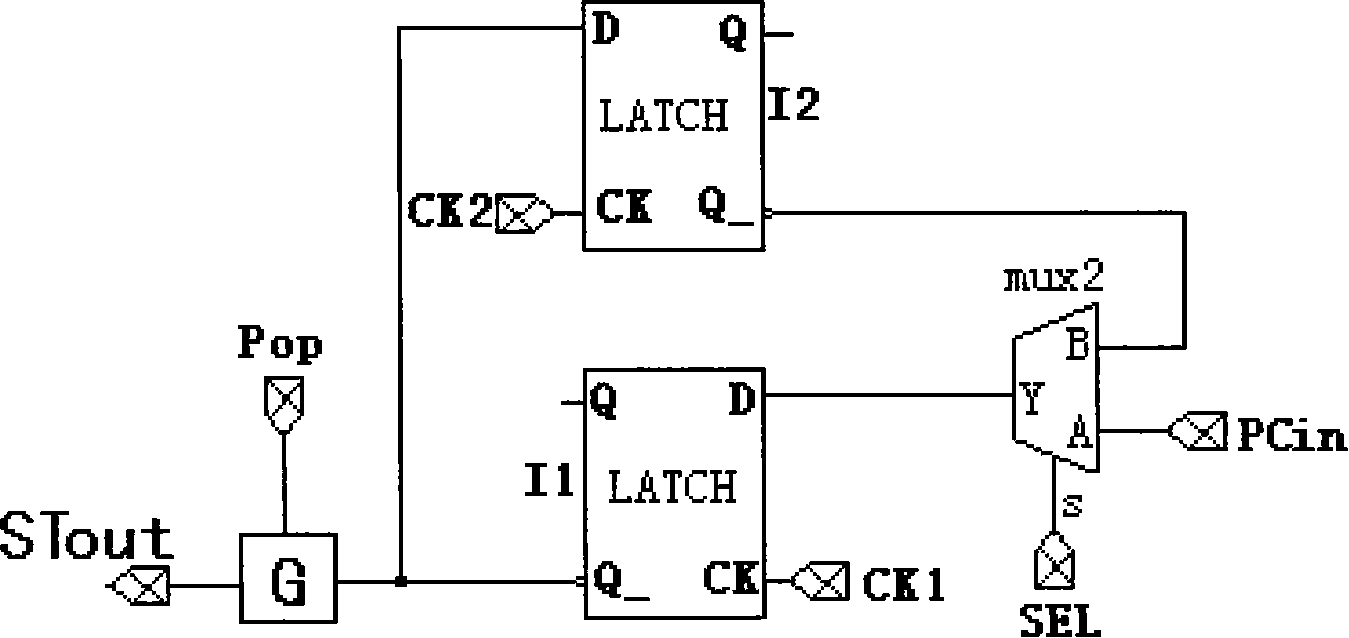

B grade stacking device and data stack pushing and out-stack method

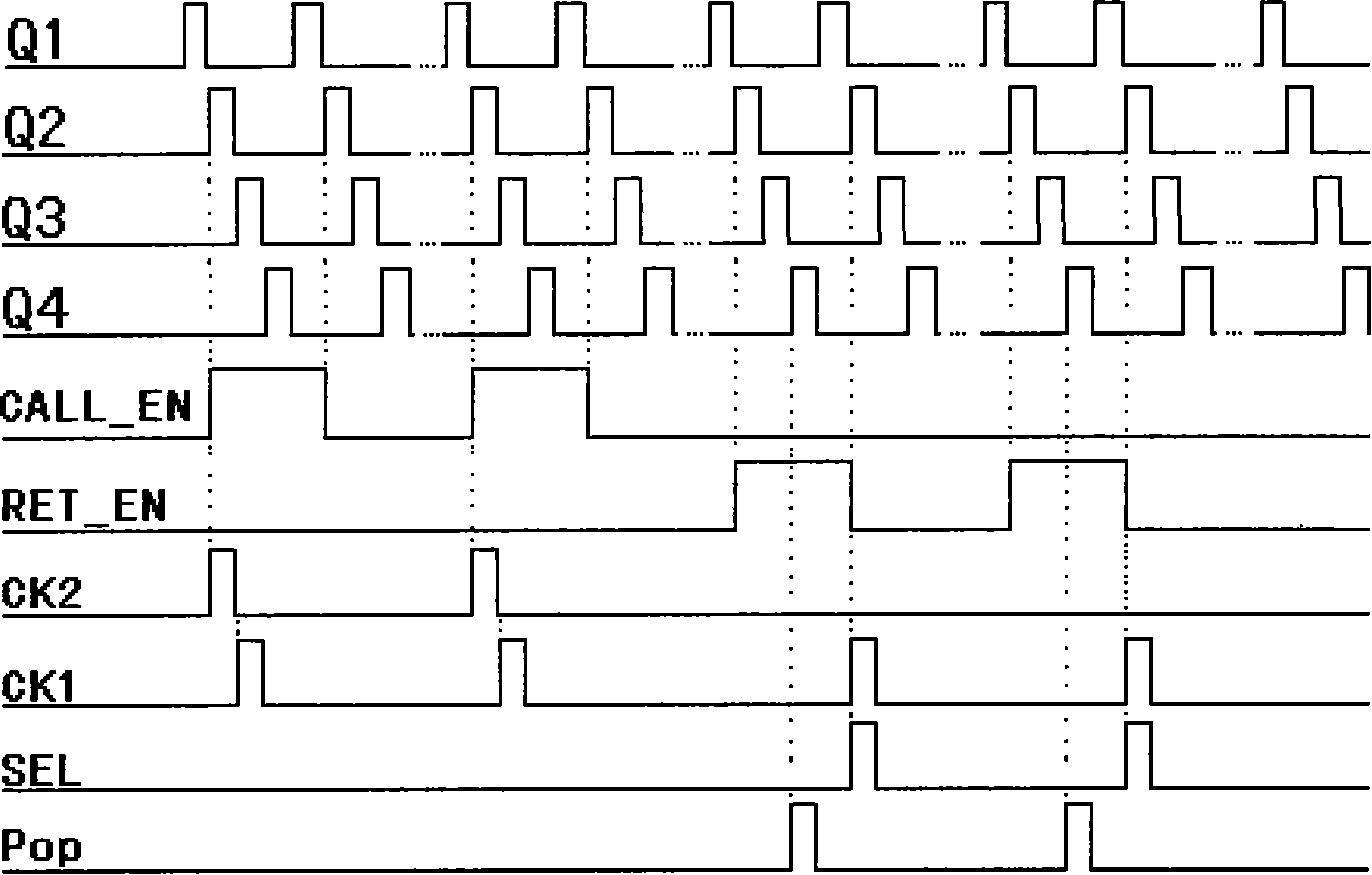

InactiveCN101114236ASimple structureReduce areaMultiprogramming arrangementsConcurrent instruction executionControl signalControl data

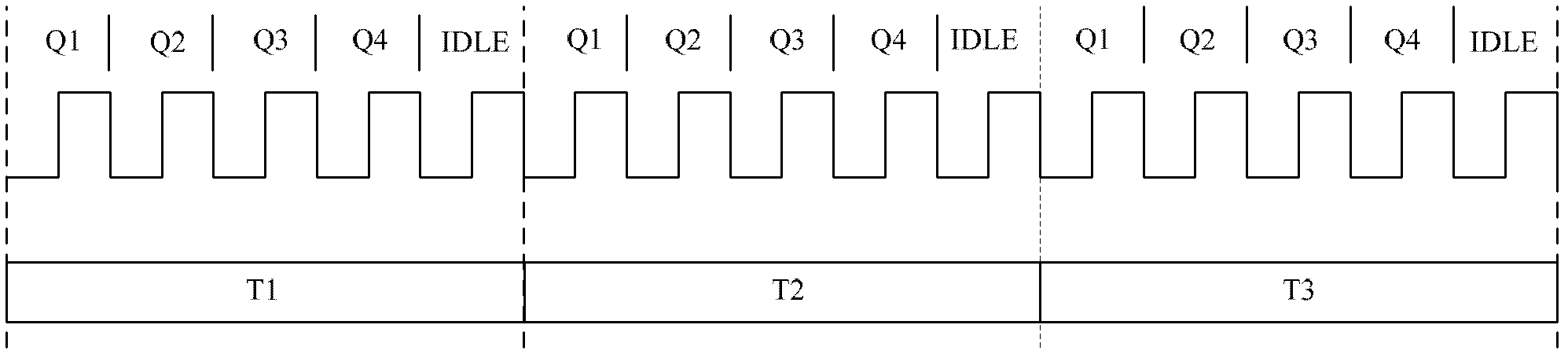

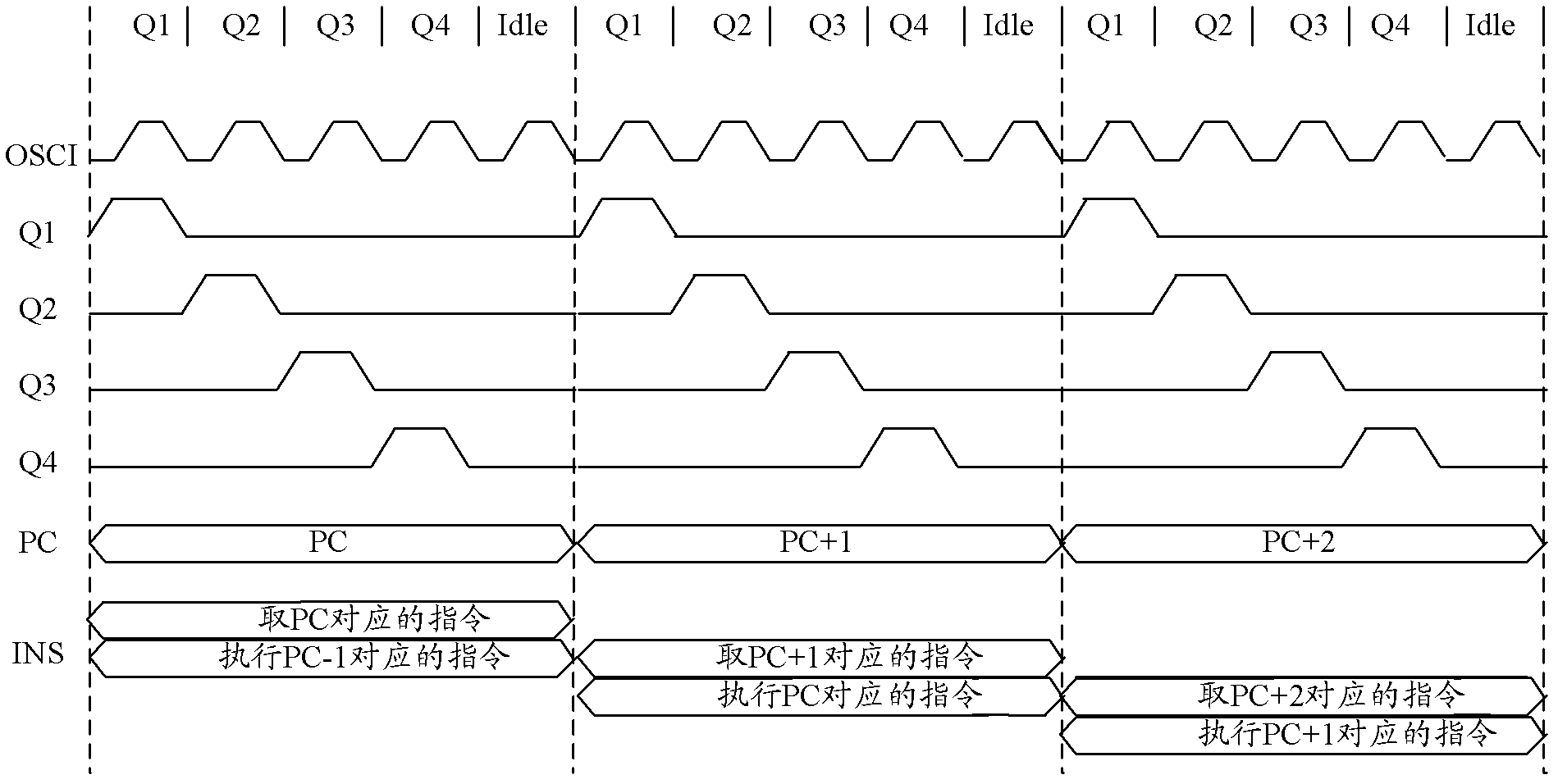

The invention discloses a secondary stack device, which is characterized in that the device comprises a controller, a secondary stack register and an address bus module, wherein, the controller generates controlling signals used for controlling the push stack and pop stack operation of data; the secondary stack register consists of a plurality of basic units and is used for storing push stack data; and the address bus module is connected with the secondary stack register through the address bus. The invention also discloses the push stack and pop stack method of the data in the secondary stack device. The invention has the beneficial effects that an address bus (PC) and a stack (STACK) are combined, the push stack operation and the pop stack operation of the data of stack (STACK) are realized with the characteristic of four-phase clocking, the circuit structure is simple, the control is easy, and circuit size is small, and the cost is effectively lowered.

Owner:SUZHOU HUAXIN MICROELECTRONICS

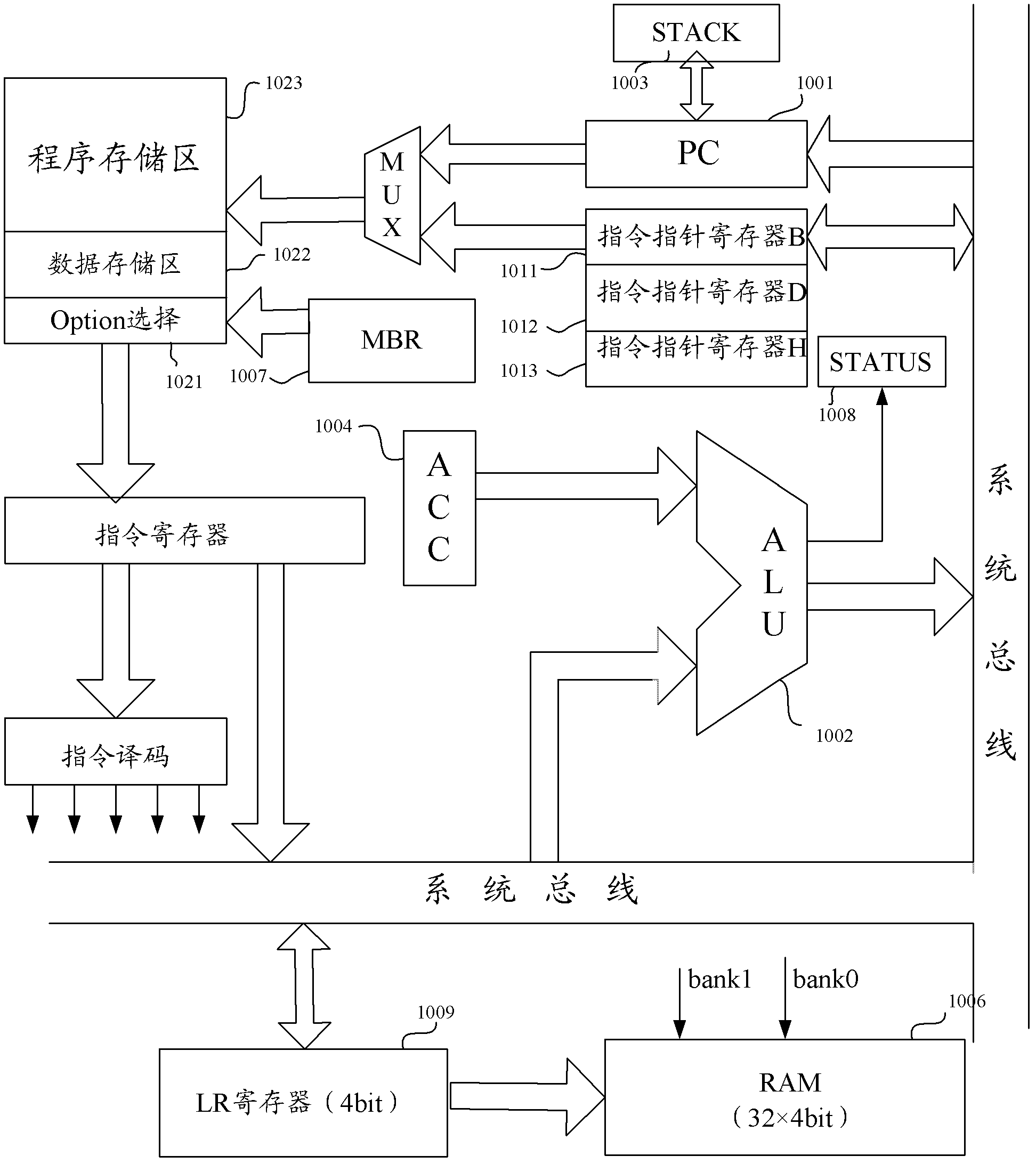

Circuit structure for implementing remote control signal emission instruction control in microprocessor

ActiveCN103186977AImprove execution efficiencySimple designNon-electrical signal transmission systemsComputer architectureData memory

The invention relates to a circuit structure for implementing remote control signal emission instruction control in a microprocessor, wherein the circuit structure comprises a program counter module, a stack register, an instruction pointer register, a multiplexer, a program memory, an instruction register, a storage register, an accumulator, an arithmetic logic unit, a state register, a data memory, a connection register, and a data bus. Because only the data memory is connected to the instruction register by the data bus, when remote control instruction control is performed by the circuit structure, except the operation on the data memory, addressing modes of other instructions are direct addressing modes, the operation can be completed in one period, and the instruction operation time is shortened. Simultaneously, all instructions are 8 bits, thereby simplifying design of hardware and reducing difficulty and complexity for programming personnel. And an instruction pipeline manner, overlaps instruction execution and instruction fetch processes, and raises the instruction execution efficiency. The circuit structure of the invention has advantages of simple structure, low cost and wide application range.

Owner:CRM ICBG (WUXI) CO LTD

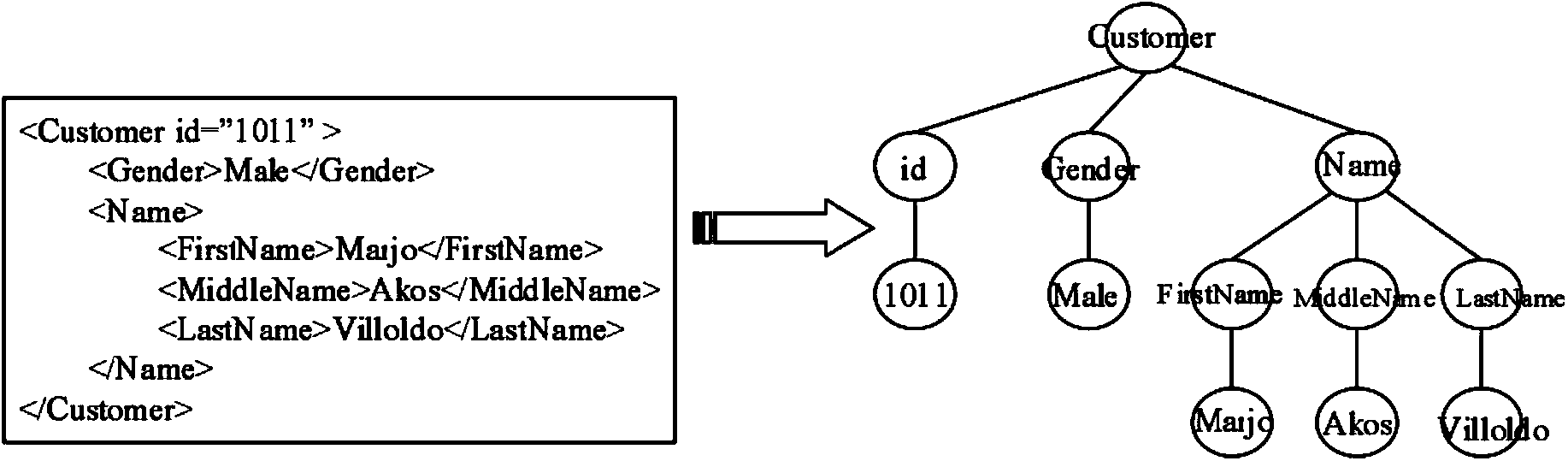

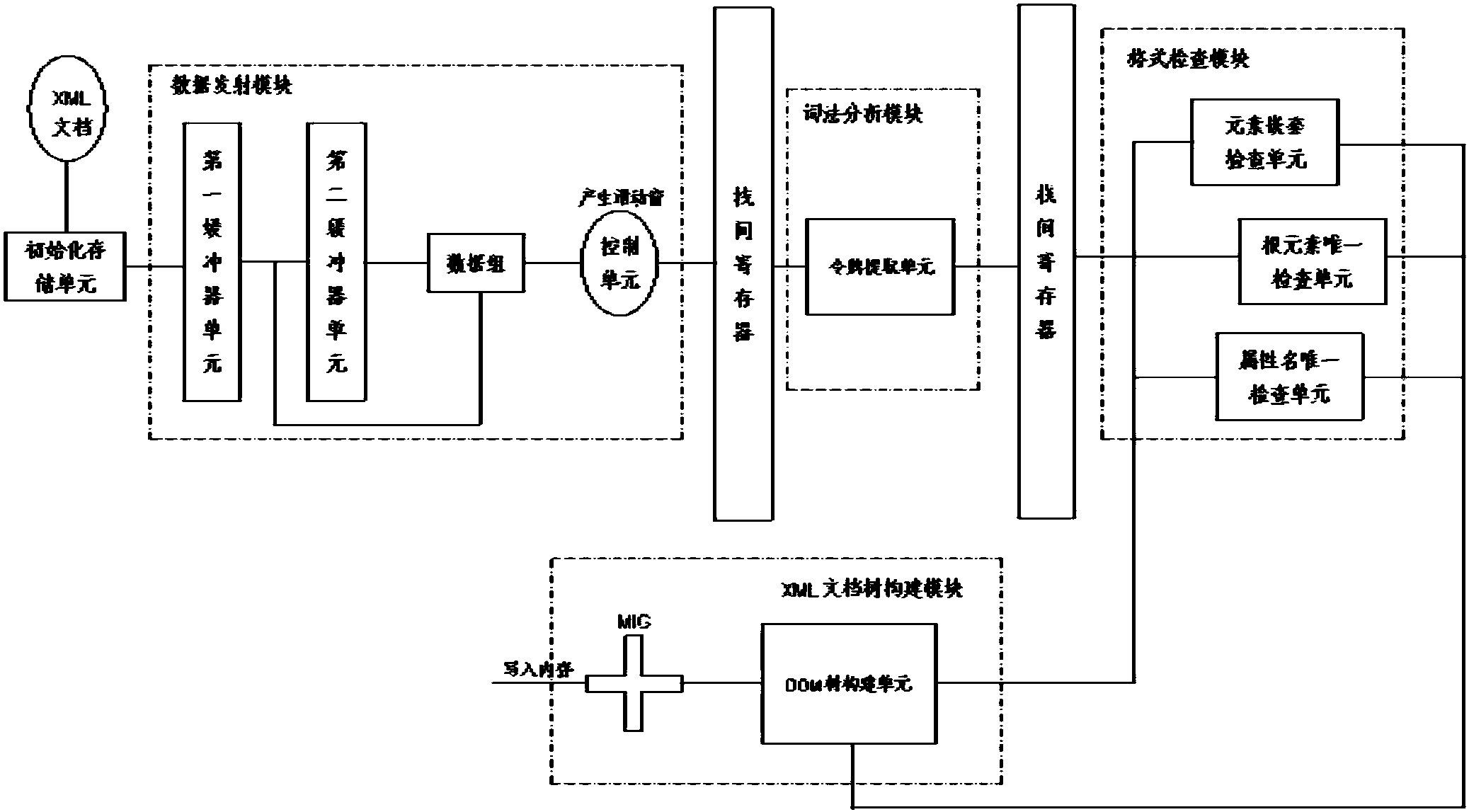

Sliding window technology based hardware XML (Extensive Markup Language) parser

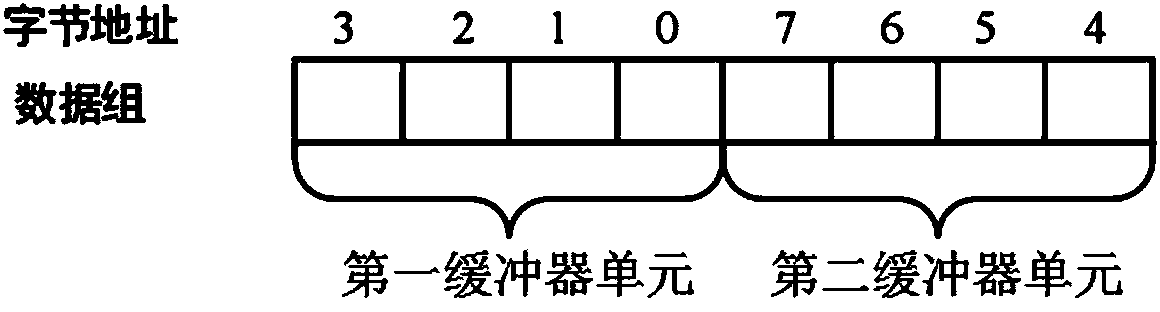

InactiveCN104267998AImprove scalabilityImprove performanceProgram loading/initiatingSpecial data processing applicationsSlide windowLexical analysis

A sliding window technology based hardware XML (Extensive Markup Language) parser comprises an initialization storage unit, inter-stack registers, a data transmitting module, a lexical analysis module, a format checking module and an XML document tree building module; the data transmitting module is used for generating a sliding window; the lexical analysis module is used for extracting a character stream of an XML document into a token; the format checking module is used for checking the token of the XML document through an XML syntax rule; the initialization storage unit is connected with the data transmitting module and used for transmitting the initialization information of the XML document; the data transmitting module is connected with the lexical analysis module and used for transmitting the sliding window information; the lexical analysis module is connected with the format checking module and the XML document tree building module and used for transmitting the token information; the XML document tree building module is connected with a memory and used for transmitting the XML document tree information; the inter-stack registers which are used for improving the throughput rate are arranged between the modules which are connected with each other respectively. According to the sliding window technology based hardware XML parser, the working efficiency of the XML parser is greatly improved, the high resolution performance can be implemented, the hardware cost is low, and the practicability is high.

Owner:SHANGHAI JIAO TONG UNIV

Microprocessor communications system

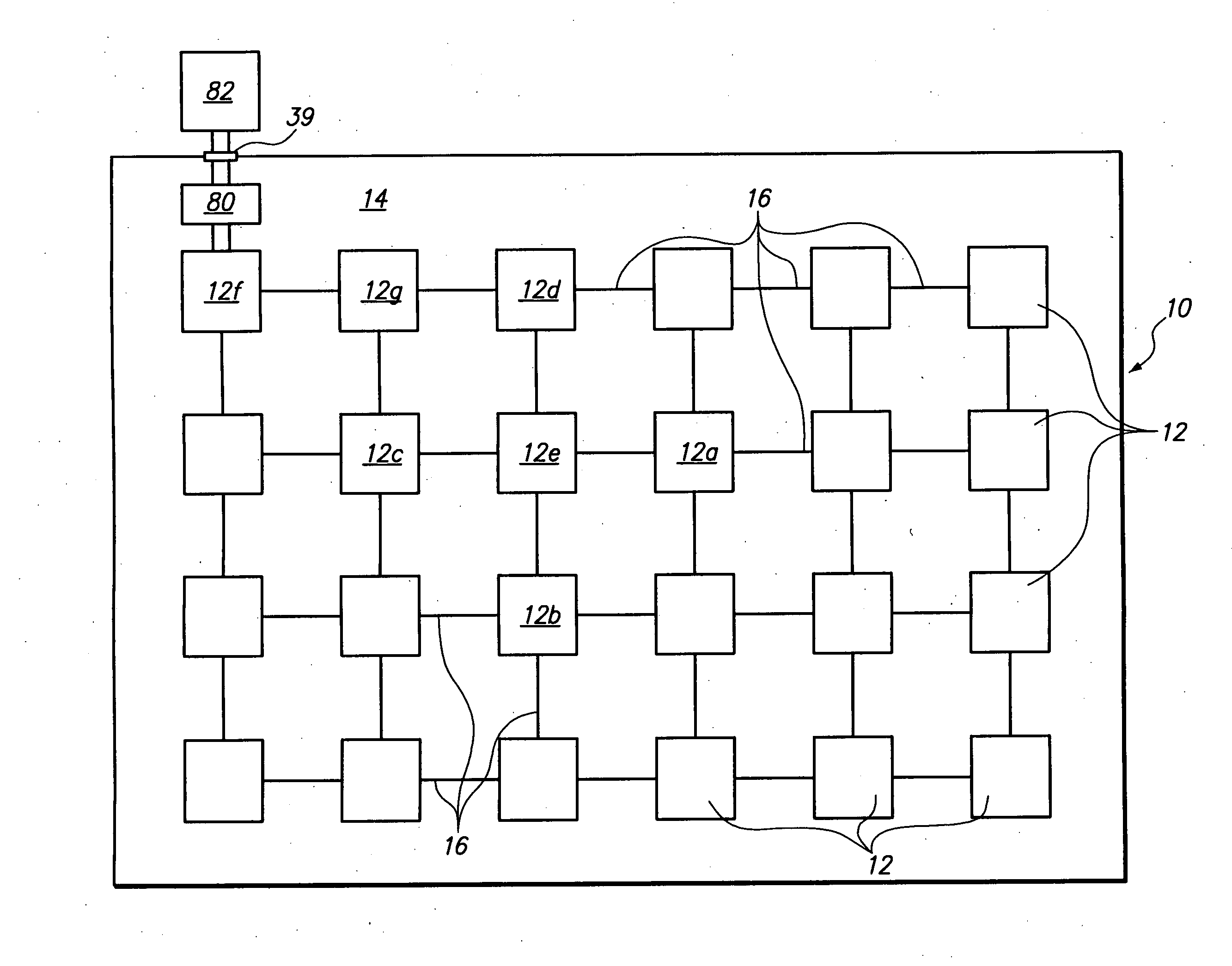

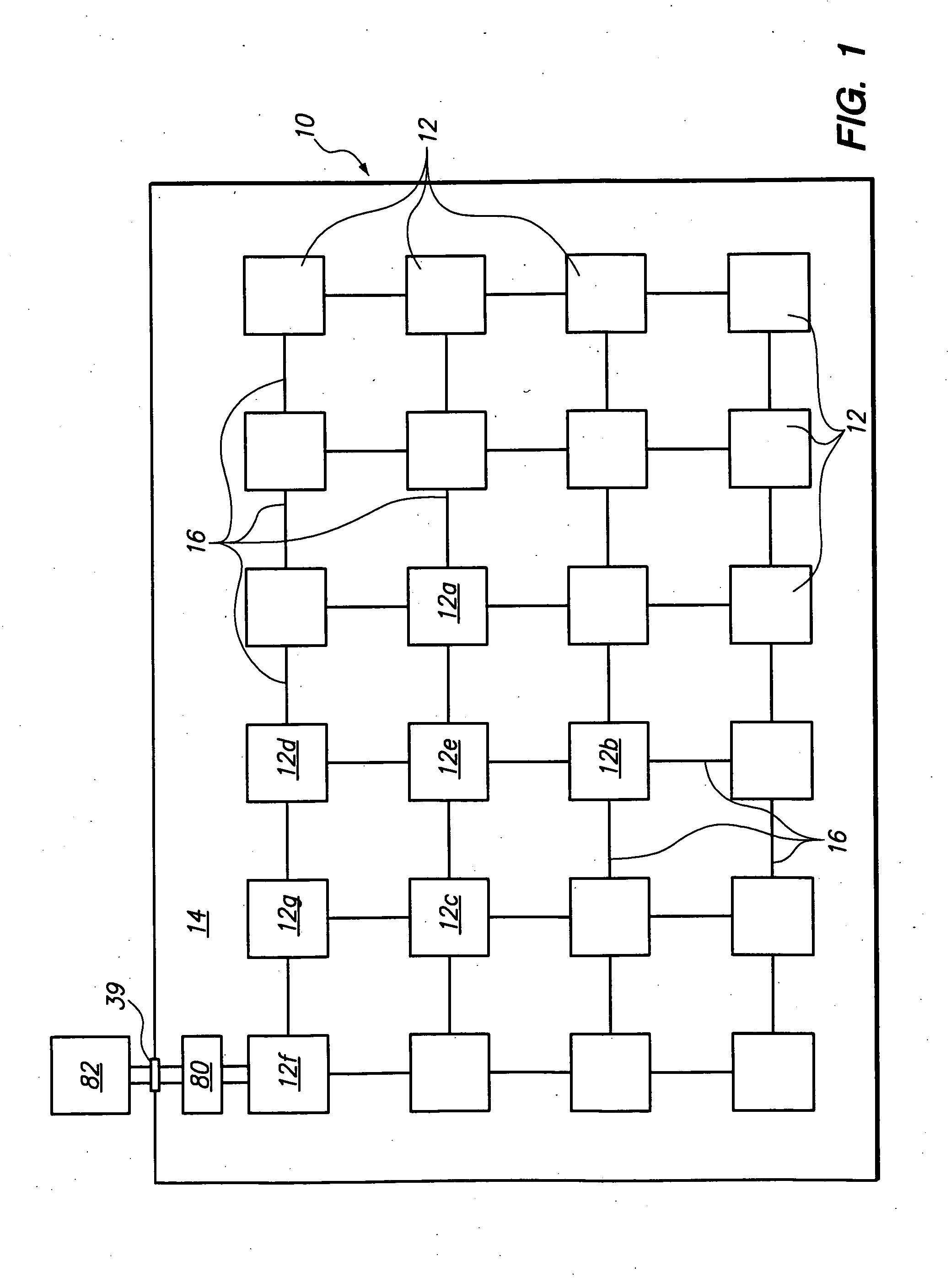

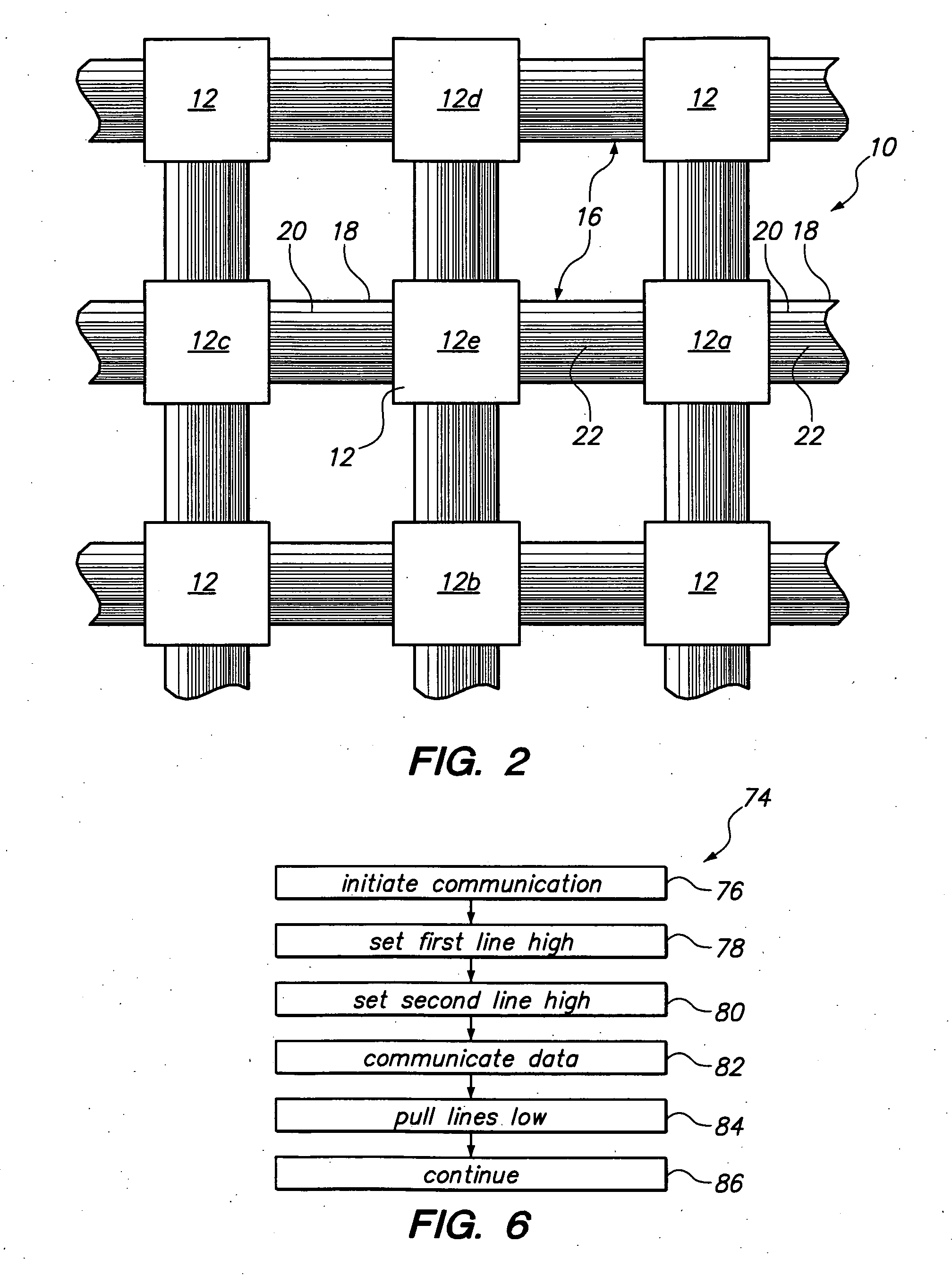

InactiveUS20100325389A1Improve processing speedEfficient processor architectureProgram control using wired connectionsGeneral purpose stored program computerShift registerCommunications system

A microprocessor communications system utilizes a combination of an activity status monitor register and one or more address select registers to read from a communications port of one processor and write to a communications port of an adjacent processor in a single instruction word loop. This circumvents the requirement to save and retrieve data and / or instructions from memory. A stack register selector contains a plurality of stack registers and a plurality of shift registers, which are interconnected. The stack registers are selected by the shift registers in such a way that the stack registers operate in a circular repeating pattern, which prevents overflow and underflow of stacks.

Owner:VNS PORTFOLIO LLC

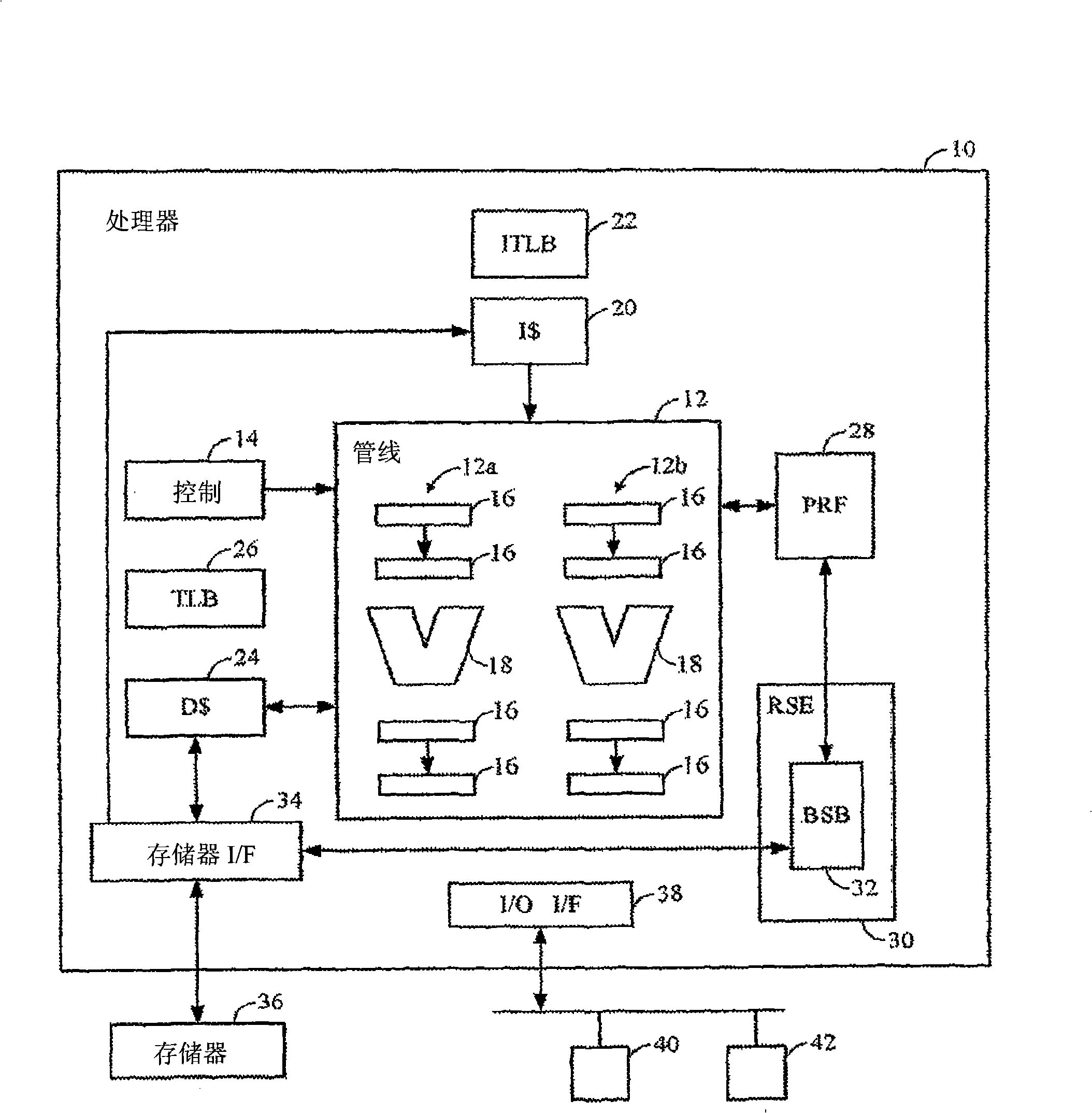

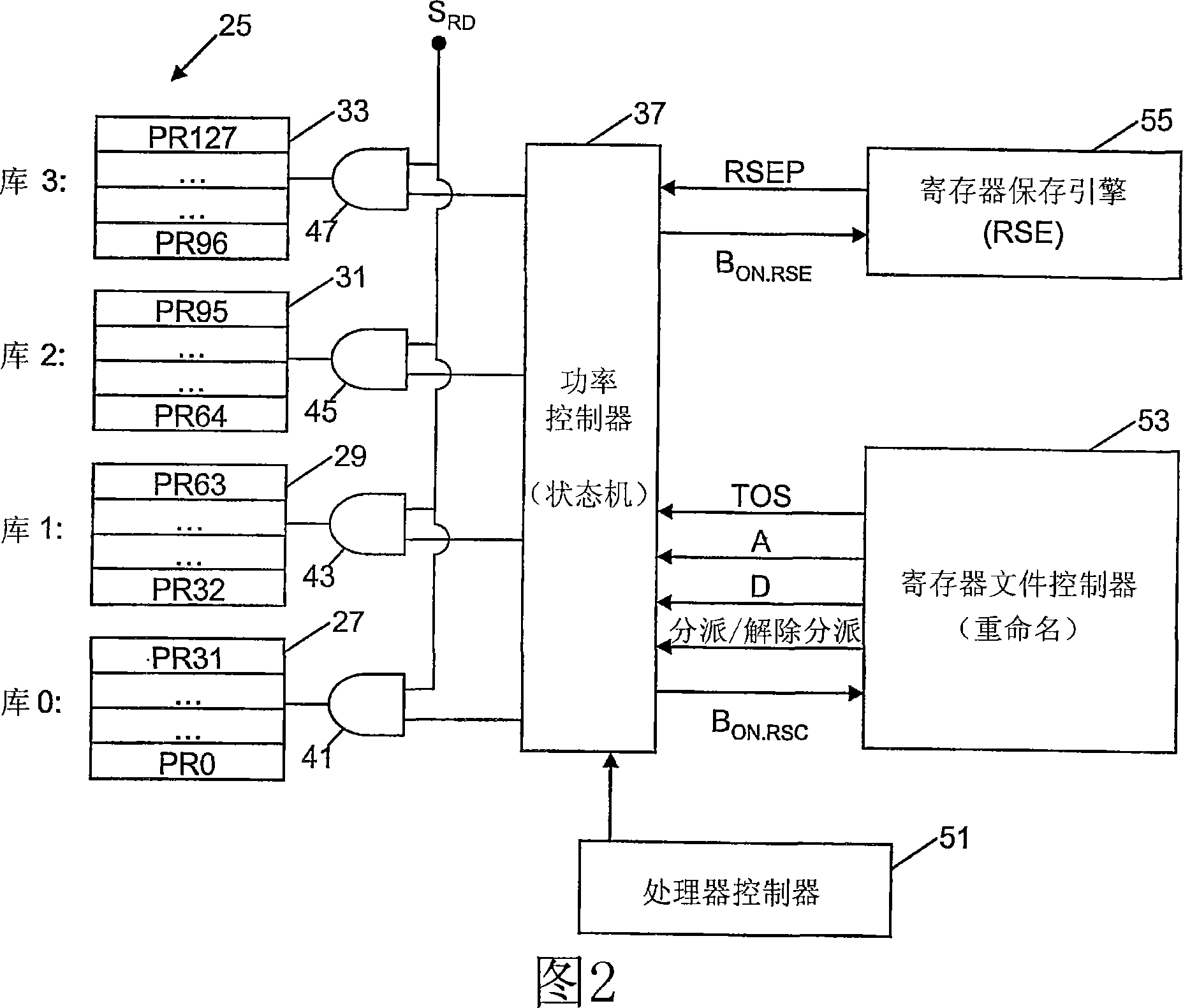

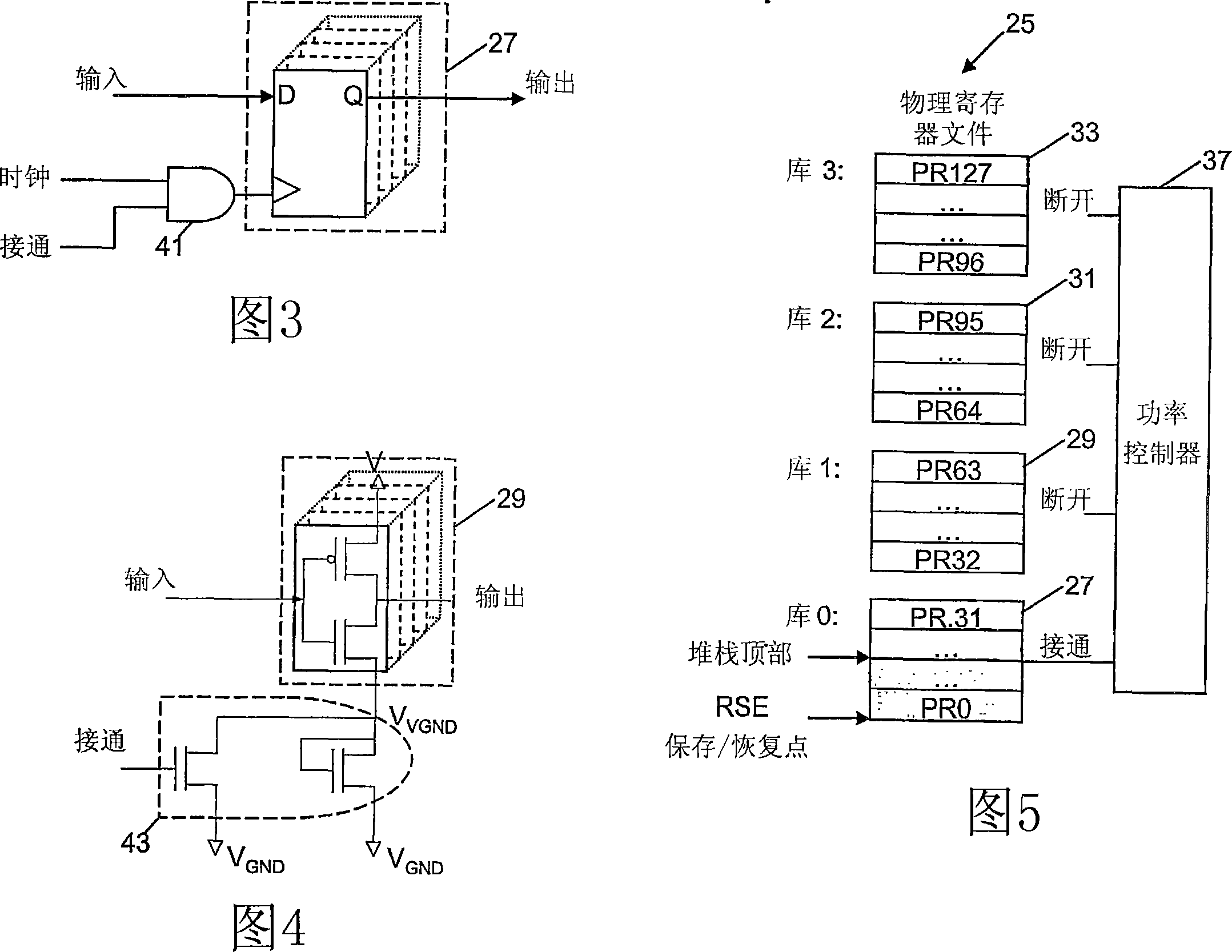

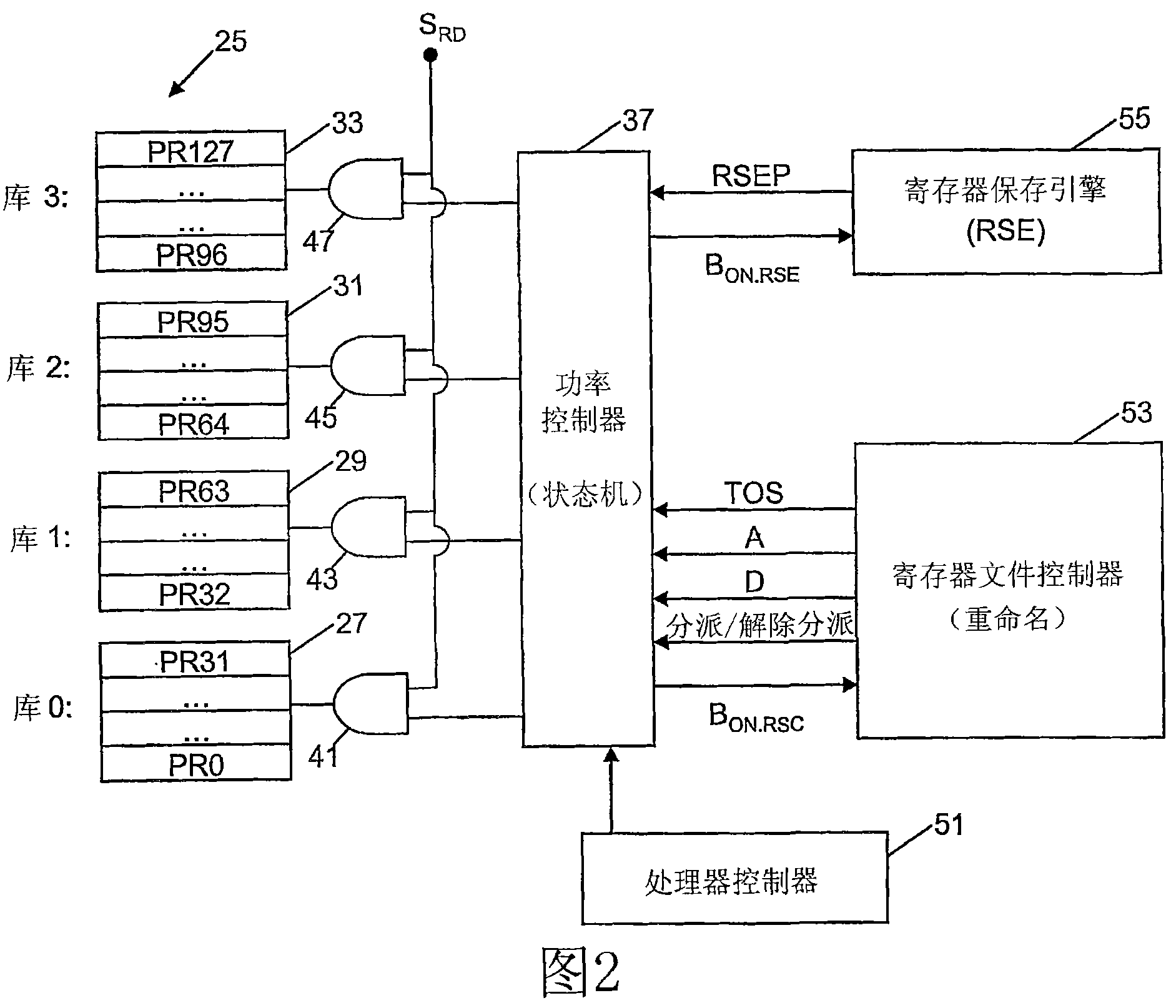

Backing store buffer for the register save engine of a stacked register file

InactiveCN101331448AMemory loss protectionNext instruction address formationTemporary storageRegister file

A Backing Store Buffer is interposed between a Physical Register File and the Backing Store in a stacked register file architecture. A Register Save Engine temporarily stores data from registers in the Physical Register File allocated to inactive procedures on-chip, freeing the registers to be re-allocated to new procedures. When the a procedures complete and returns control to a prior, inactive procedure, the Register Store Engine retrieves data associated with the inactive procedure from the Backing Store Buffer to registers in the Physical Register File, and the registers are re-allocated to the inactive procedure. The Register Save Engine saves data from the Backing Store Buffer to to the Backing Store, incurring the significant performance degradation and power consumption required for off-chip RAM access, only when the Backing Store Buffer is full and more data must be saved from the Physical Register File.

Owner:QUALCOMM INC

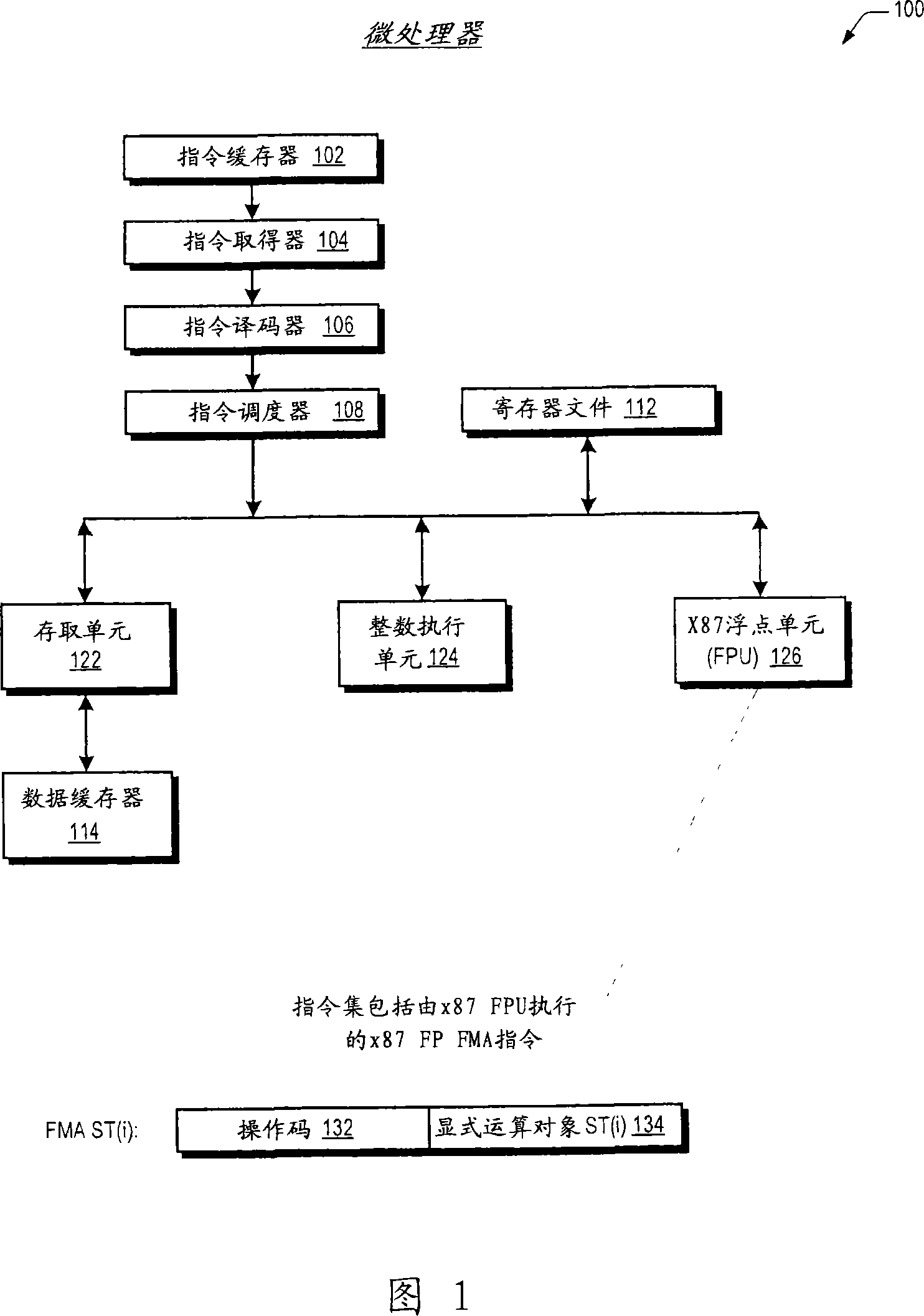

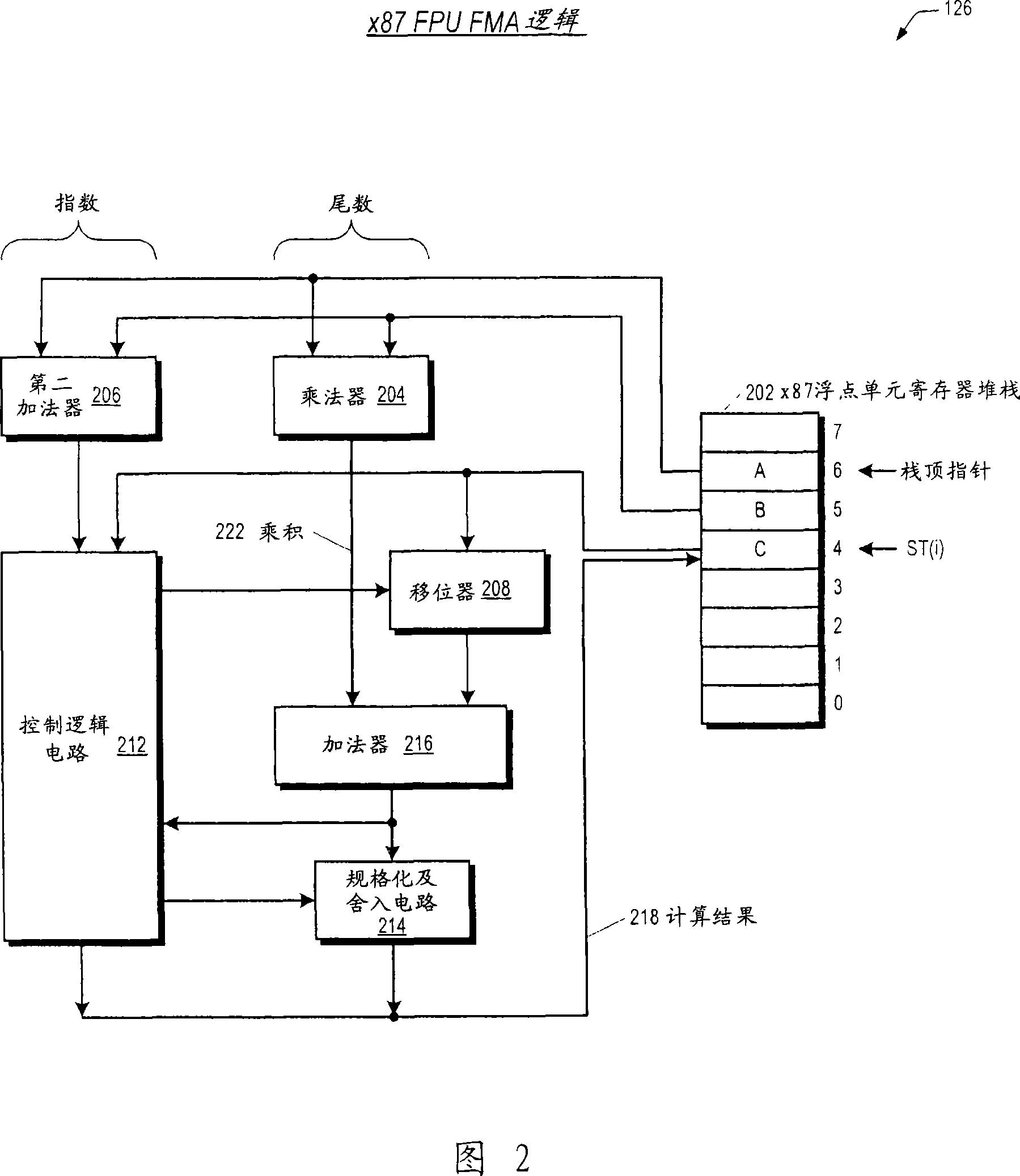

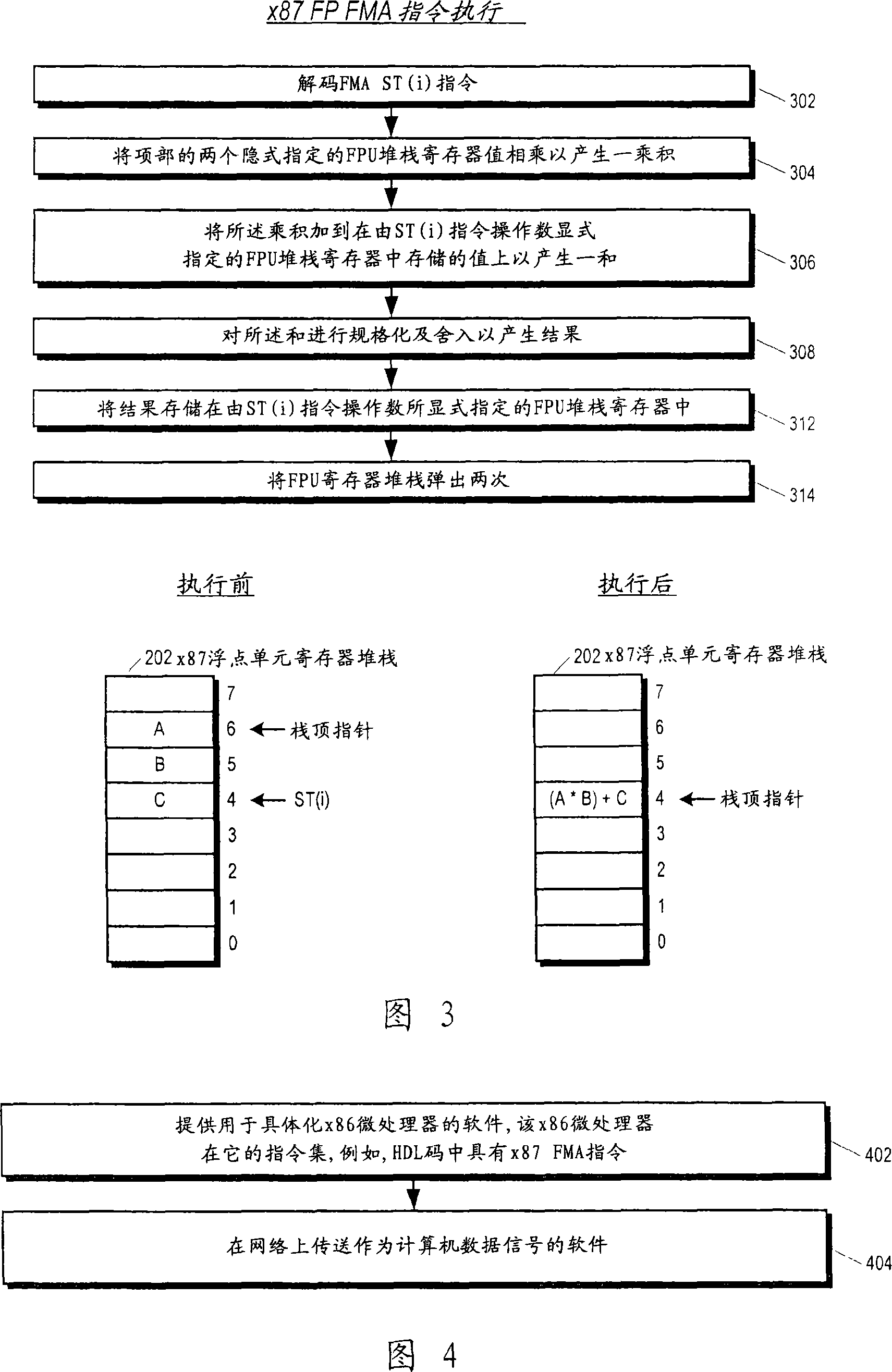

X87 fused multiplication-addition instruction and its use

An x87 fused multiply-add (FMA) instruction in the instruction set of an x86 architecture microprocessor is disclosed. The FMA instruction implicitly specifies the two factor operands as the top two operands of the x87 FPU register stack and explicitly specifies the third addend operand as a third x87 FPU register stack register. The microprocessor multiplies the first two operands and adds the product to the third operand to generate a result. The result is stored into the third register and the first two operands are popped off the stack. In an alternate embodiment, the third operand is also implicitly specified as being stored in the register that is two registers below the top of stack register; the result is also stored therein. The instruction opcode value is in the x87 opcode range.

Owner:VIA TECH INC

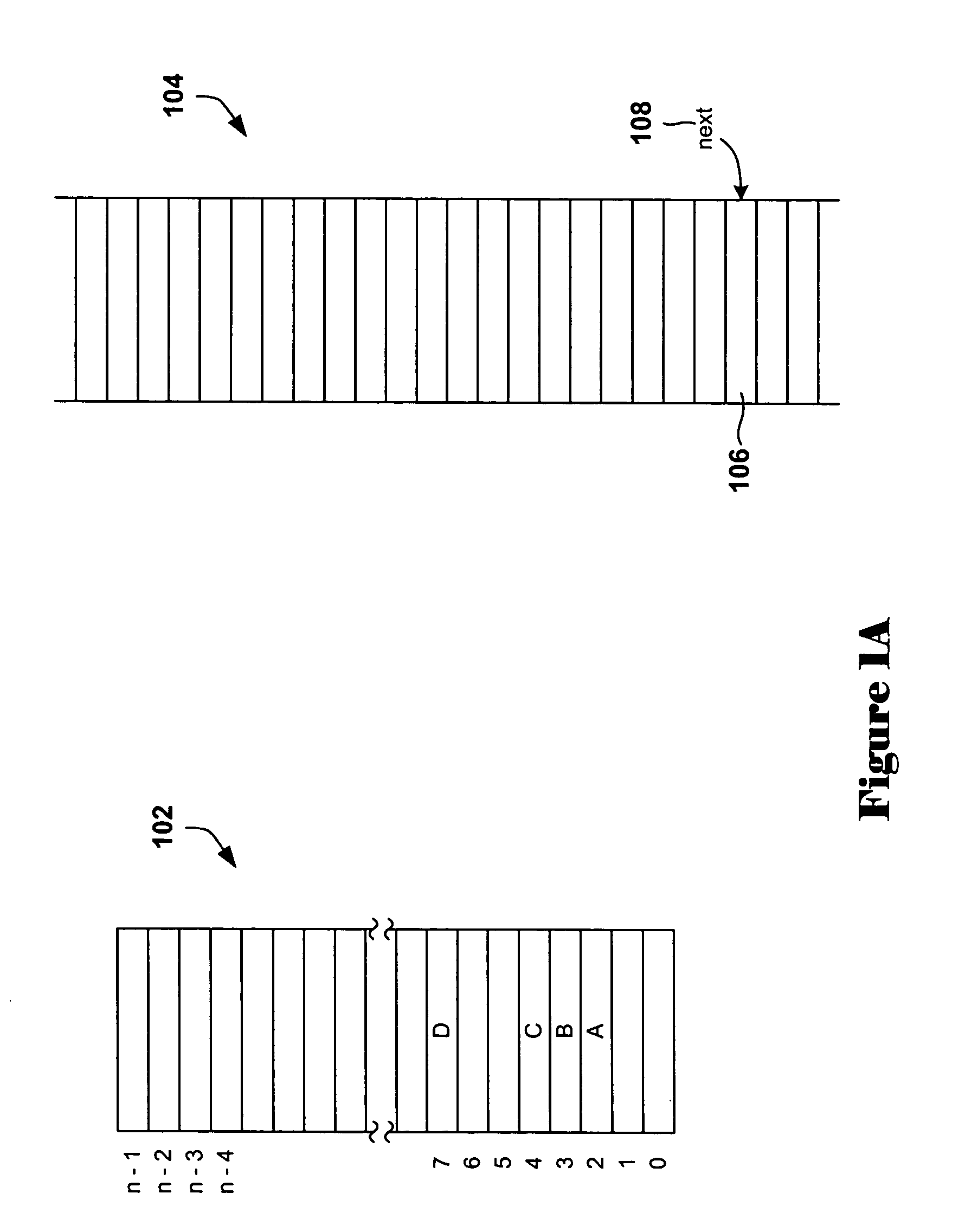

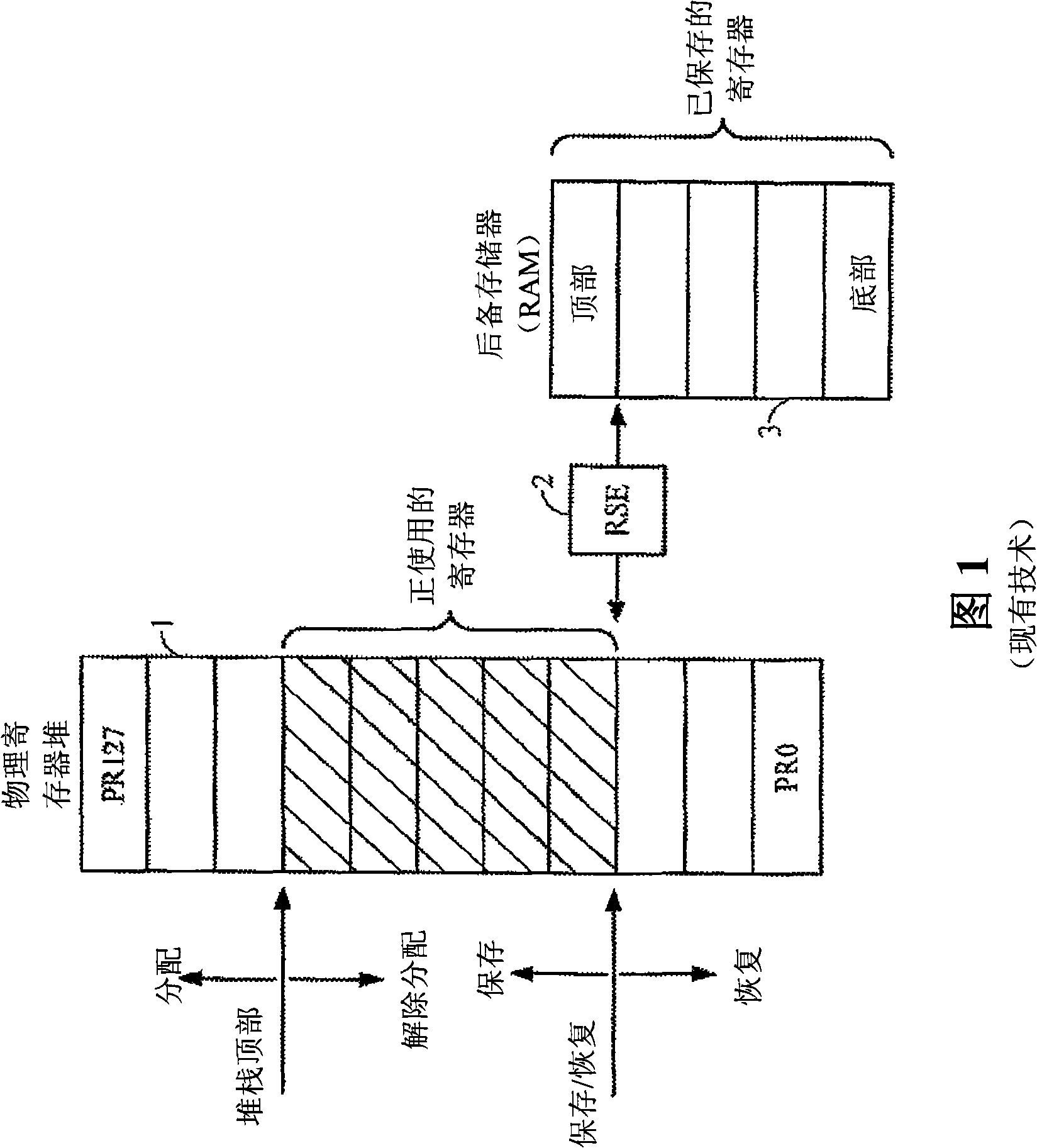

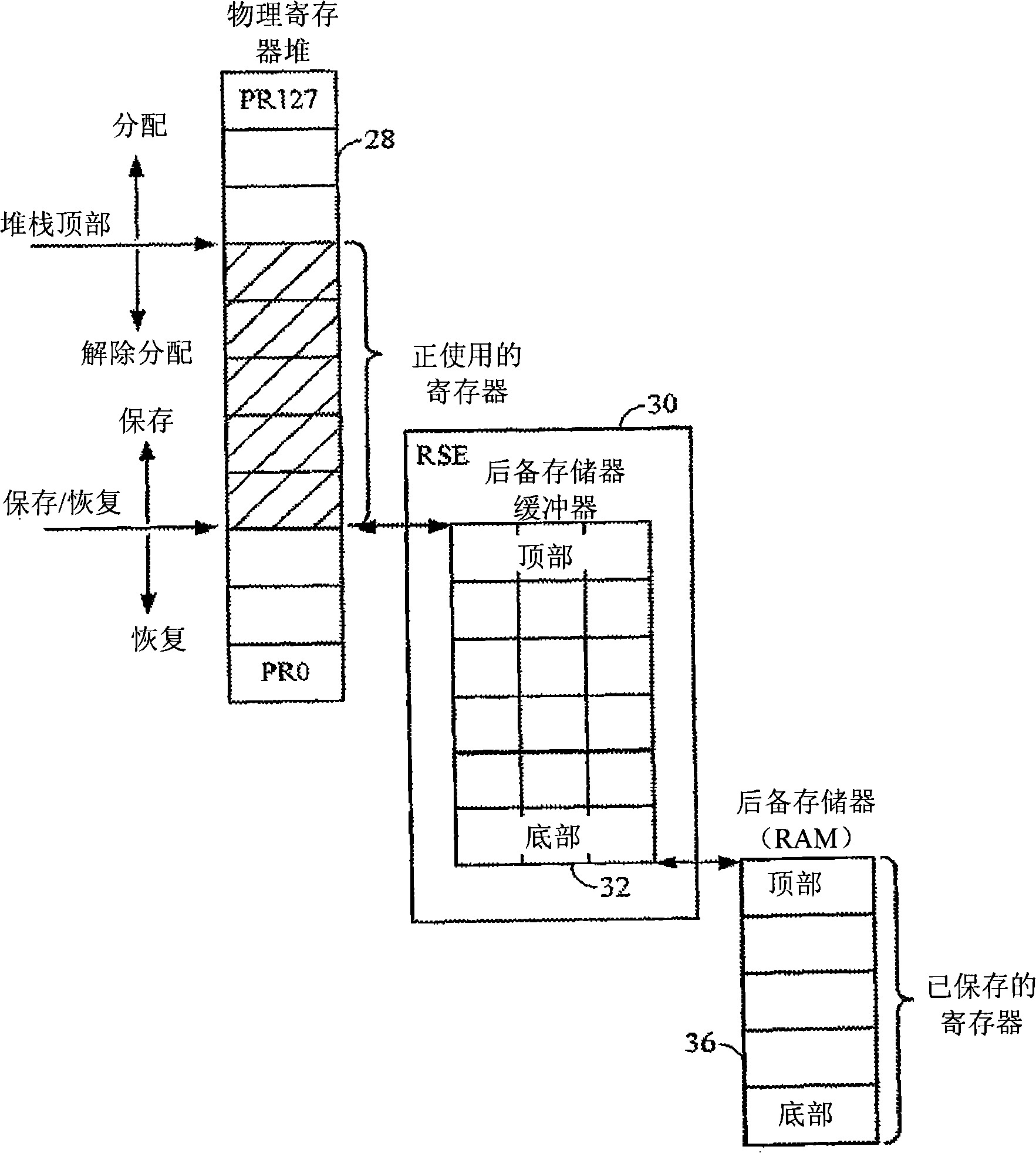

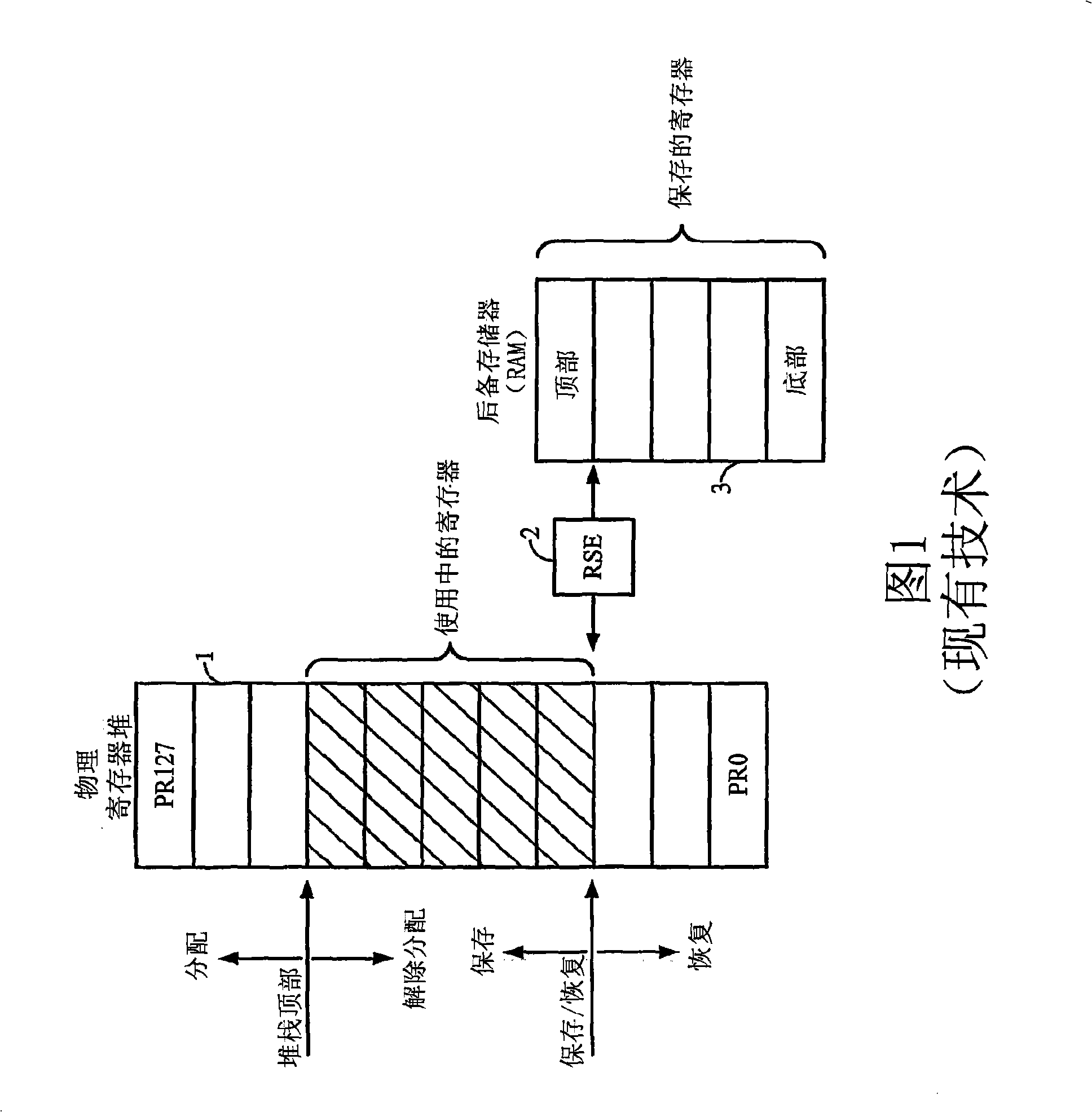

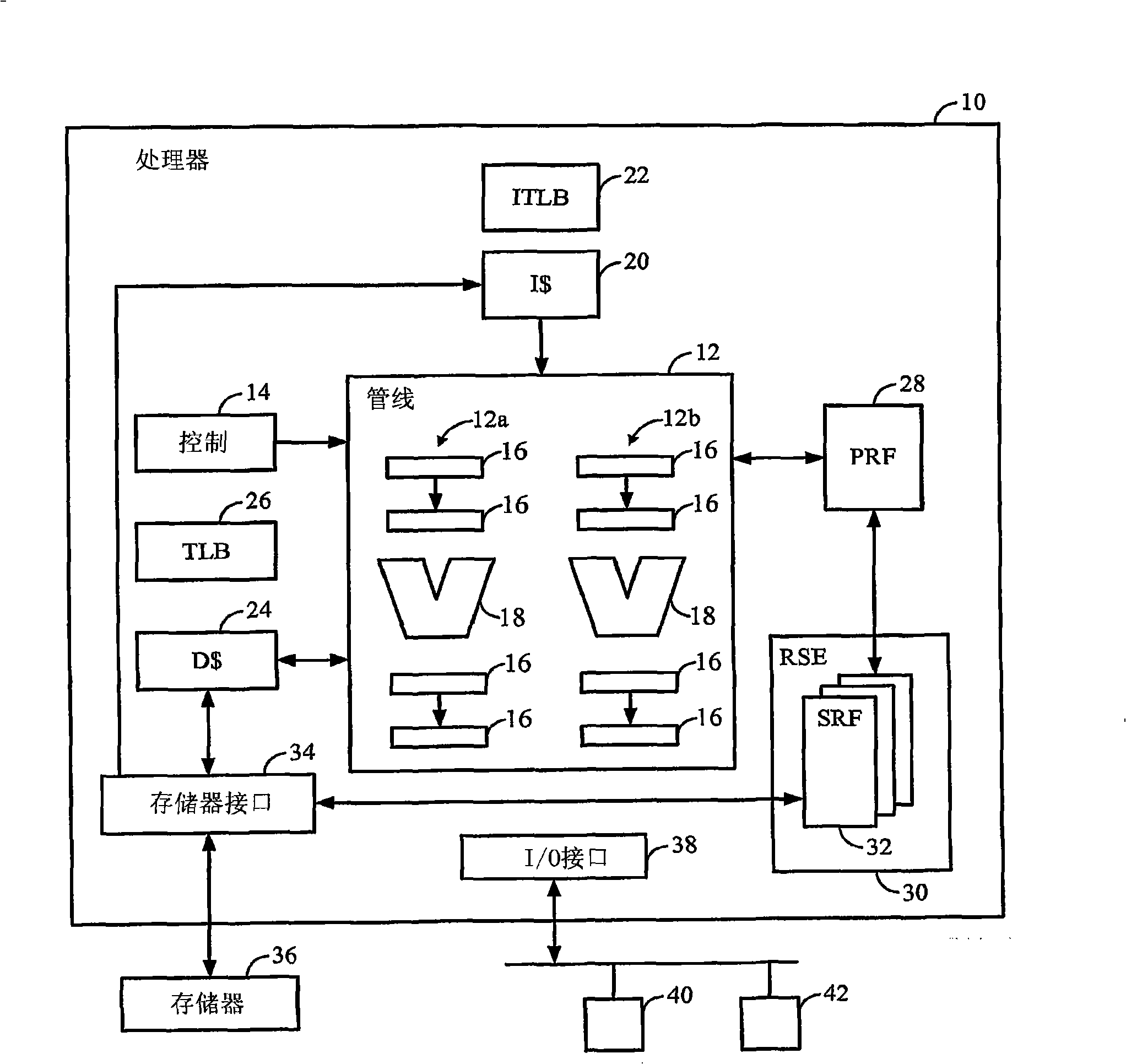

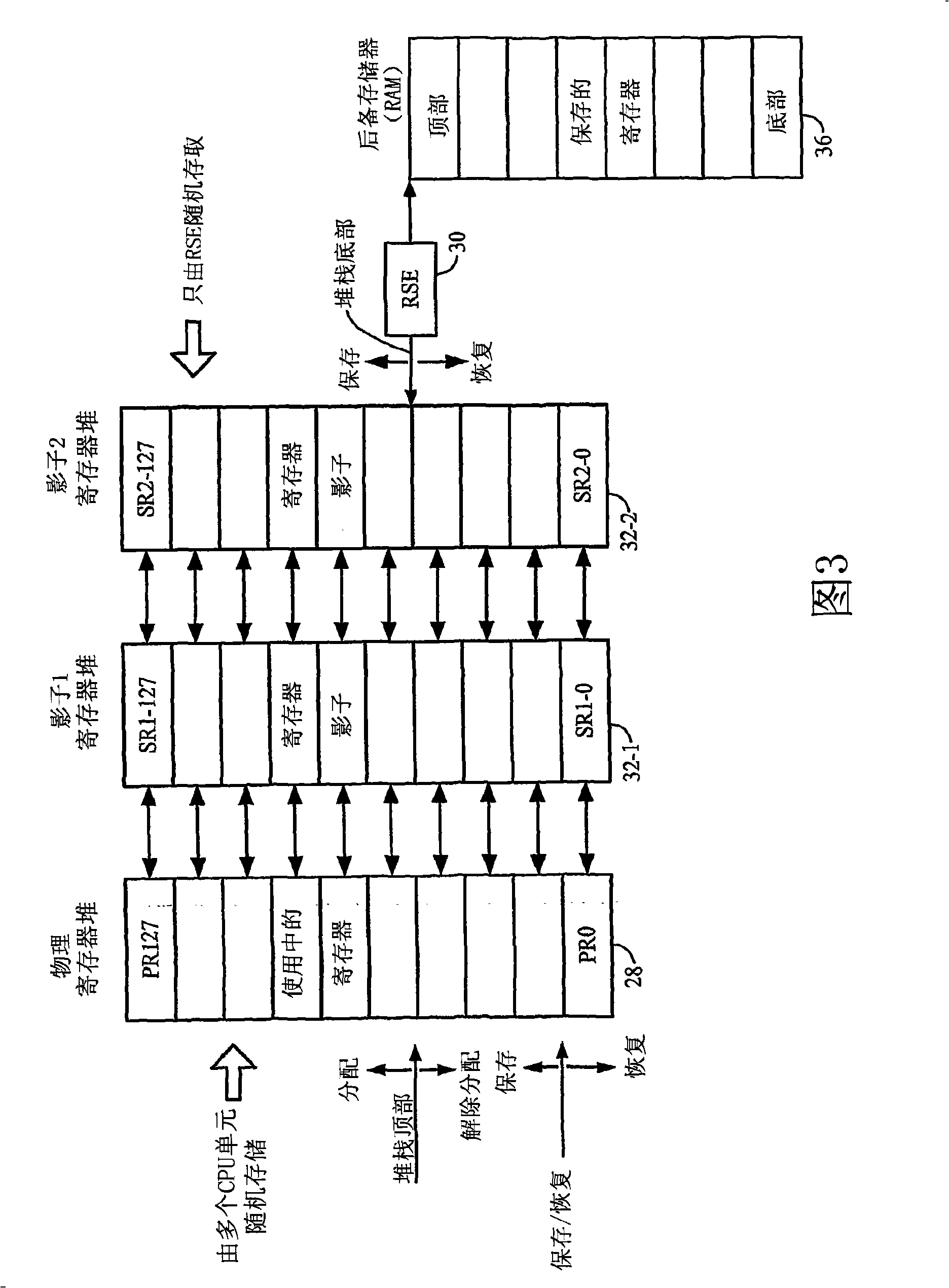

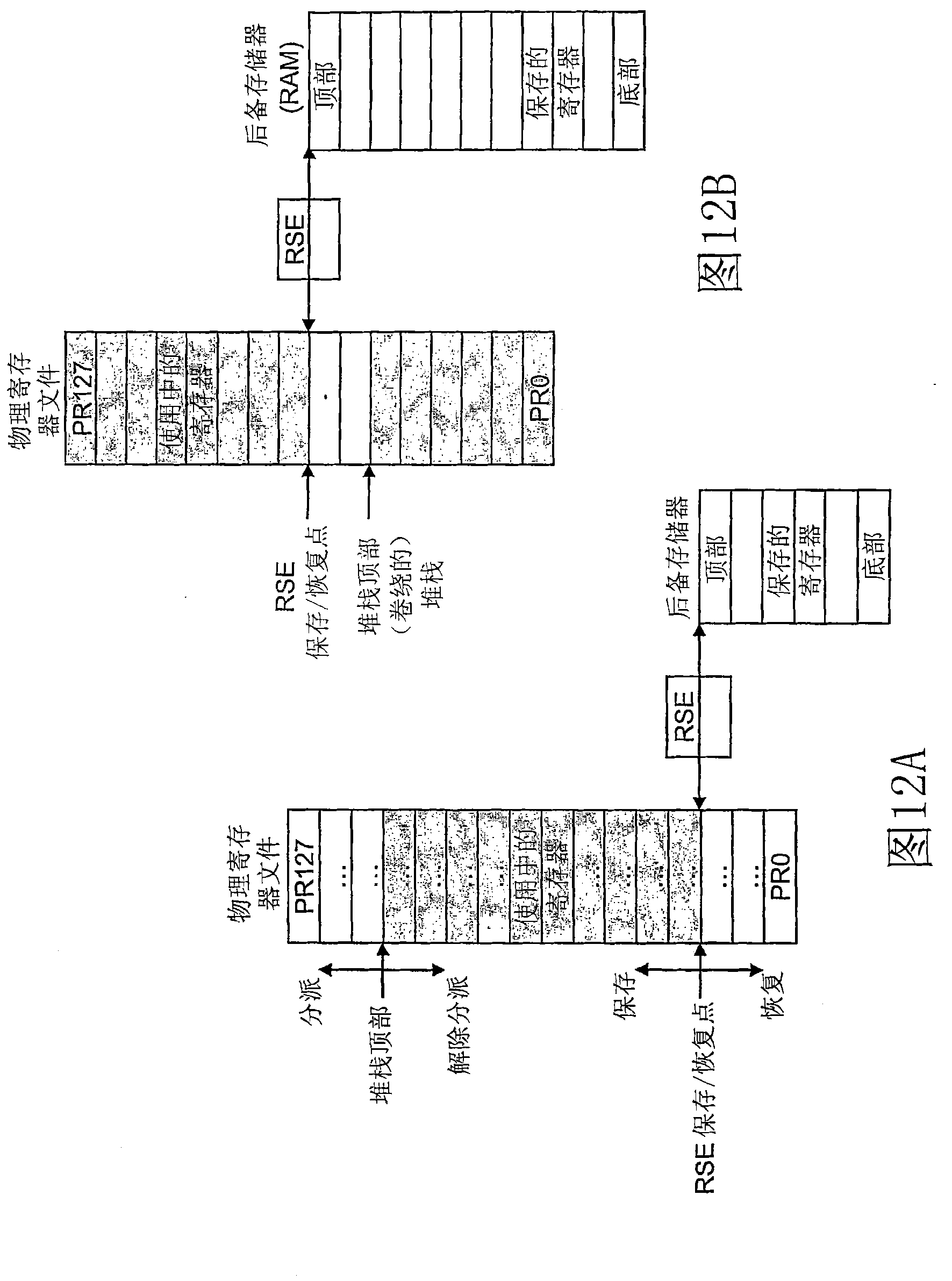

Expansion of a stacked register file using shadow registers

One or more Shadow Register Files (SRF) are interposed between a Physical Register File (PRF) and a Backing Store (BS) in a shadow register file system. The SRFs comprise dual-port registers connected serially in a chain of arbitrary depth from the PRF. A Register Save Engine has random access to one port of the registers in the final SRF in the chain, and saves / restores data between the final SRF and the BS, e.g., RAM. As PRF registers are deallocated from calling procedures for use by called procedures, data are serially shifted from multi-port registers in the PRF through successive corresponding dual-port registers in SRFs, and are serially shifted back toward the multi-port registers as the PRF registers are reallocated to calling procedures. Since no procedure can access more than the number of registers in the PRF, the effective size of the PRF is increased, using less costly dual-port registers.

Owner:QUALCOMM INC

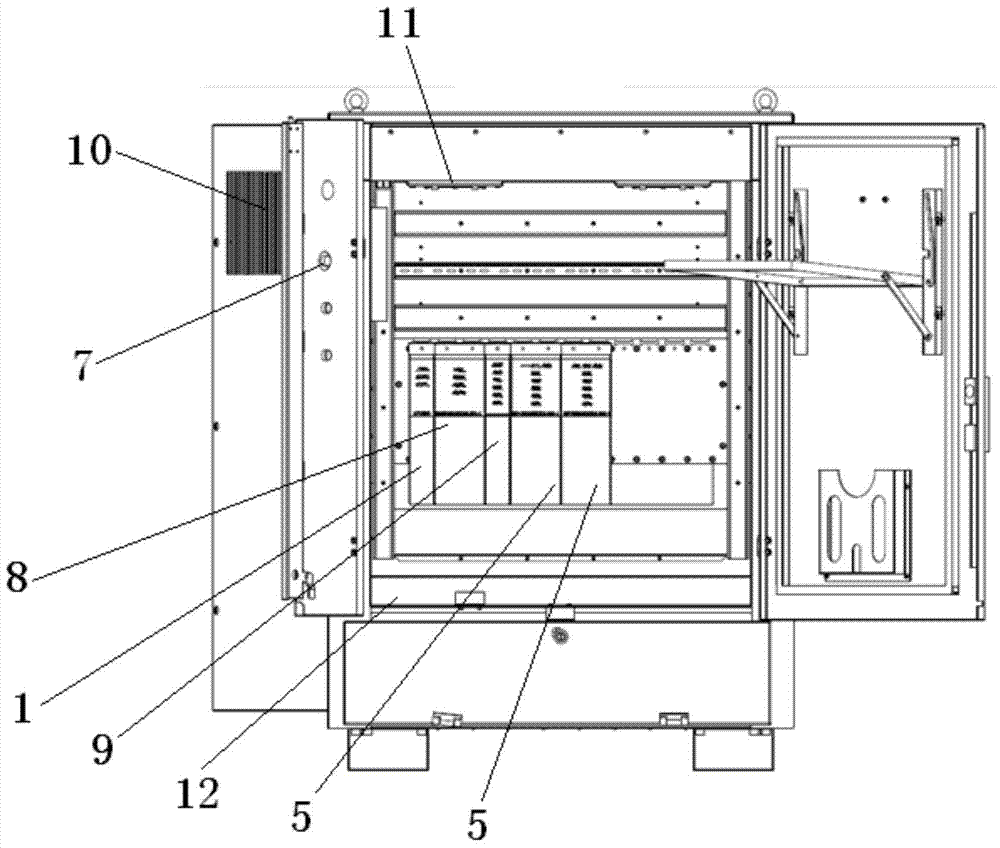

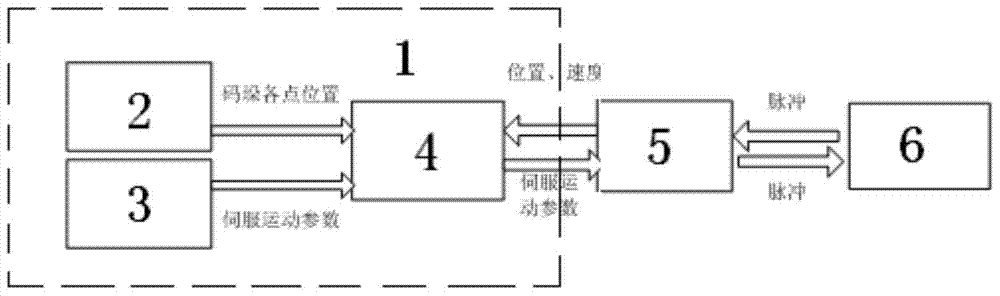

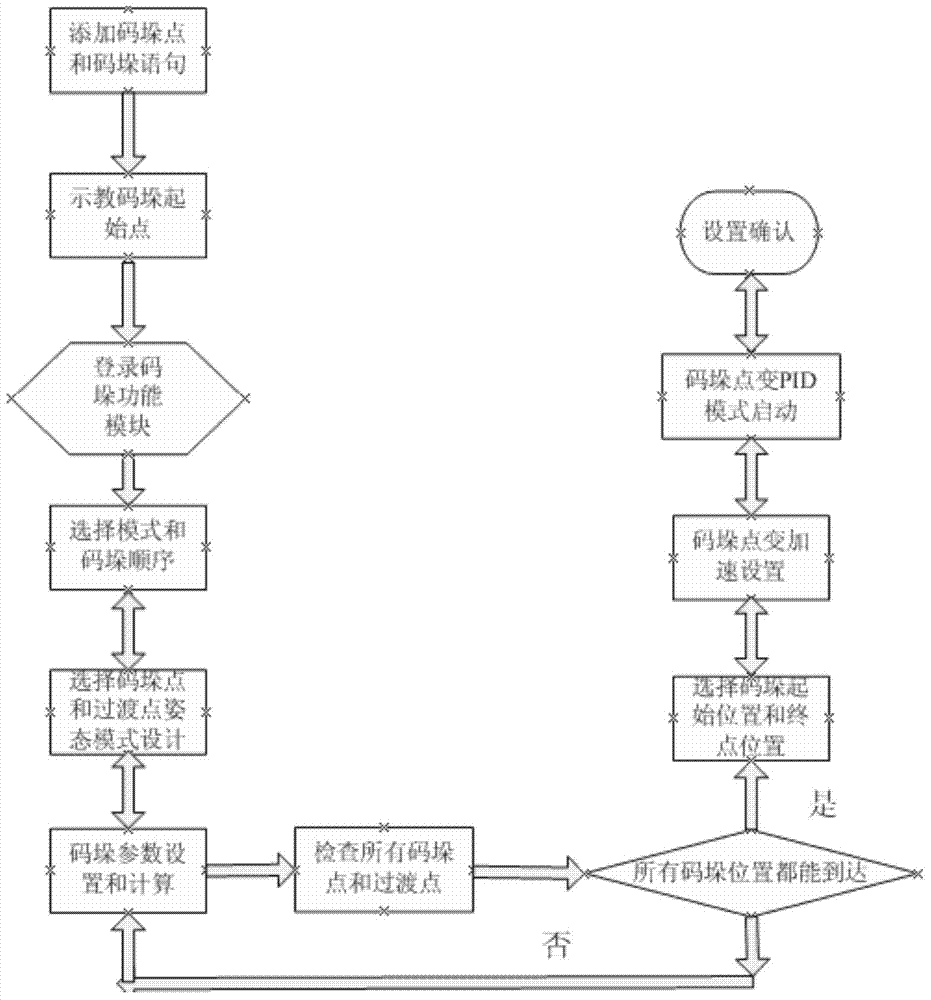

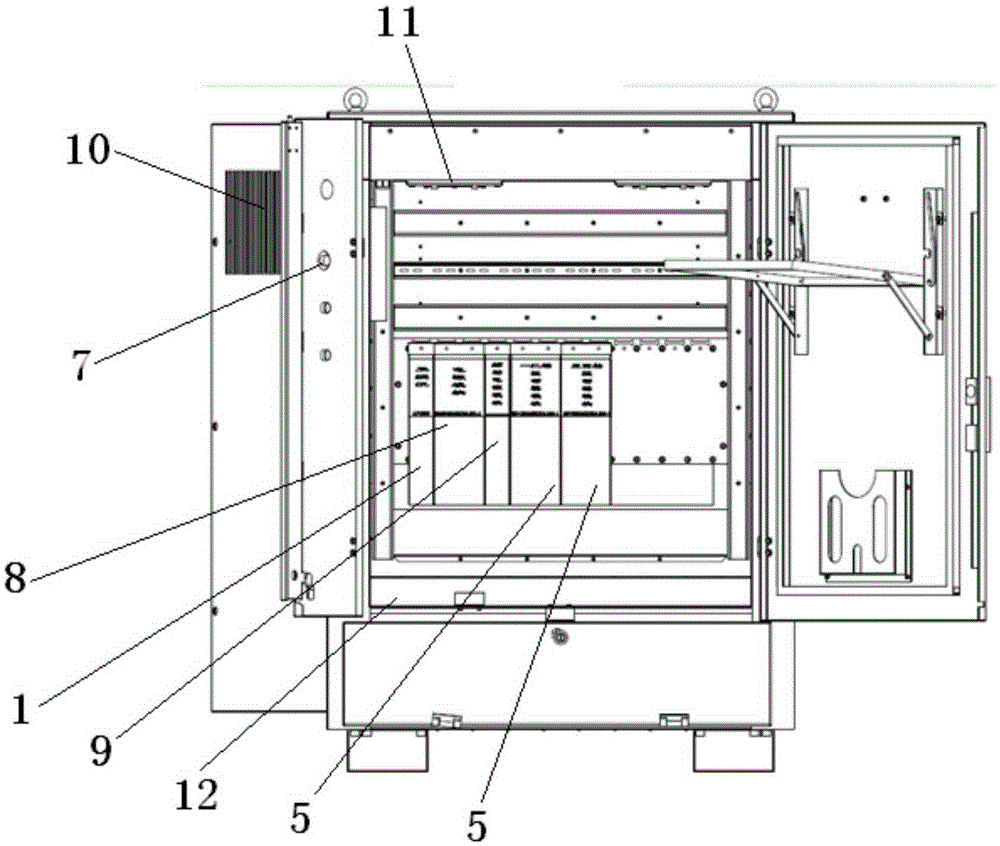

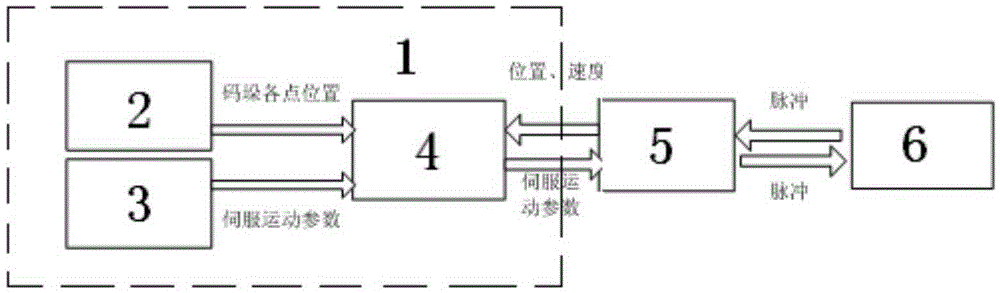

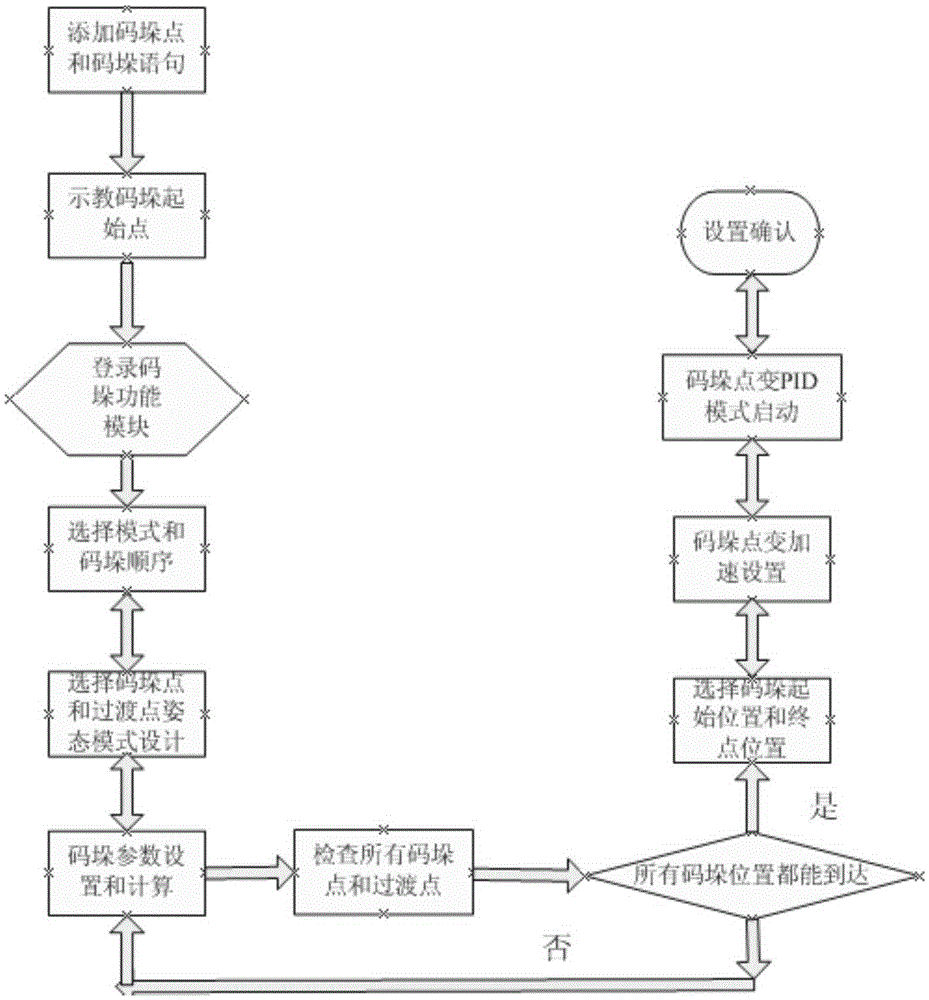

Electric control system of stacking industrial robot

ActiveCN103935771AEasy to prepareEasy to debugProgramme-controlled manipulatorStacking articlesElectric controlControl theory

The invention discloses an electric control system of a stacking industrial robot. The system is characterized in that the electric control system is built in a PC-BASE framework mode, namely a power supply module and an auxiliary power supply module are arranged in a cabinet and connected with an industrial personal computer and a servo drive respectively, and the industrial personal computer and the servo drive achieve two-way communication; a stacking register module, a variable acceleration PID register module and an internal motion control module are disposed in the industrial personal computer. By means of the structure, the PC-BASE framework mode is adopted, the structure is simplified, energy is saved, consumption is lowered, and motion variable acceleration time and PID functions of the robot can be extended so that stacking and unstacking time can be saved, and the electric control system has good stability and is high in cost performance.

Owner:EFORT INTELLIGENT EQUIP CO LTD

Managing registers in a processor to emulate a portion of a stack

ActiveUS7363475B2Memory adressing/allocation/relocationDigital computer detailsParallel computingStack register

Owner:VIA TECH INC

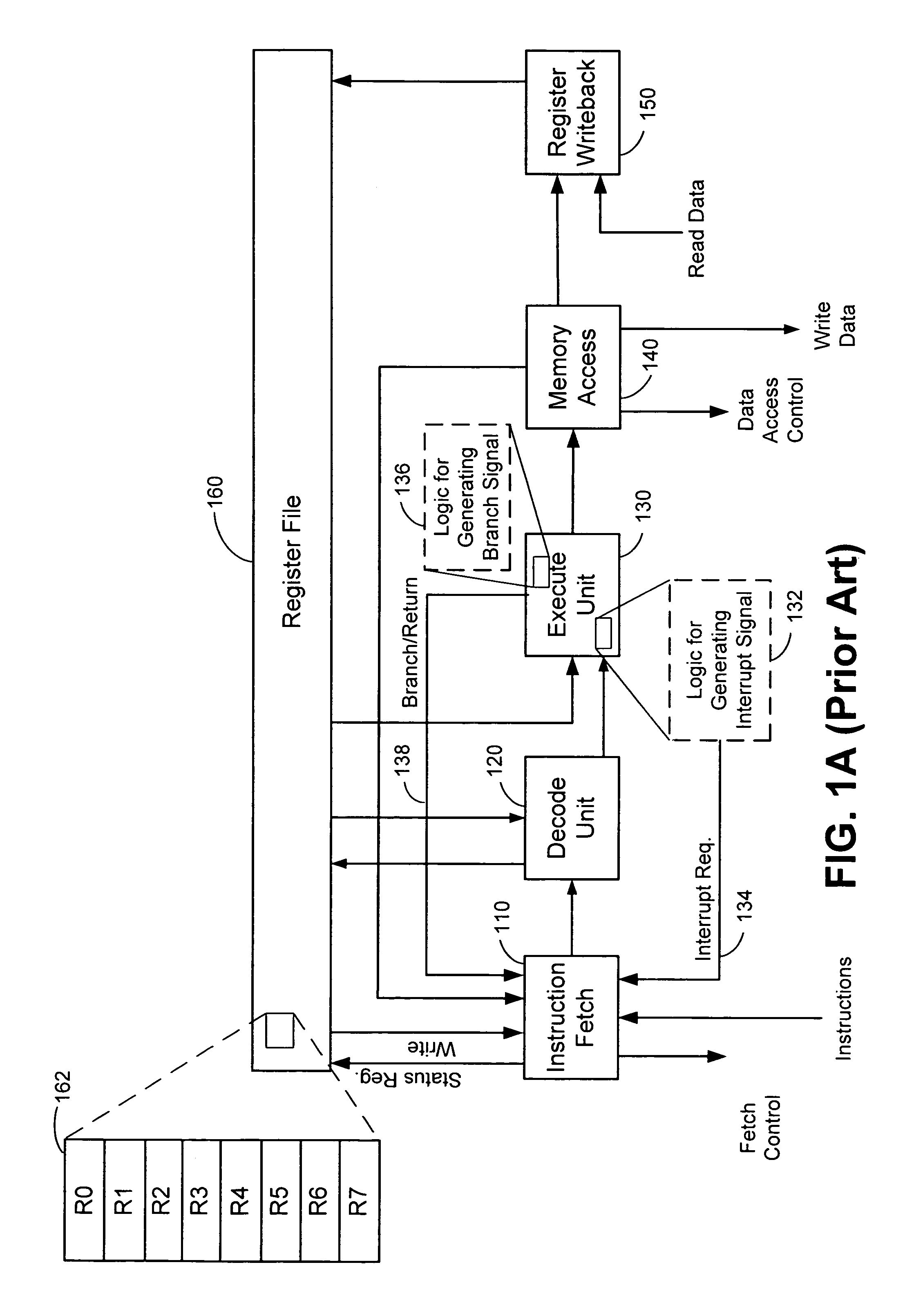

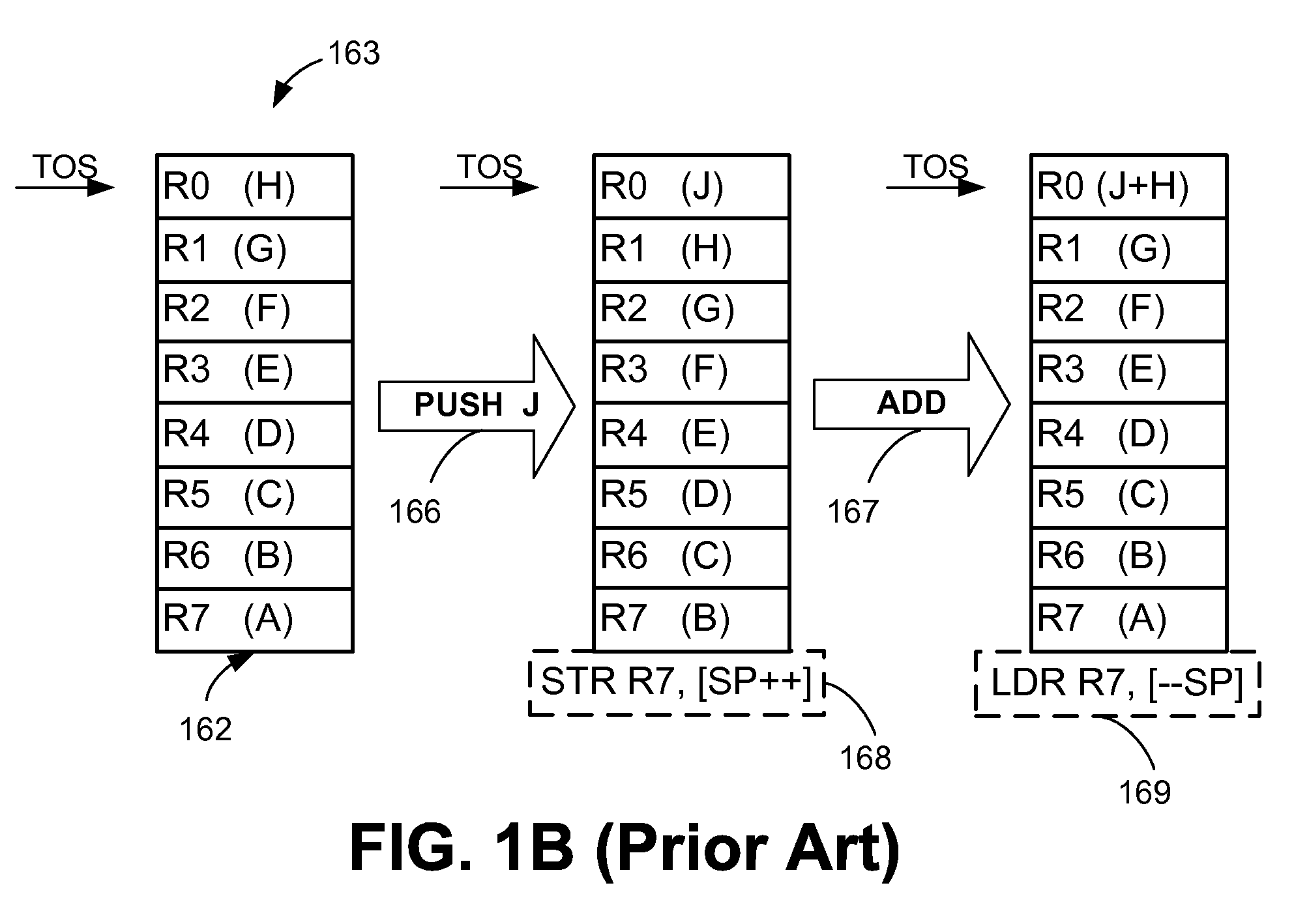

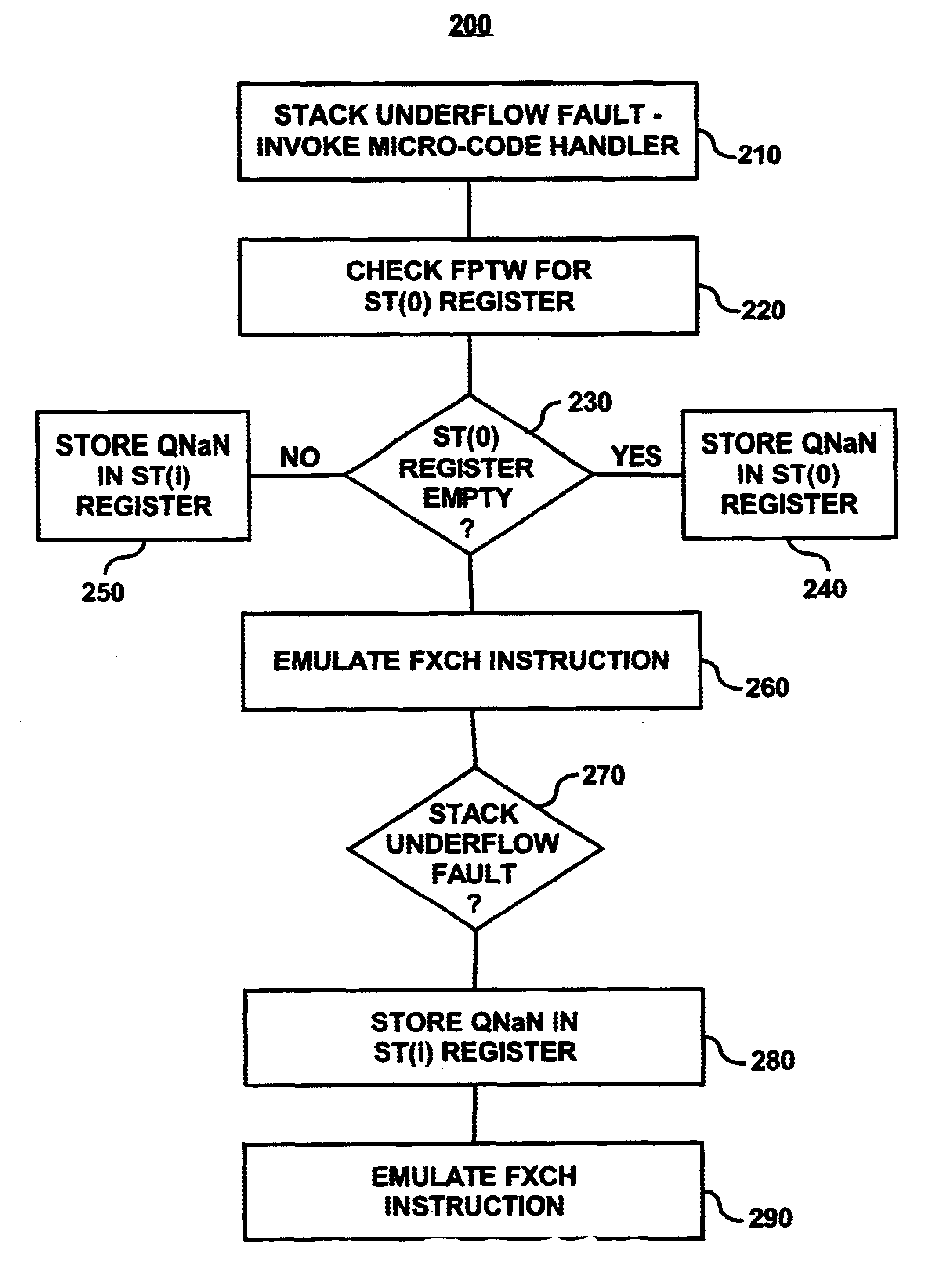

Methods and apparatus for exchanging the contents of registers

InactiveUS6668315B1Digital computer detailsConcurrent instruction executionComputerized systemRegister file

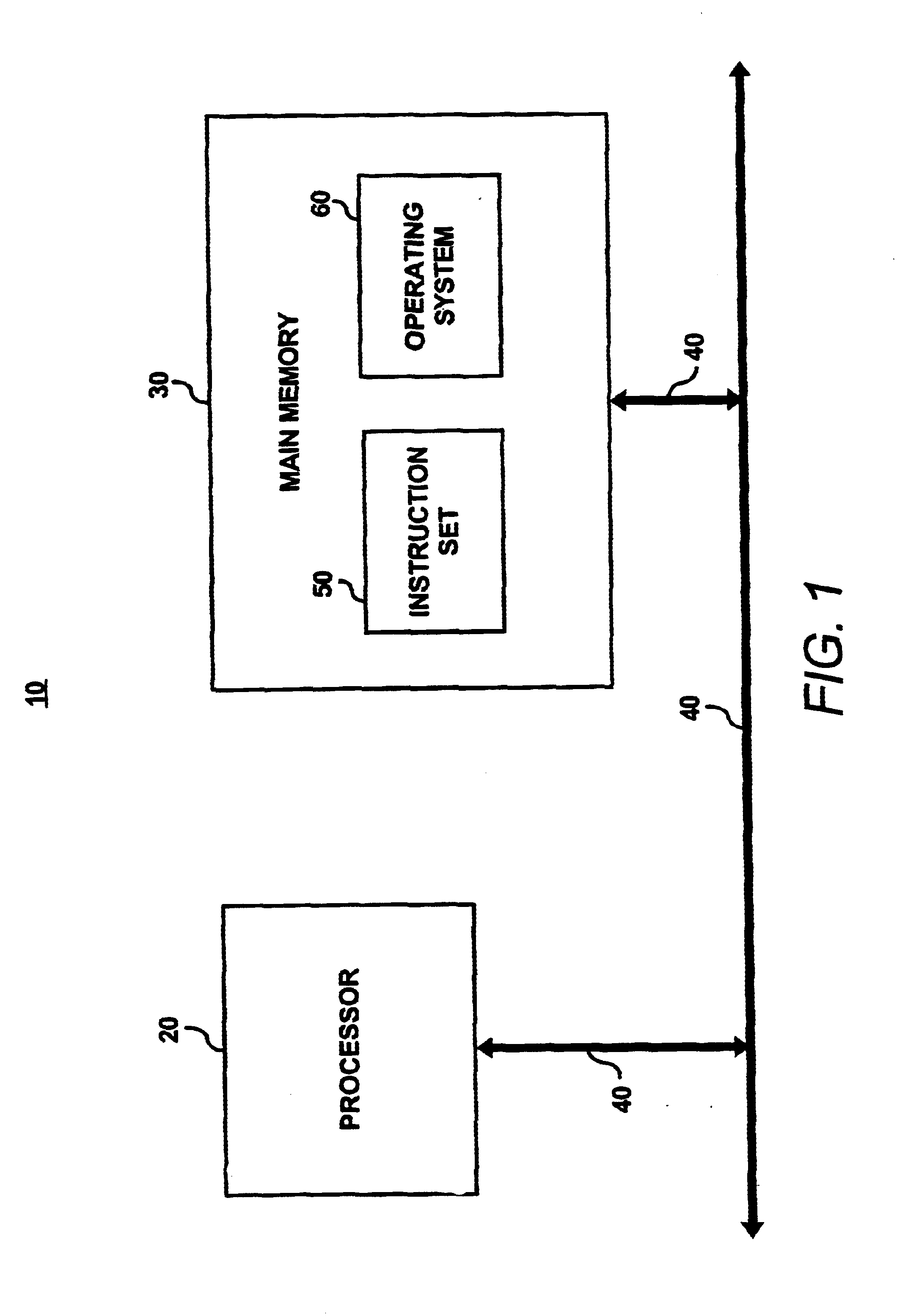

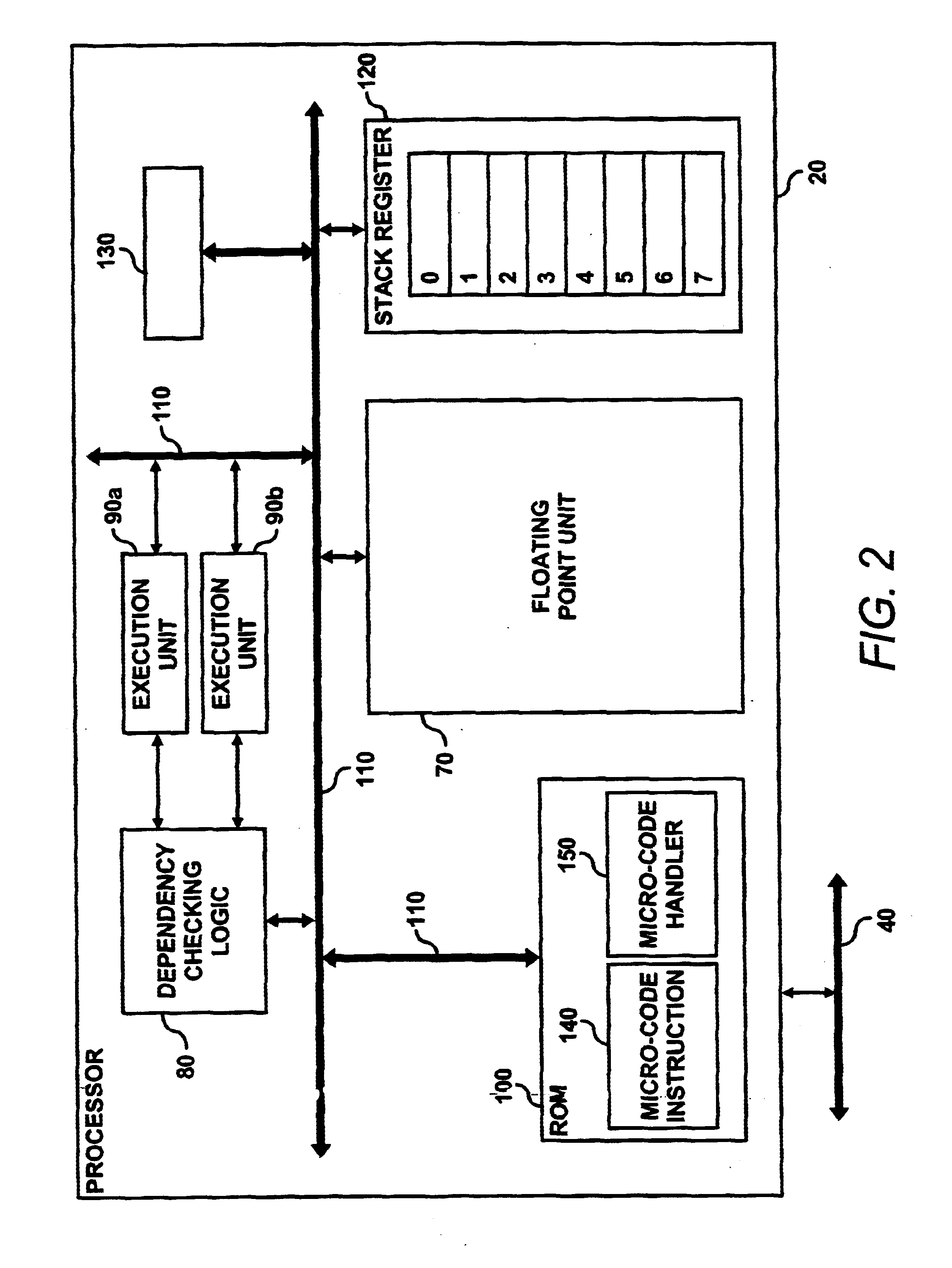

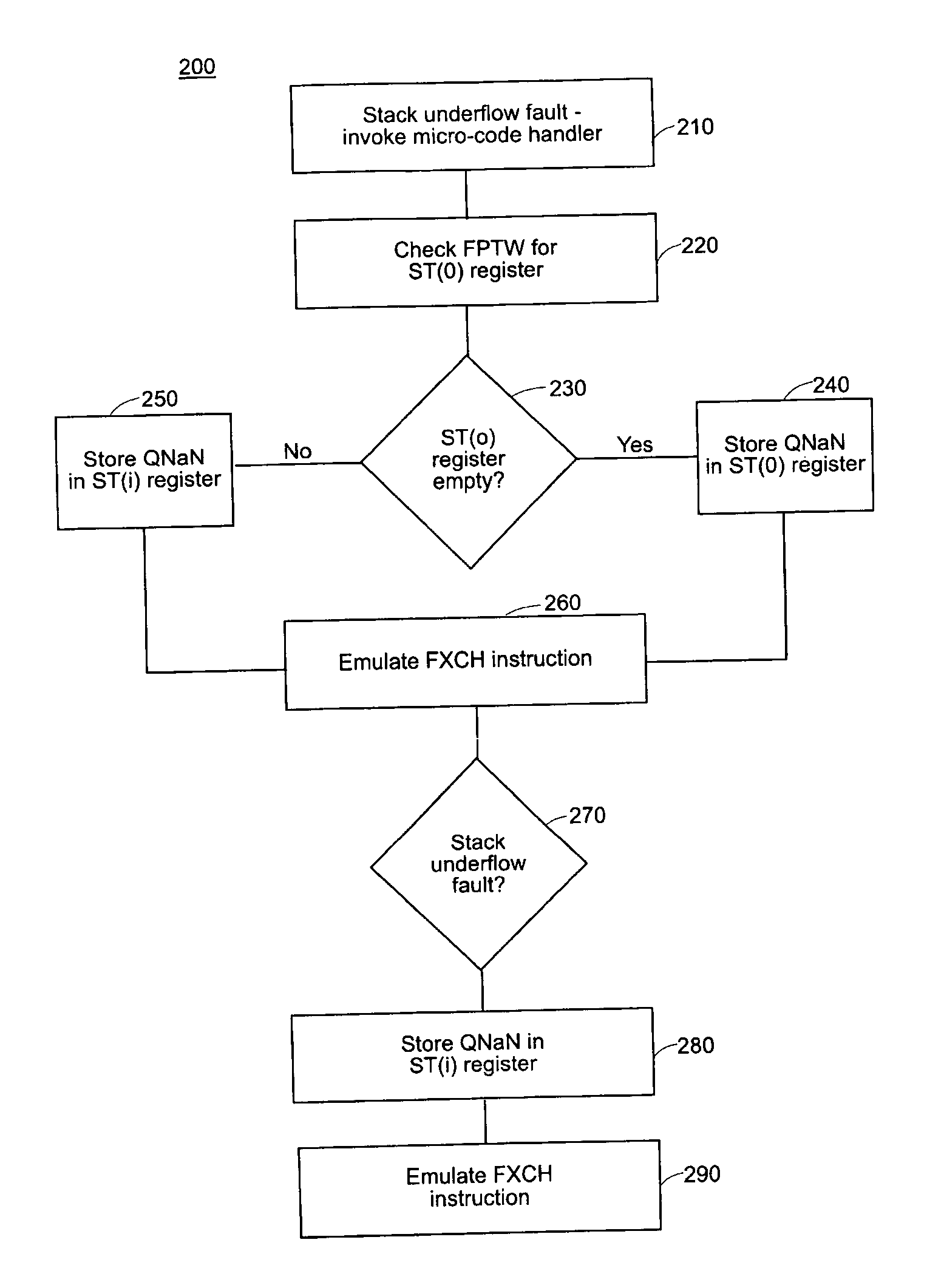

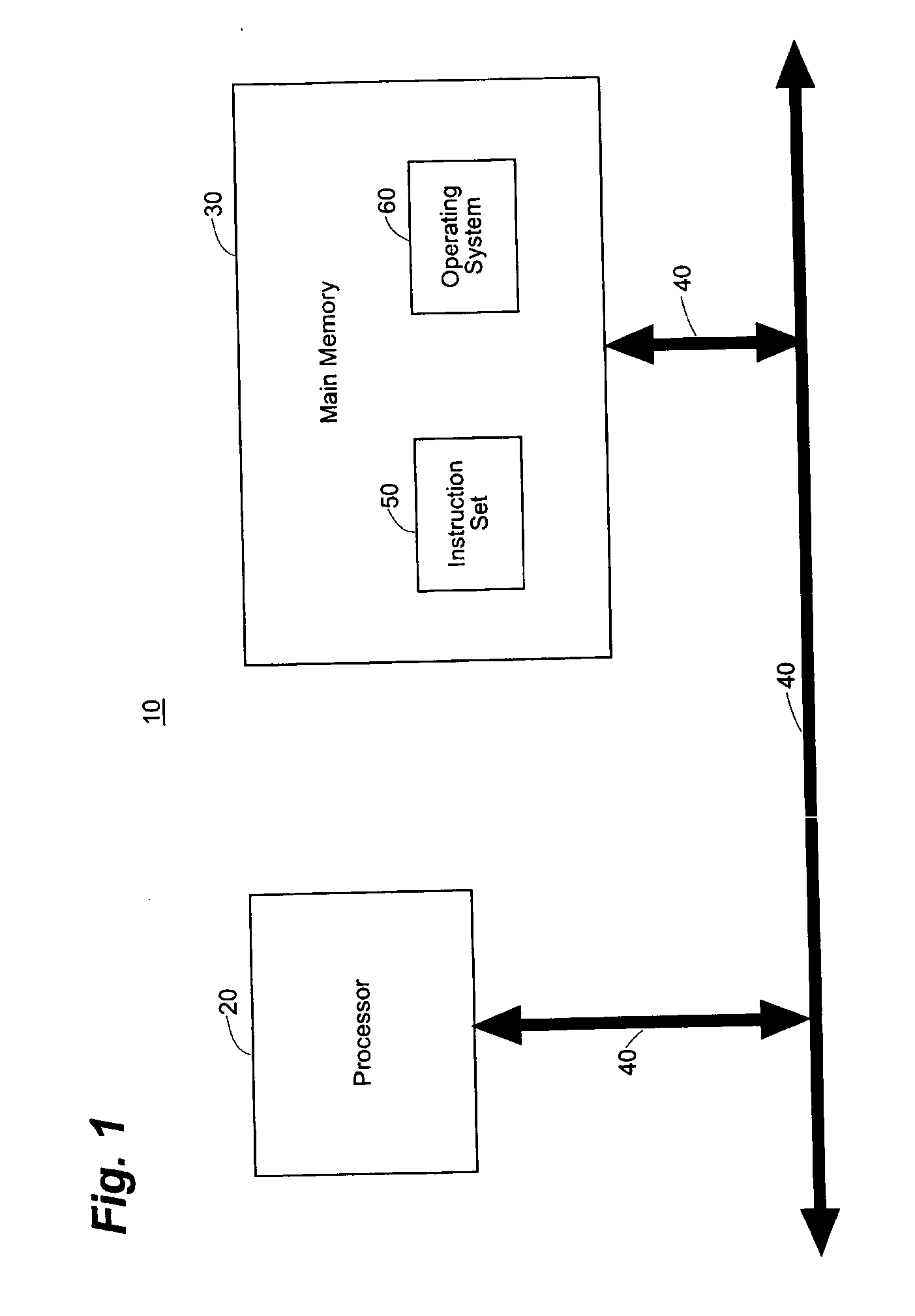

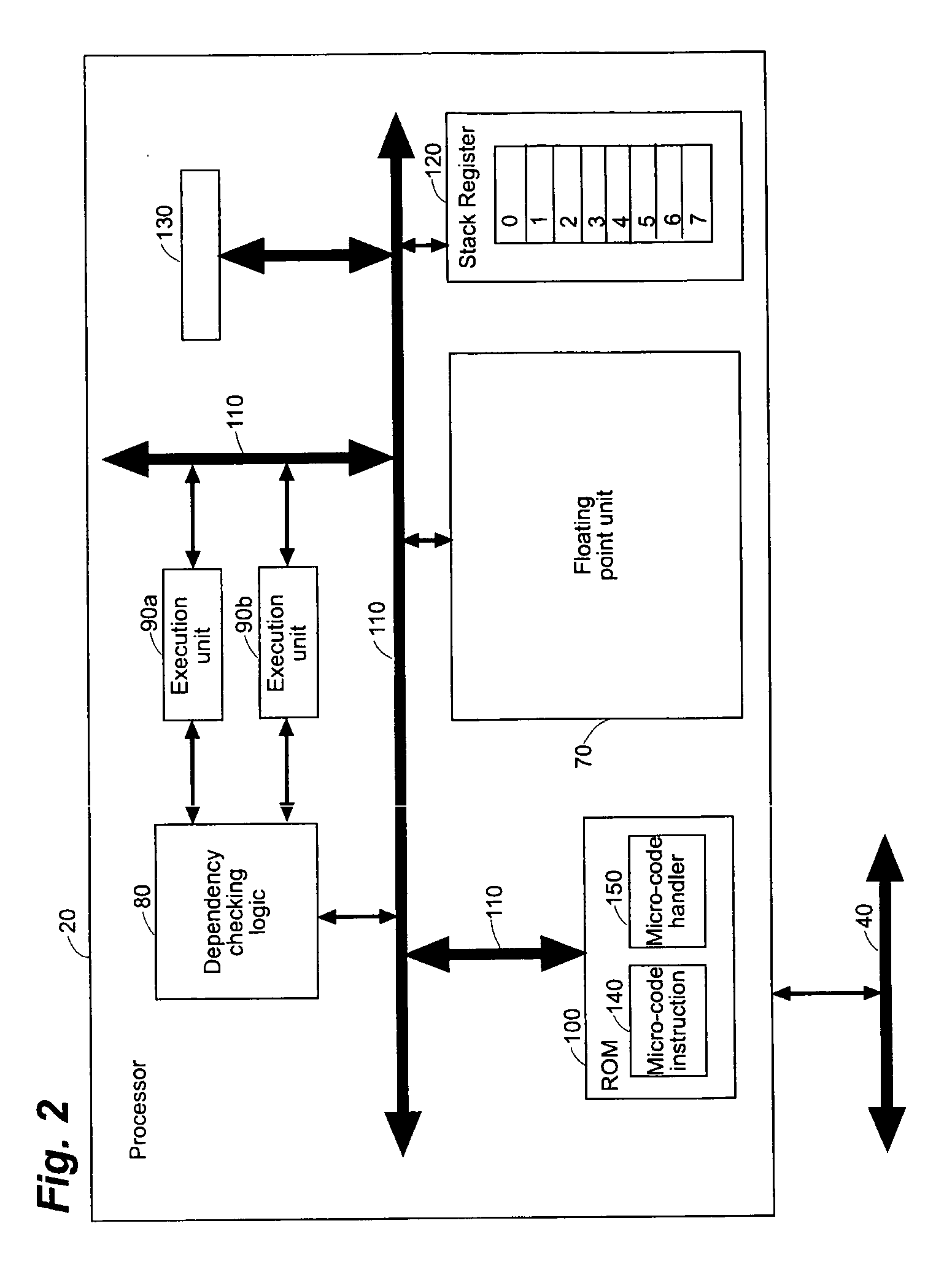

A processor based computer system having dependency checking logic and a register stack, wherein the system overrides the dependency logic such that move instructions associated with the stack registers may be executed in parallel. The system operates such that it can be determined whether a stack underflow exception has occurred and if it has, the move instructions can be flushed, and a micro-code handler algorithm invoked that operates to allow execution of the move instructions in parallel without a stack underflow exception.

Owner:HEWLETT PACKARD DEV CO LP

Extending a register file utilizing stack and queue techniques

ActiveUS7203820B2Digital computer detailsSpecific program execution arrangementsComputer scienceSoftware

In a set of registers, each individually addressable by register operations using a corresponding register identification, at least one register of the set of registers is an extended register having multiple storage locations. Values stored in the multiple storage locations are accessed, for example, according to the order in which they have been stored. Less than all of the multiple storage locations are accessible by a register operation at a given time. Older versions of software that do not recognize extended registers identify the extended register as having only one storage location. An extended register can be, for example, a stack register, a queue register, or a mixed register and values stored in the multiple storage locations are read and stored according to the characteristics of the register.

Owner:ORACLE INT CORP

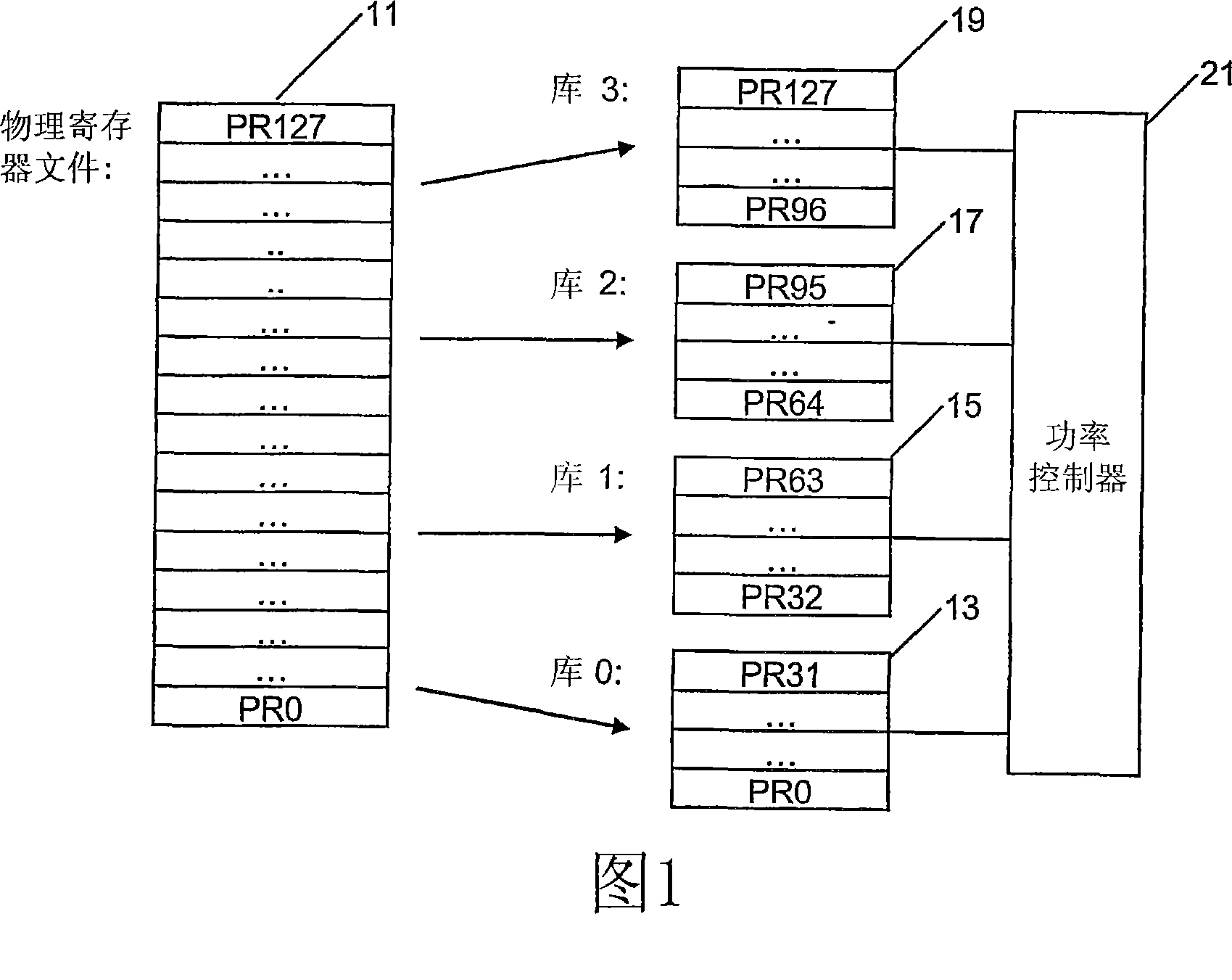

Reducing power by shutting down portions of a stacked register file

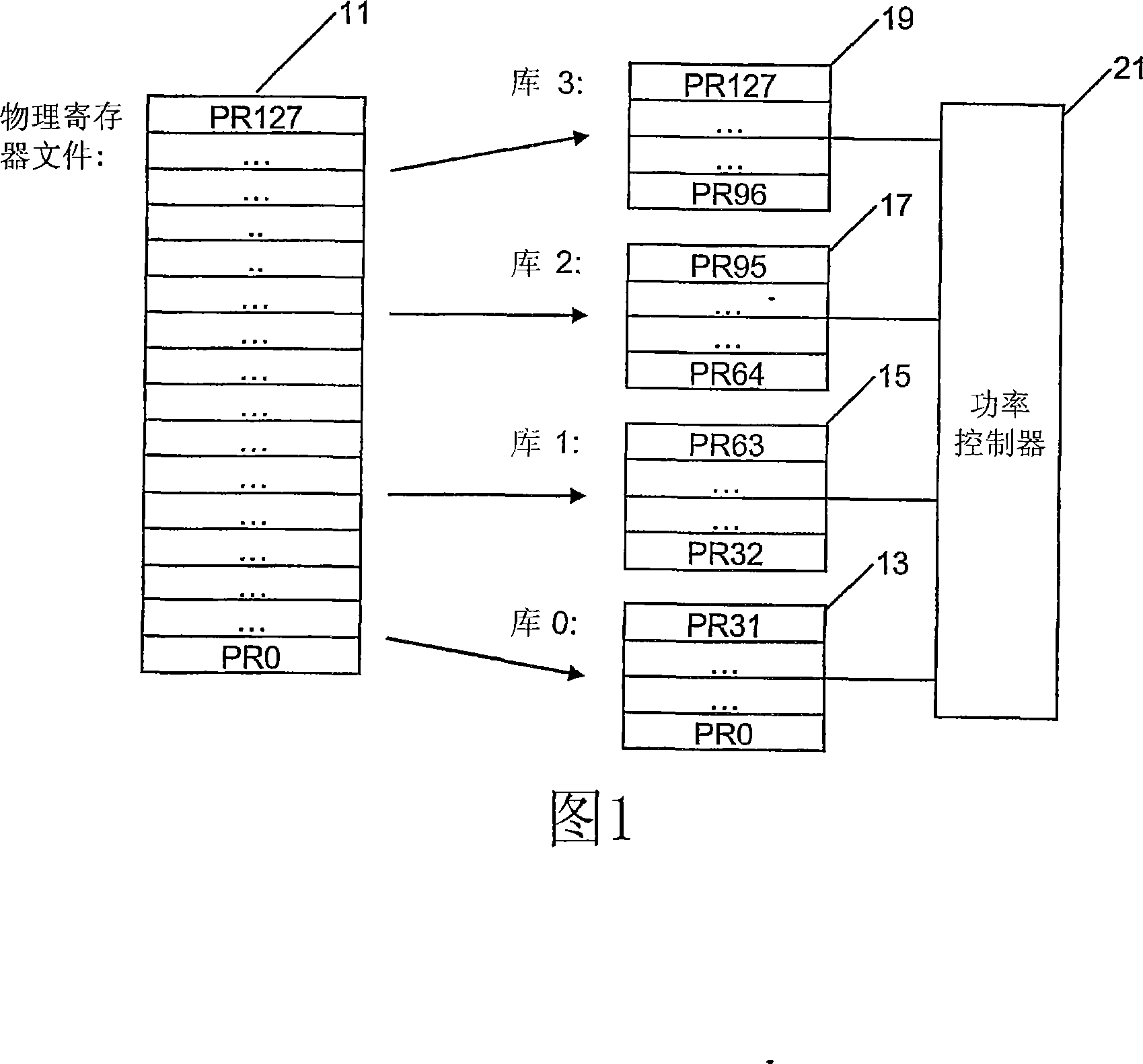

ActiveCN101160559ARegister arrangementsPower supply for data processingRegister allocationMulti processor

Many processor architectures include registers in the form of a stacked register file, for holding data used during execution of processing operations. As taught herein, the physical registers forming the stack are organized into banks. One or more of the banks is activated and deactivated, as needed to meet the demands of register allocations.

Owner:QUALCOMM INC

An electric control system for a palletizing industrial robot

ActiveCN103935771BEasy to prepareEasy to debugProgramme-controlled manipulatorStacking articlesElectric controlControl theory

Owner:EFORT INTELLIGENT EQUIP CO LTD

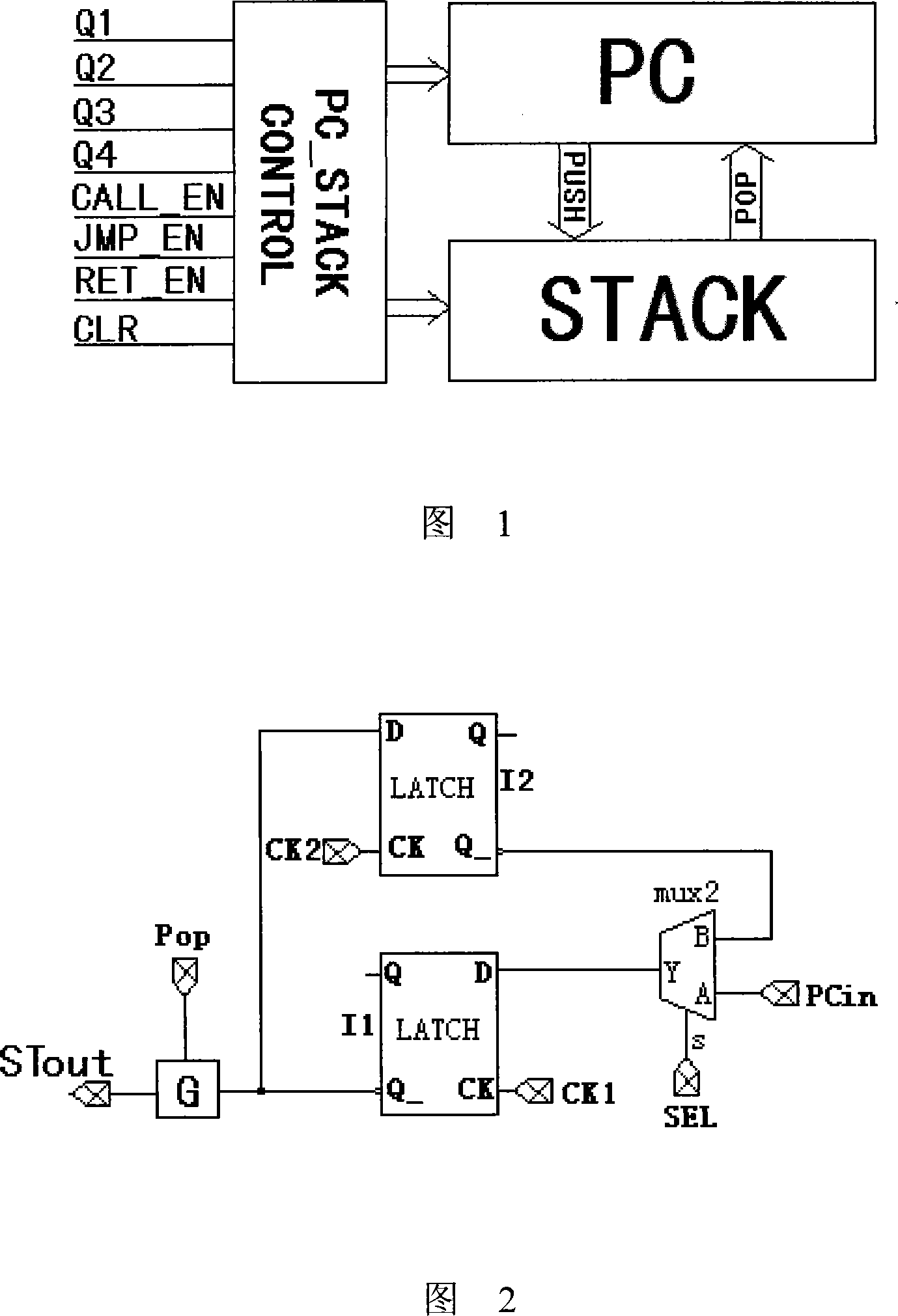

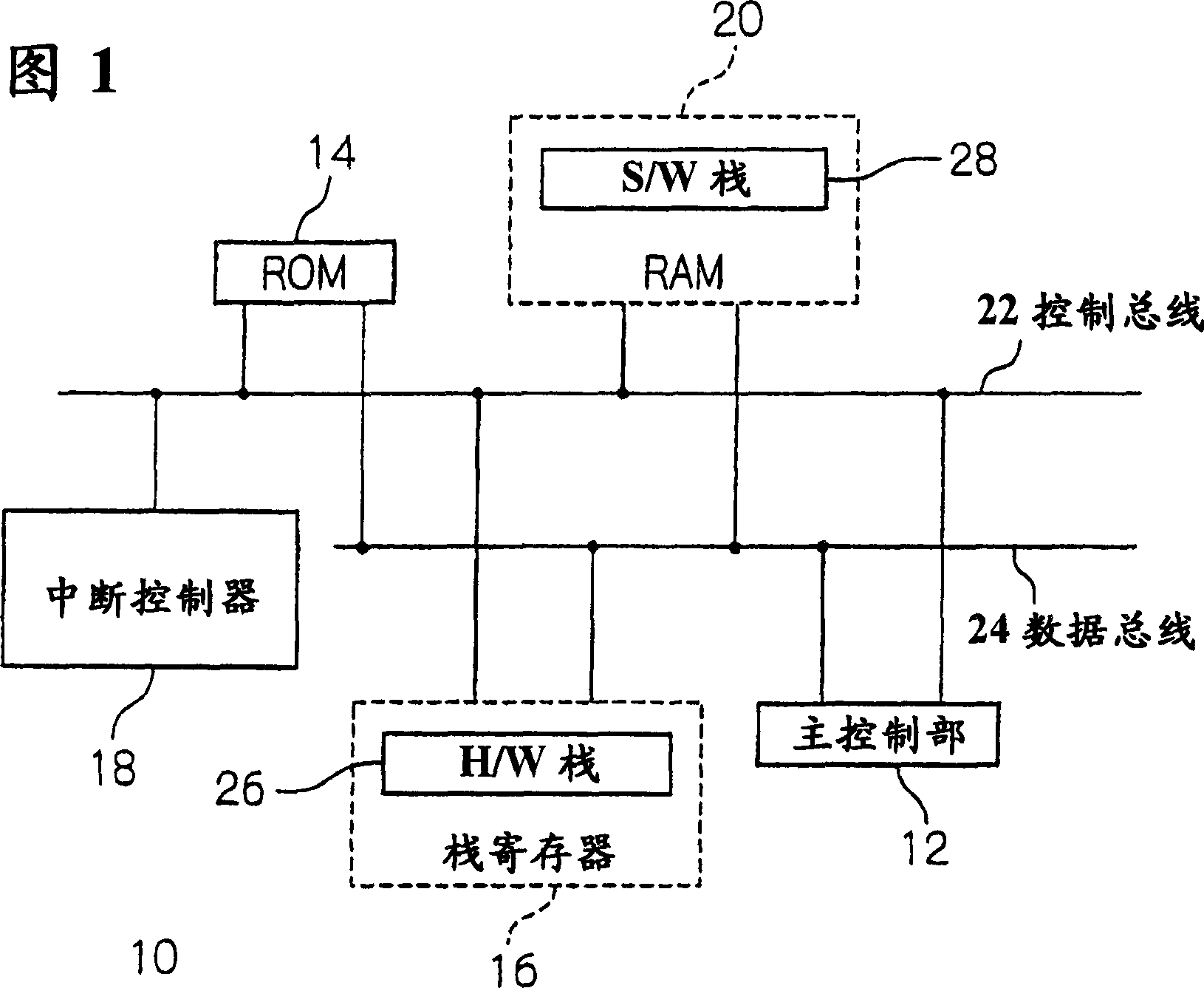

Stack control device and method

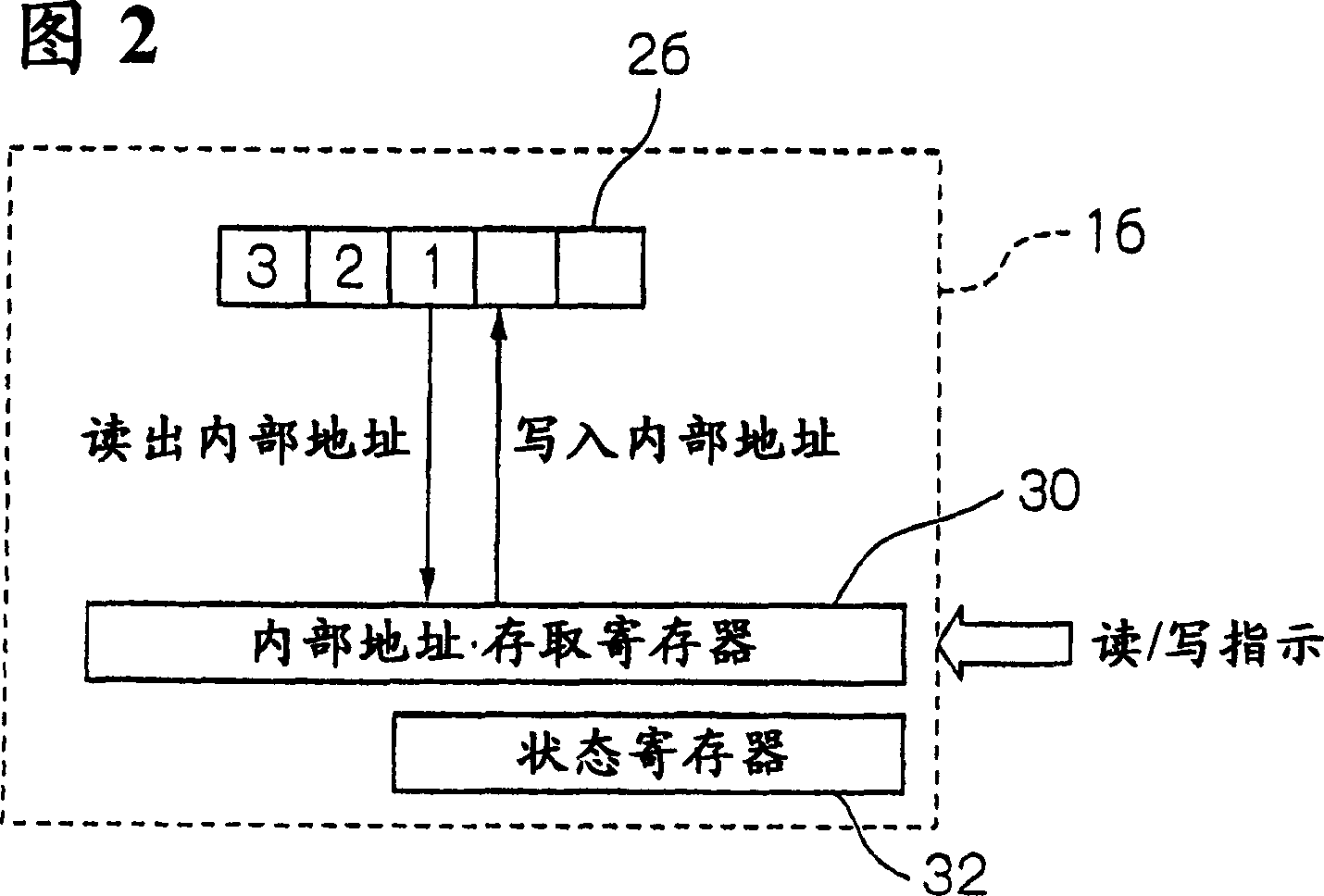

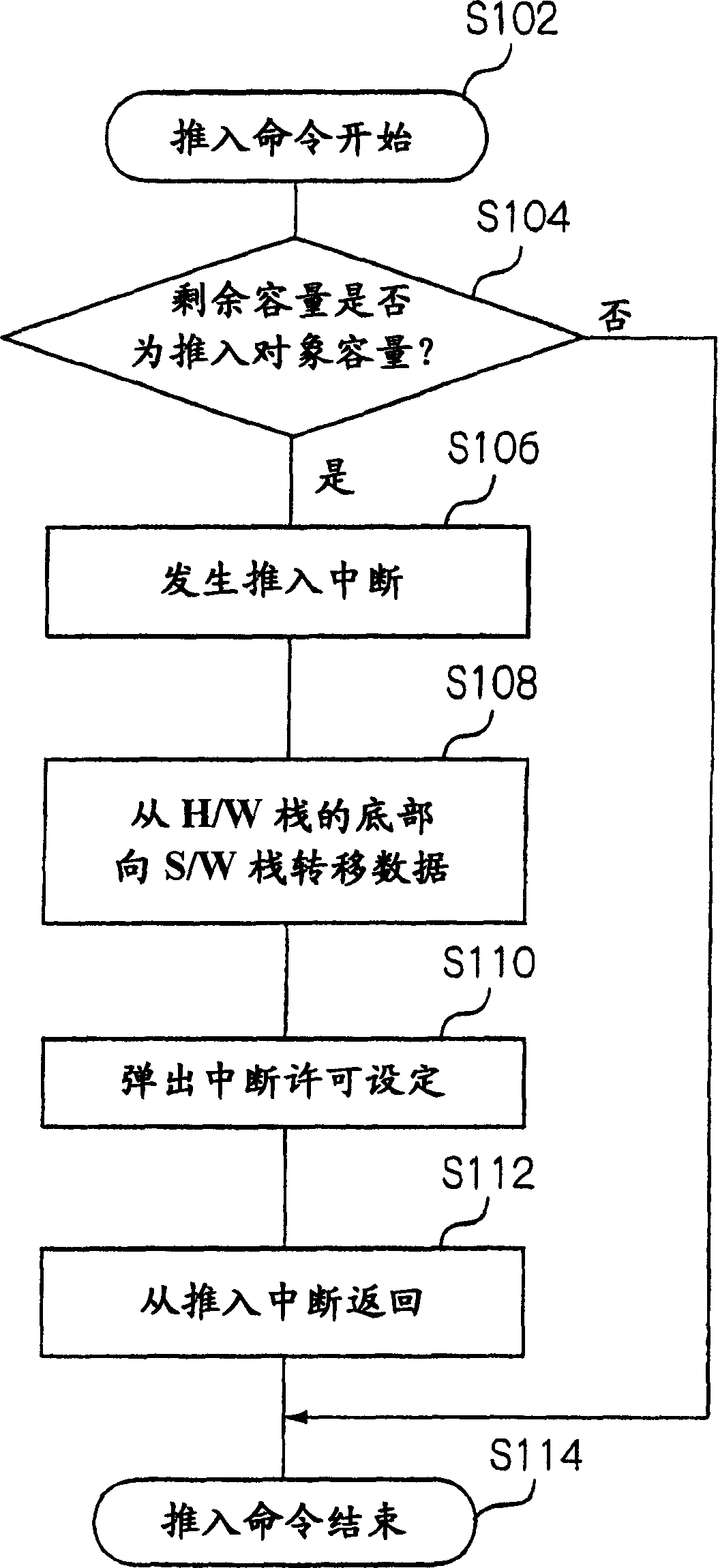

Provided are a stack control device and method thereof used when a microcomputer or the like executes a program. The stack control device 10, when the interrupt controller 18 monitors the capacity of the H / W stack 26, and when it becomes the push and pop object capacity, push and pop interrupts occur respectively and the main control unit 12 is notified, and the main control unit 12 responds to the push interrupt , take out the data from the bottom of the H / W stack 26, push into the S / W stack 28, and repeat this operation as the push interrupt process according to the prescribed transfer number, respond to the pop-up interrupt, pop the data from the S / W stack 28 and store it in the H / At the bottom of the W stack 26, this operation is repeated as a pop-up interrupt process according to the specified return number, so that even if the program that may exceed the capacity of the stack register is executed, it can continue to execute without program stop and runaway phenomenon.

Owner:OKI ELECTRIC IND CO LTD

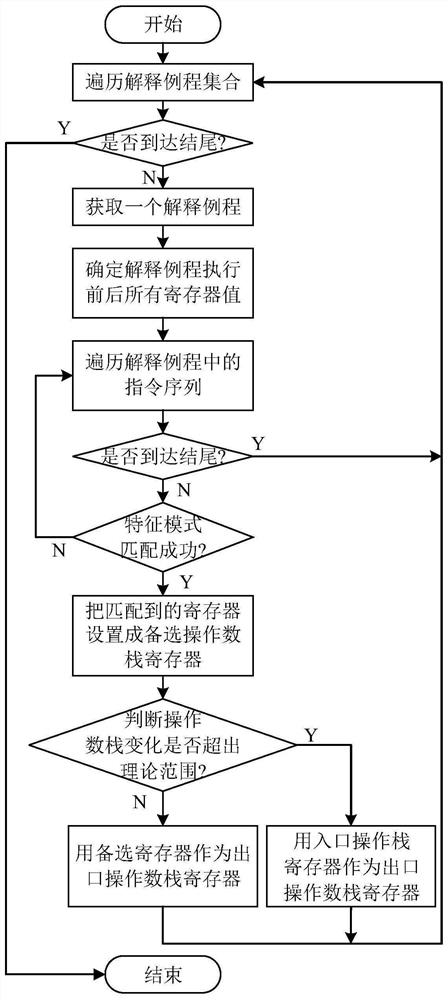

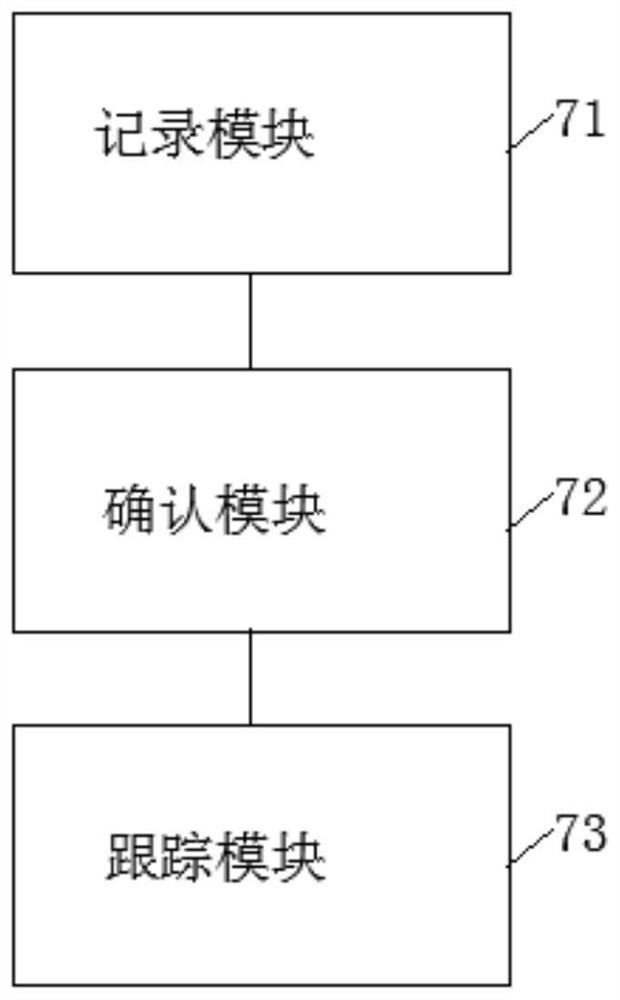

Operand stack register identification method, device and equipment and storage medium

PendingCN112199116AReverse engineeringSoftware simulation/interpretation/emulationEngineeringOperand

The embodiment of the invention discloses an operand stack register identification method, device and equipment and a storage medium, and the operand stack register identification method comprises thesteps: determining the values of all registers before and after each interpretation routine is executed, and recording the two groups of states through employing the registers as two containers of akey value; confirming a register corresponding to an operand stack before entering a virtual machine; and then tracking and analyzing the change condition of the operand stack to further determine a register corresponding to each interpretation routine operand stack; and determining the register corresponding to each interpretation routine operand stack according to the execution characteristics of the interpretation routines and the change range of the registers, thereby facilitating subsequent virtual instruction grammar and semantic analysis.

Owner:CHANGSHU INSTITUTE OF TECHNOLOGY

Reducing power by shutting down portions of a stacked register file

ActiveCN101160559BRegister arrangementsPower supply for data processingRegister allocationComputer architecture

Many processor architectures include registers in the form of a stacked register file, for holding data used during execution of processing operations. As taught herein, the physical registers forming the stack are organized into banks. One or more of the banks is activated and deactivated, as needed to meet the demands of register allocations.

Owner:QUALCOMM INC

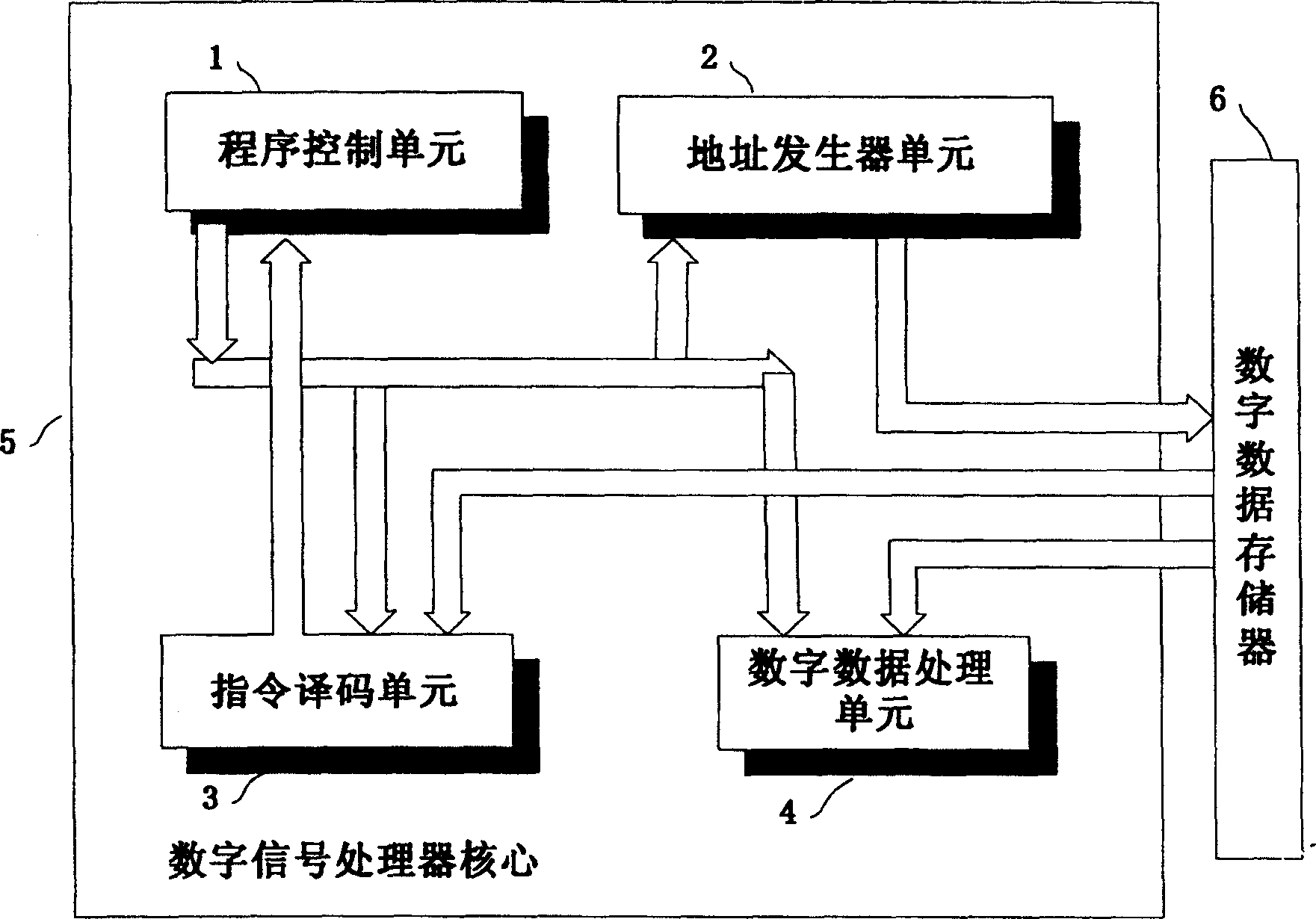

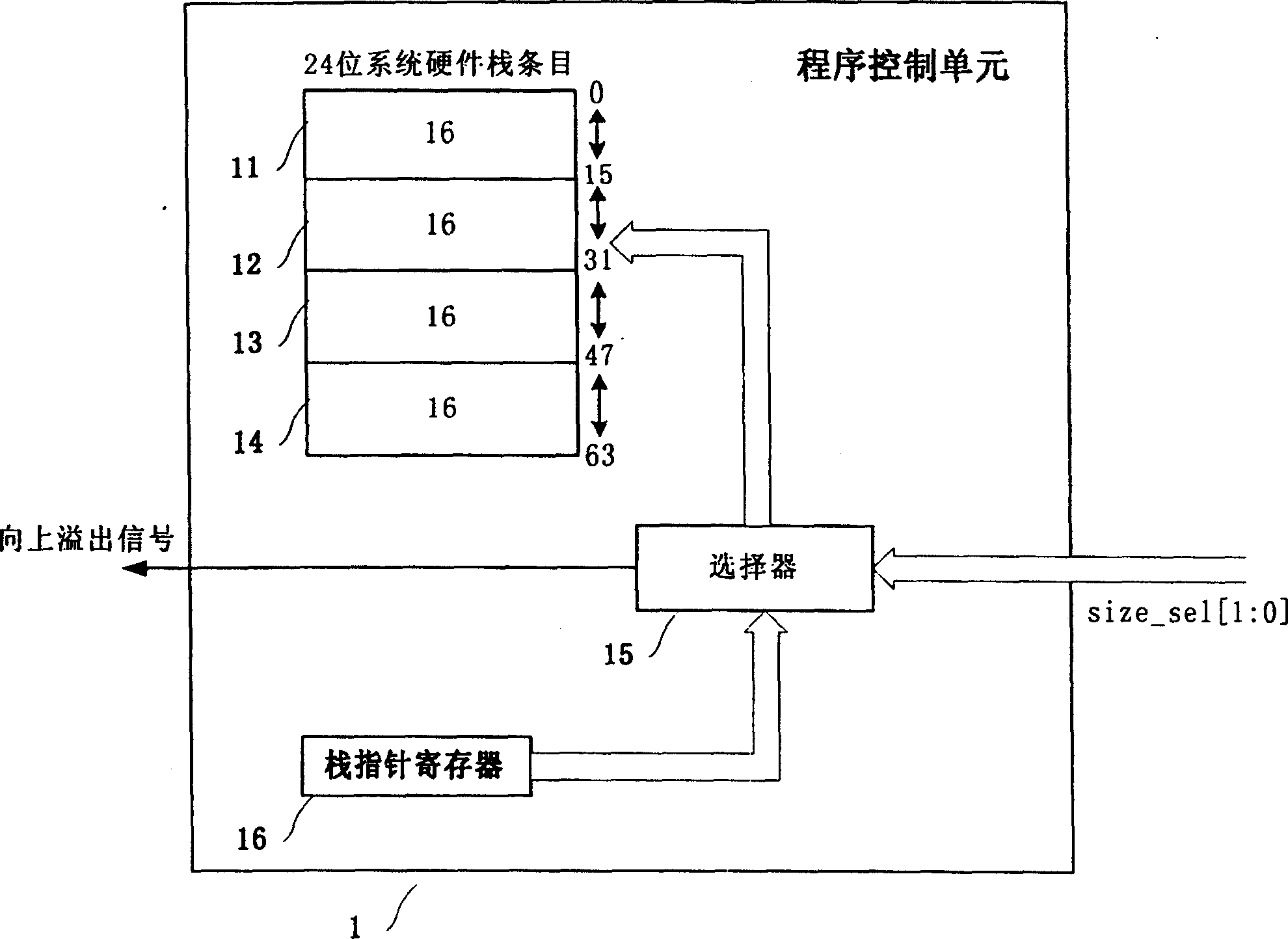

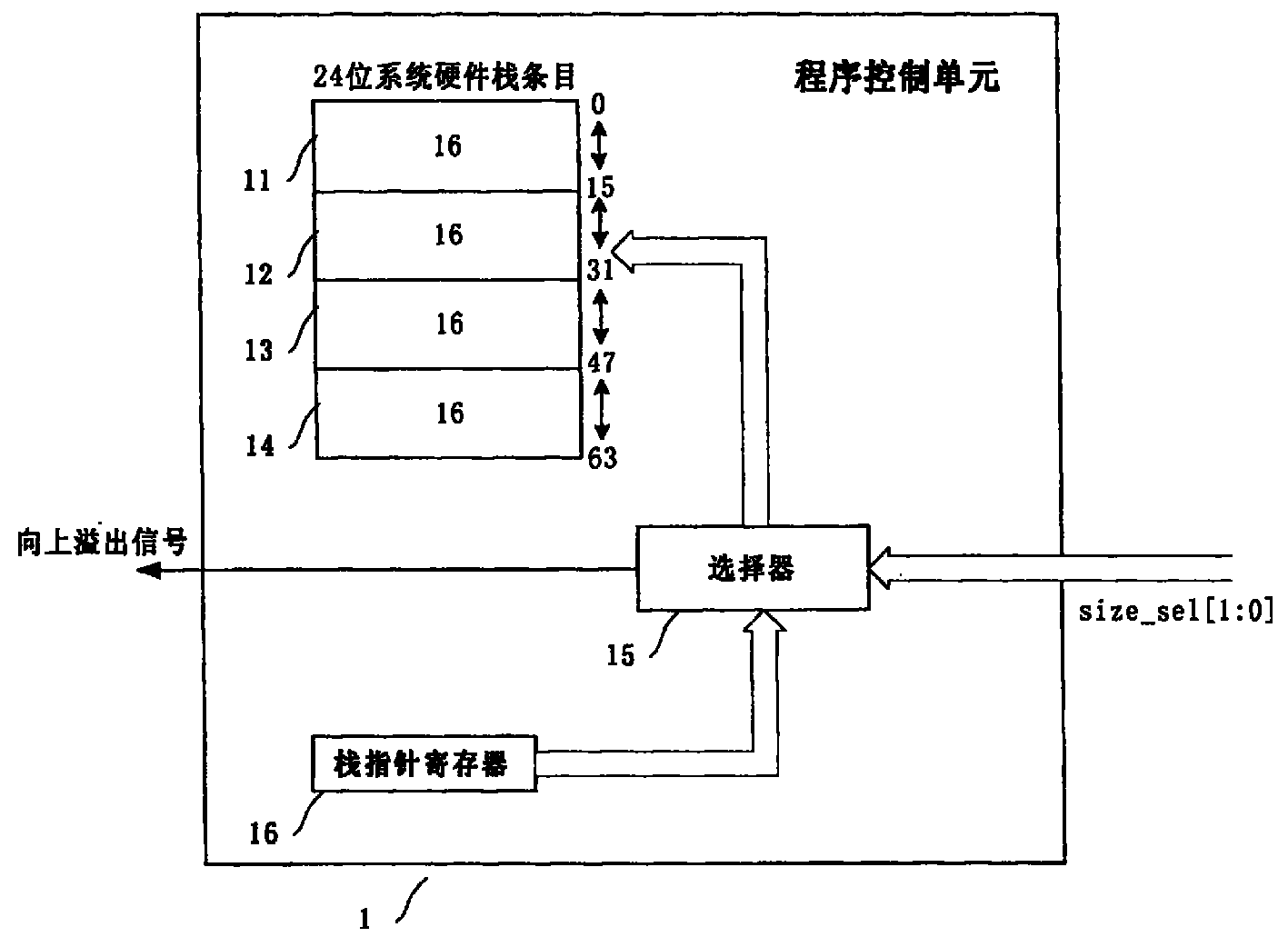

Digital signal processor with a reconfigurable system hardware stack

InactiveCN1255740CGood value for moneyLow costMachine execution arrangementsDigital signal processingAddress bus

Owner:SHANGHAI JIAOTONG UNIV +1

Secondary stack device and its data push and pop methods

InactiveCN101114236BSimple structureReduce areaMultiprogramming arrangementsConcurrent instruction executionControl signalControl data

The invention discloses a two-level stacking device, comprising a controller, a two-level stack register and an address bus module, wherein the controller generates a control signal for controlling the operations of pushing and popping data; the two-level stack The register is used to store the data pushed to the stack; the address bus module is connected with the second-level stack register through the address bus, and is characterized in that the second-level stack register is composed of a plurality of basic units. The invention also discloses a data stacking and stacking method of the two-level stacking device. The beneficial effect of the invention is that the address bus (PC) and the stack (STACK) are combined, and the data push and pop operations of the stack (STACK) are realized by utilizing the characteristics of the 4-phase clock, the circuit structure is simple, the control is convenient, and the circuit area Small, effectively reducing the cost.

Owner:SUZHOU HUAXIN MICROELECTRONICS

Method and apparatus for exchanging the contents of registers

InactiveUS20040068641A1Digital computer detailsConcurrent instruction executionComputerized systemRegister file

A processor based computer system having dependency checking logic and a register stack, wherein the system overrides the dependency logic such that move instructions associated with the stack registers may be executed in parallel. The system operates such that it can be determined whether a stack underflow exception has occurred and if it has, the move instructions can be flushed, and a micro-code handler algorithm invoked that operates to allow execution of the move instructions in parallel without a stack underflow exception.

Owner:SAFFORD KEVIN DAVID +1

Calculator capable of recovering cleared values

InactiveUS6865586B2Digital computer detailsInput/output processes for data processingFLAGS registerEmbedded system

A calculator comprises an input having an UNDO key for recovering cleared values. When displayed data or recorded data of memory is cleared by pressing one of deletion keys, the cleared data is pushed into a stack register. A flag register is set when the displayed data or recorded data is cleared by a deletion key. When the UNDO key is pressed and the flag register indicates that the displayed data or recorded data was cleared by the deletion key, a data entry is popped from the stack register, so as to recover the cleared value.

Owner:KINPO ELECTRONICS