Digital signal processor with a reconfigurable system hardware stack

A digital signal and reconstruction system technology, applied in the direction of electrical digital data processing, instruments, machine execution devices, etc., can solve problems such as unfavorable application programs and adjustments, and achieve the effect of saving costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

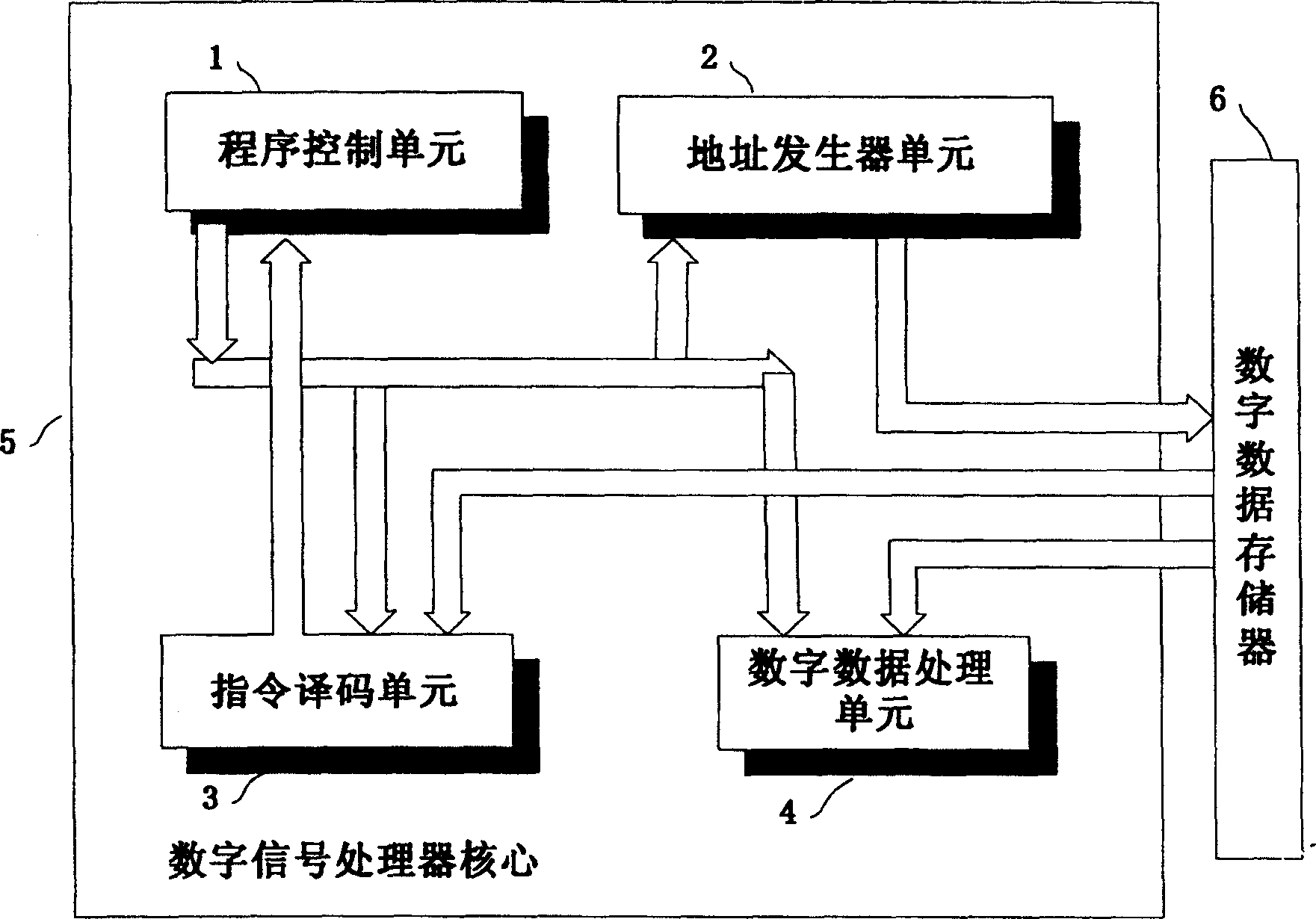

[0010] like figure 1 As shown, the digital signal processor core 5 has a program control unit 1 , an address generator unit 2 , an instruction decoding unit 3 , and a digital data processing unit 4 , and a digital data memory 6 is connected to the digital signal processor core 5 . The instruction decoding unit 3 translates the instruction code into the control signal representing the meaning of the instruction inside the digital signal processor core 5, and these described control signals are connected to the program control unit 1, and the program control unit 1 sends the address generation unit 2, the instruction translation The code unit 3 and the digital data processing unit 4 send out the control signals needed to control the work of these modules. The digital data processing unit receives the data from the digital data memory 6 and performs operations on it. The address generator unit 2 performs address calculation, and the result of the address calculation is connected...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More