Bus signal analysis tool for Flash storage chip

A bus signal and memory chip technology, applied in the field of Flash memory chip bus signal analysis tools, can solve problems such as unsatisfactory, and achieve the effect of simple operation and large storage depth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

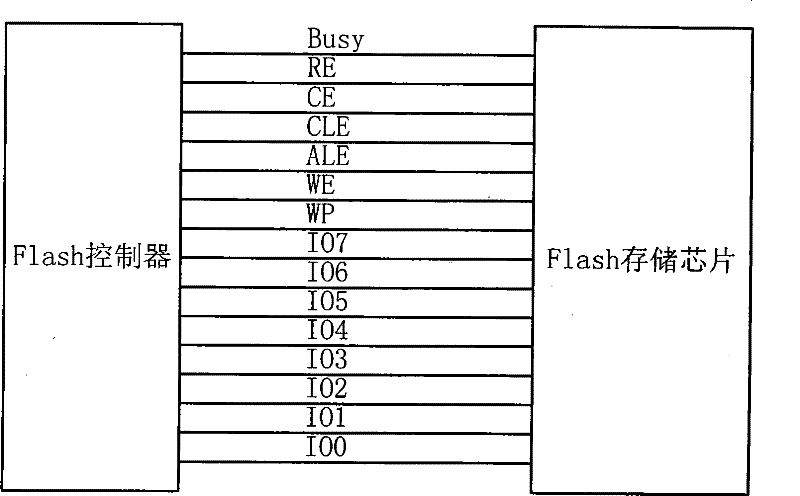

[0033] The application of the flash memory chip bus signal analysis tool of the present invention is very simple, as long as the flash bus signal sampling probe (eg connector, wire, probe, etc.) of the present invention is directly connected to the corresponding flash bus signal. That is to say, the present invention only needs to include two parts in practical application:

[0034] (1) The analyzed object related to the Flash memory chip.

[0035] (2) Flash bus signal analysis tool.

[0036] In order to achieve such a requirement, the Flash bus signal analysis tool must have the following five functions:

[0037] (1) Sampling the Flash bus signal of the object to be analyzed, the Flash bus signal analysis tool is connected to the Flash bus signal of the object to be analyzed through sampling probes (such as connectors, wires, probes, etc.), and according to a certain frequency ( Generally greater than twice the frequency of the Flash bus) to sample it.

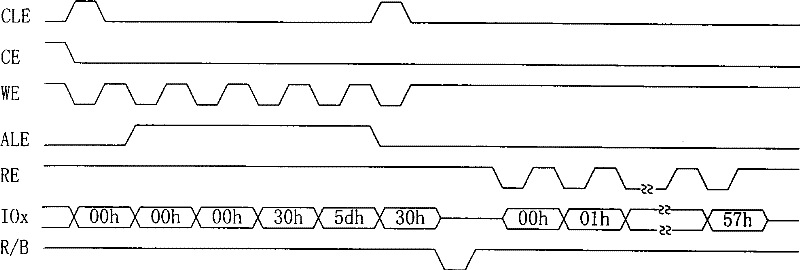

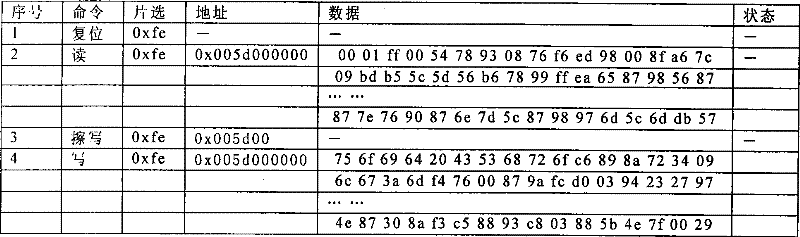

[0038] (2) Analyze...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More