Method and apparatus for generating clock signals for quadrature sampling

A clock signal, sampling clock technology, applied in the field of receivers, can solve the problems of power consumption, VCO expensive, uneconomical, etc., and achieve the effect of reducing cost and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

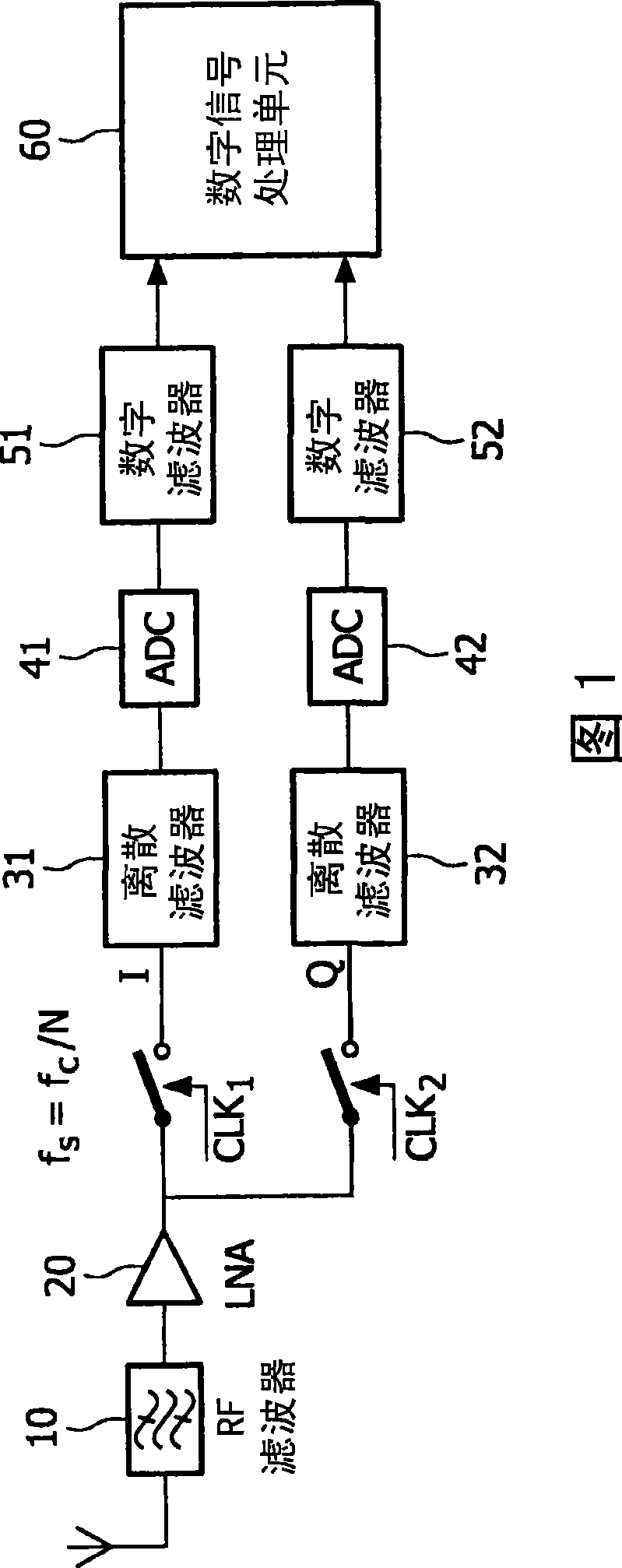

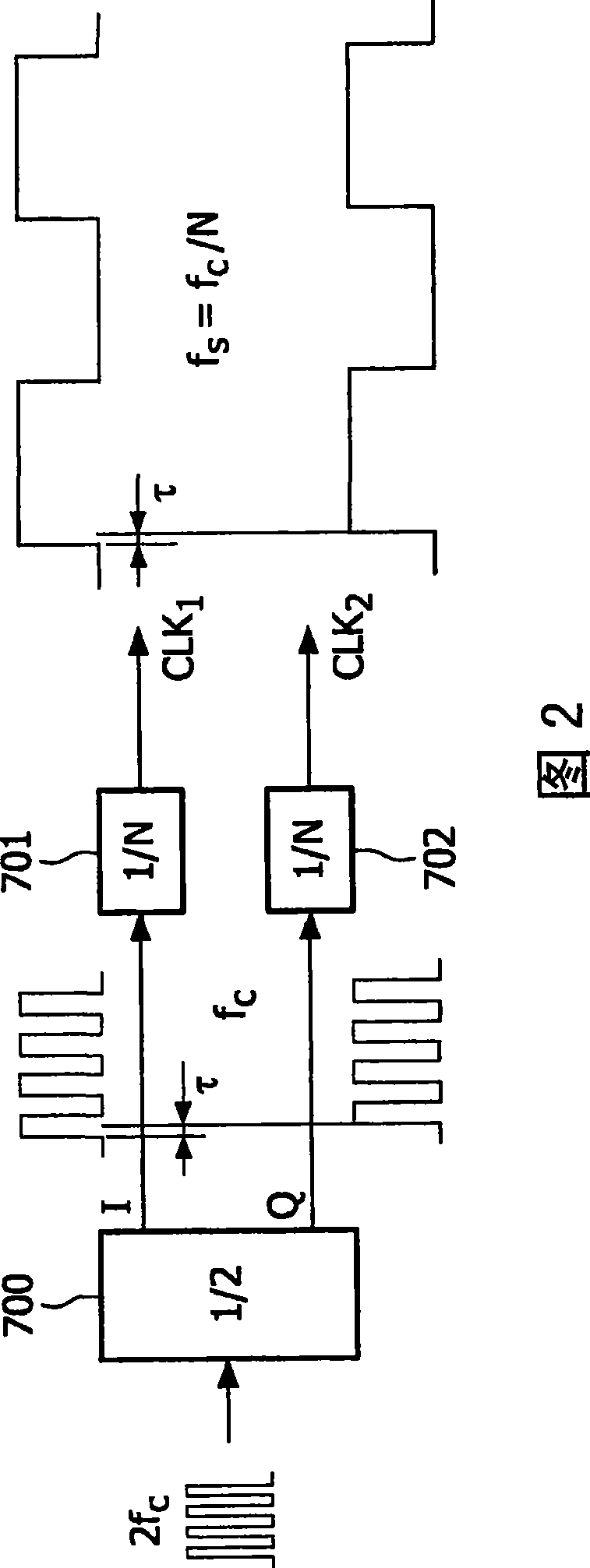

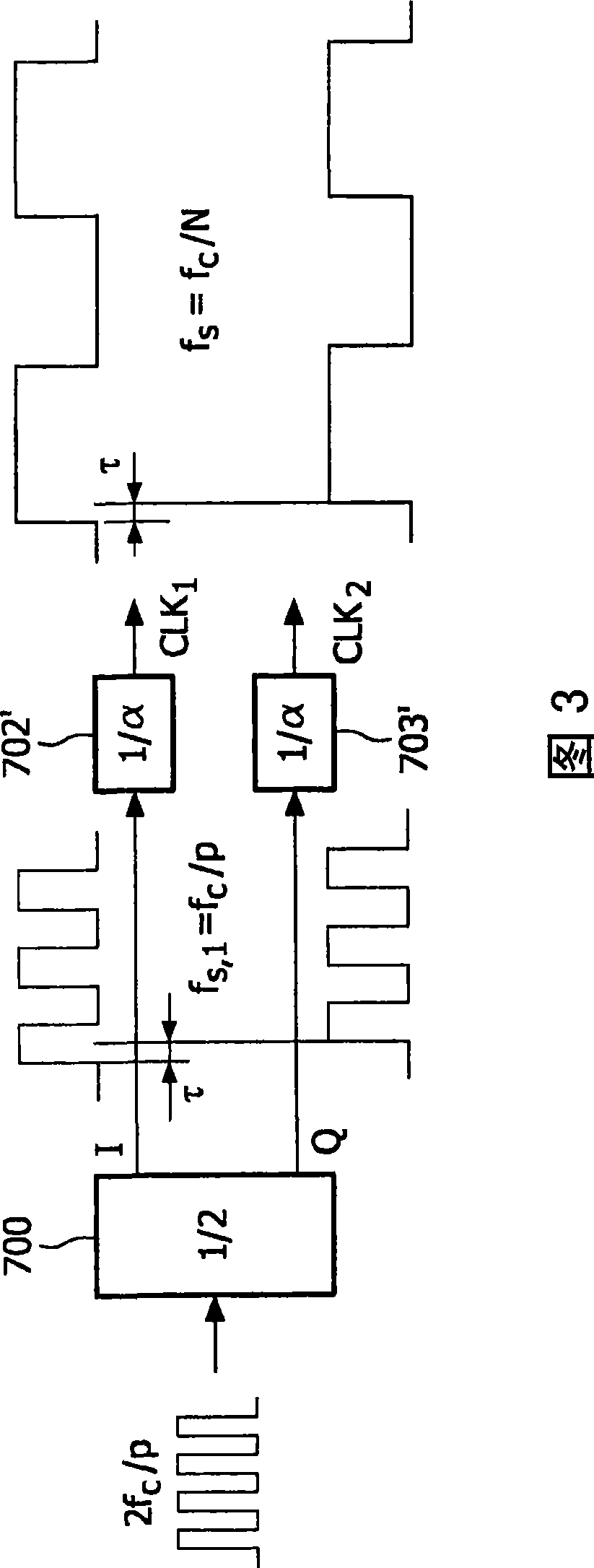

[0025] For a quadrature sampling receiver, two clock signals with a 90° phase shift need to be provided so that quadrature sampling is performed separately on the received RF signal. In order to reduce the frequency of the initial clock signal of the traditional clock signal generating device shown in Fig. 2 and at the same time ensure that the two clock signals obtained by dividing the frequency of the initial clock signal maintain a 90° phase shift on the carrier frequency, the present invention proposes A new solution is proposed to generate the clock signal, which will be described in detail with reference to FIG. 3 .

[0026] In a quadrature sampling receiver, if the carrier frequency of the signal is f c , and the subsampling factor is N, then the sampling frequency will be f c = f s N . Since N is an integer, N can be expressed as the product ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More