Data processing hardware for non-negative matrix factorisation

A technology of data processors and processors, applied in the fields of hardware accelerators and non-negative matrix factorization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

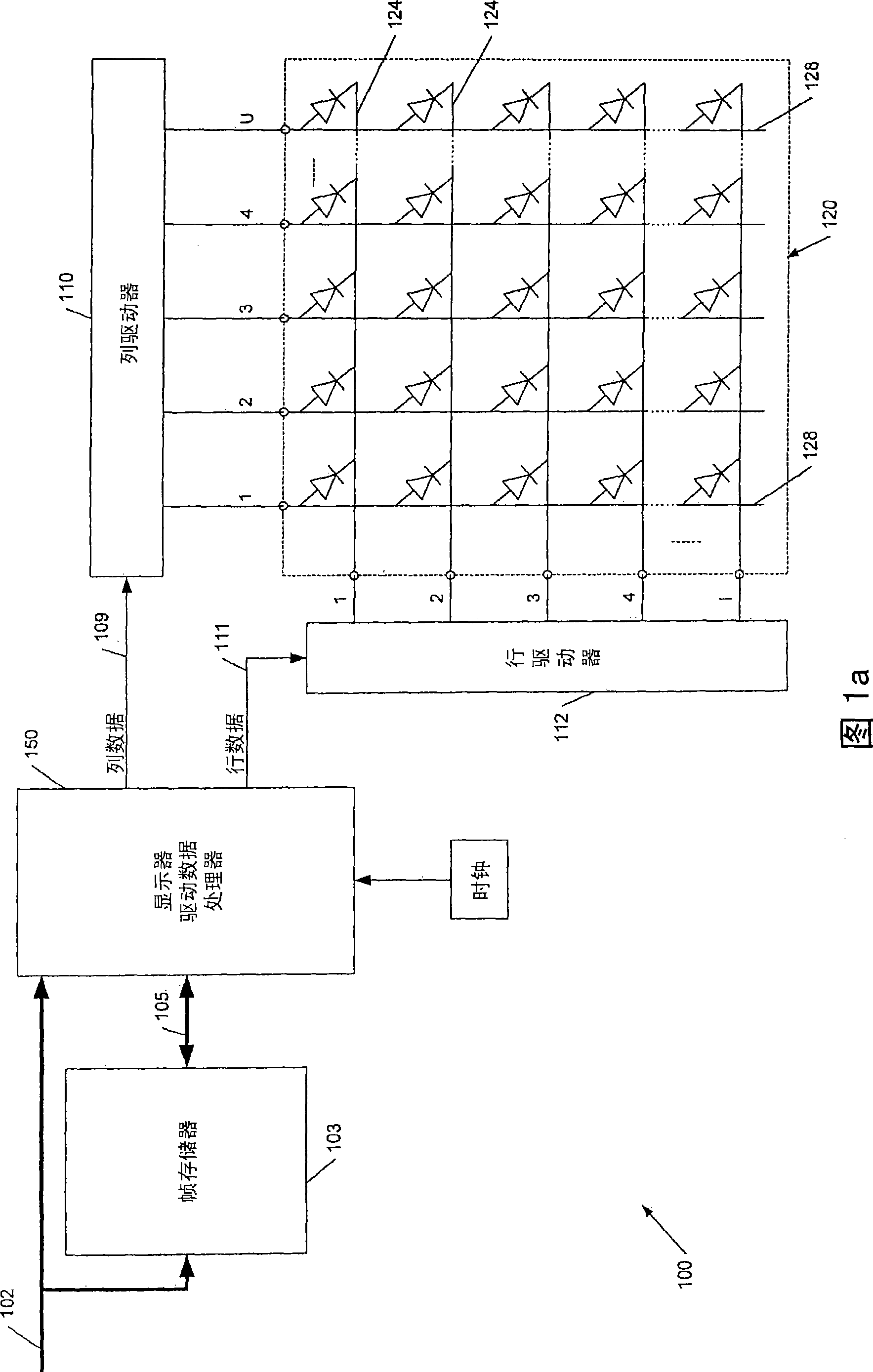

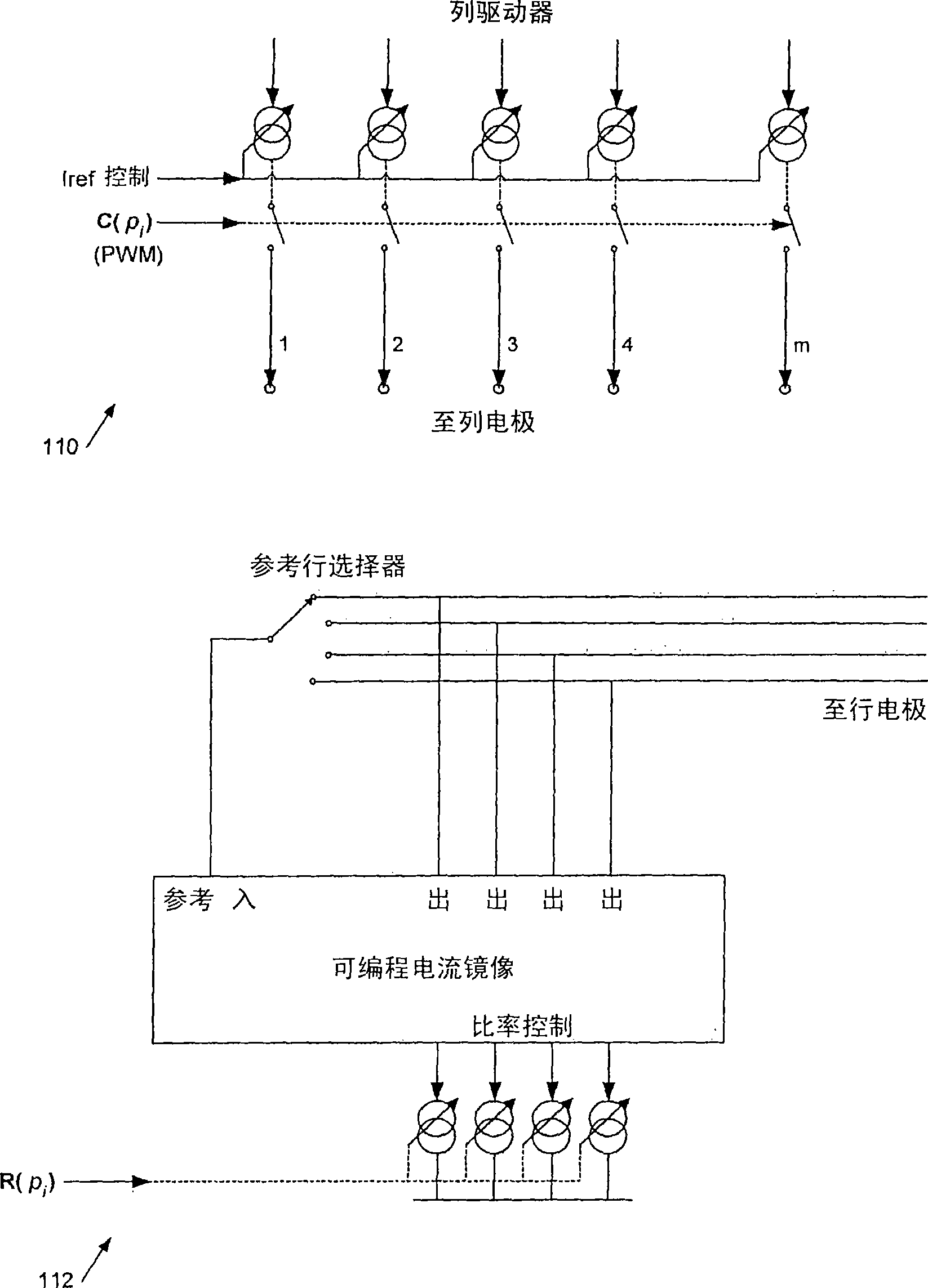

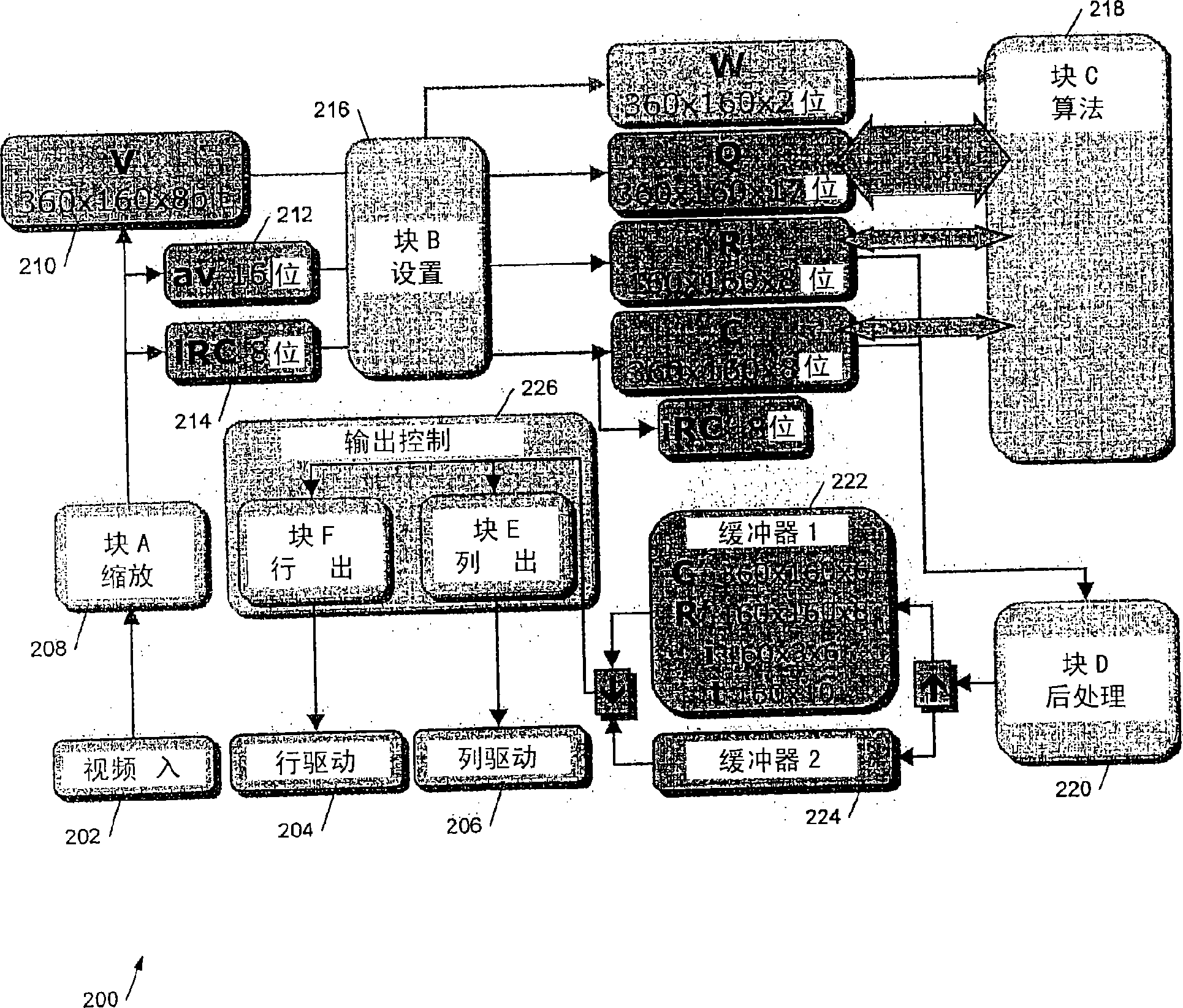

[0076] Now refer to figure 2 , which shows an OLED display driver system 200 including NMF hardware to perform TMA (Total Matrix Addressing). As shown, the system has a video supply input and provides row and column drive data outputs 204, 206 for driving a TMA driven display (not shown). will be described later for implementing figure 2 system, specifically a preferred embodiment of an NMF hardware accelerator for performing the preferred NMF computations described in the Introduction. However, it is understandable figure 2 The operation of the system is shown mapped to a number of functional blocks, and in a hardware embodiment (as shown later), the assignment of the hardware blocks to these functions differs from that of the illustrated blocks. For example, hardware accelerators described later may be controlled by software running on a digital signal processor (DSP) to implement some of all (non-NMF) functional blocks shown. In some preferred embodiments, however, s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More