Link reconfiguration method for PCIE interface and device thereof

An interface and link technology, which is applied in the field of link reorganization of PCIE interface, can solve the problems of unusable PCIE interface and low utilization rate of PCIE interface link, so as to reduce the probability of crash, improve utilization rate and ensure stability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0021] An embodiment of the present invention provides a method for link reorganization of a fast peripheral component interconnection PCIE interface, which will be described in detail below in conjunction with the accompanying drawings.

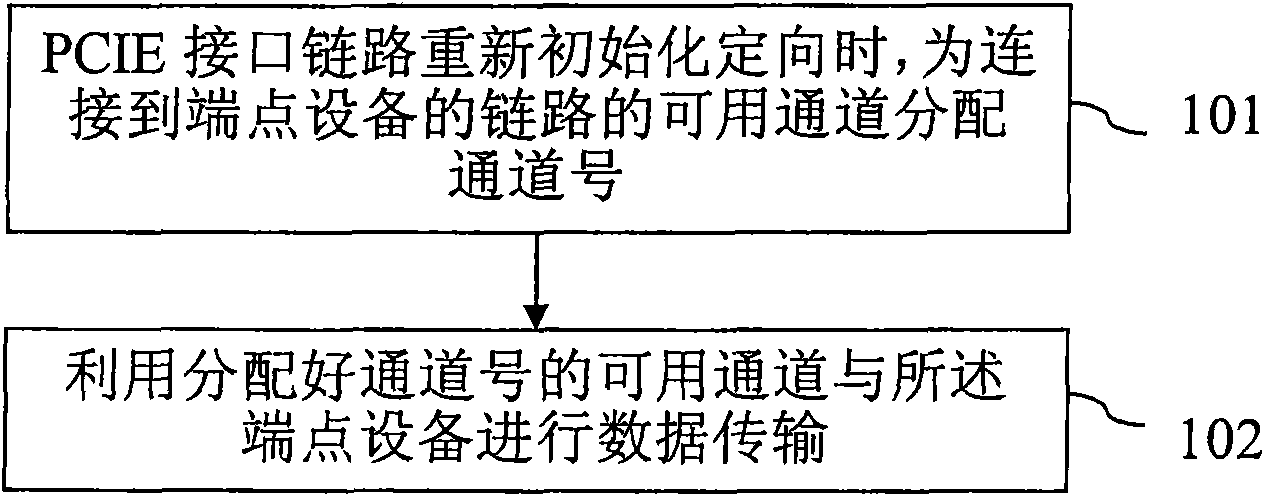

[0022] figure 1 For the method flowchart of this embodiment, the link reorganization method of the PCIE interface of this embodiment is applied to any device using the PCIE interface, wherein the PCIE interface device applying the method of the embodiment of the present invention is called the root complex as the master device , the slave device connected to the master device is called an endpoint device, such as figure 1 As shown, the method of the present embodiment mainly includes:

[0023] 101: When the PCIE interface link re-initializes the orientation, if the root complex finds that there is an endpoint device physically connected to it through the PCIE interface, and the electrical function of the link with the endpoint device is int...

Embodiment 2

[0030] An embodiment of the present invention also provides a method for link reorganization of a PCIE interface, which will be described in detail below in conjunction with the accompanying drawings.

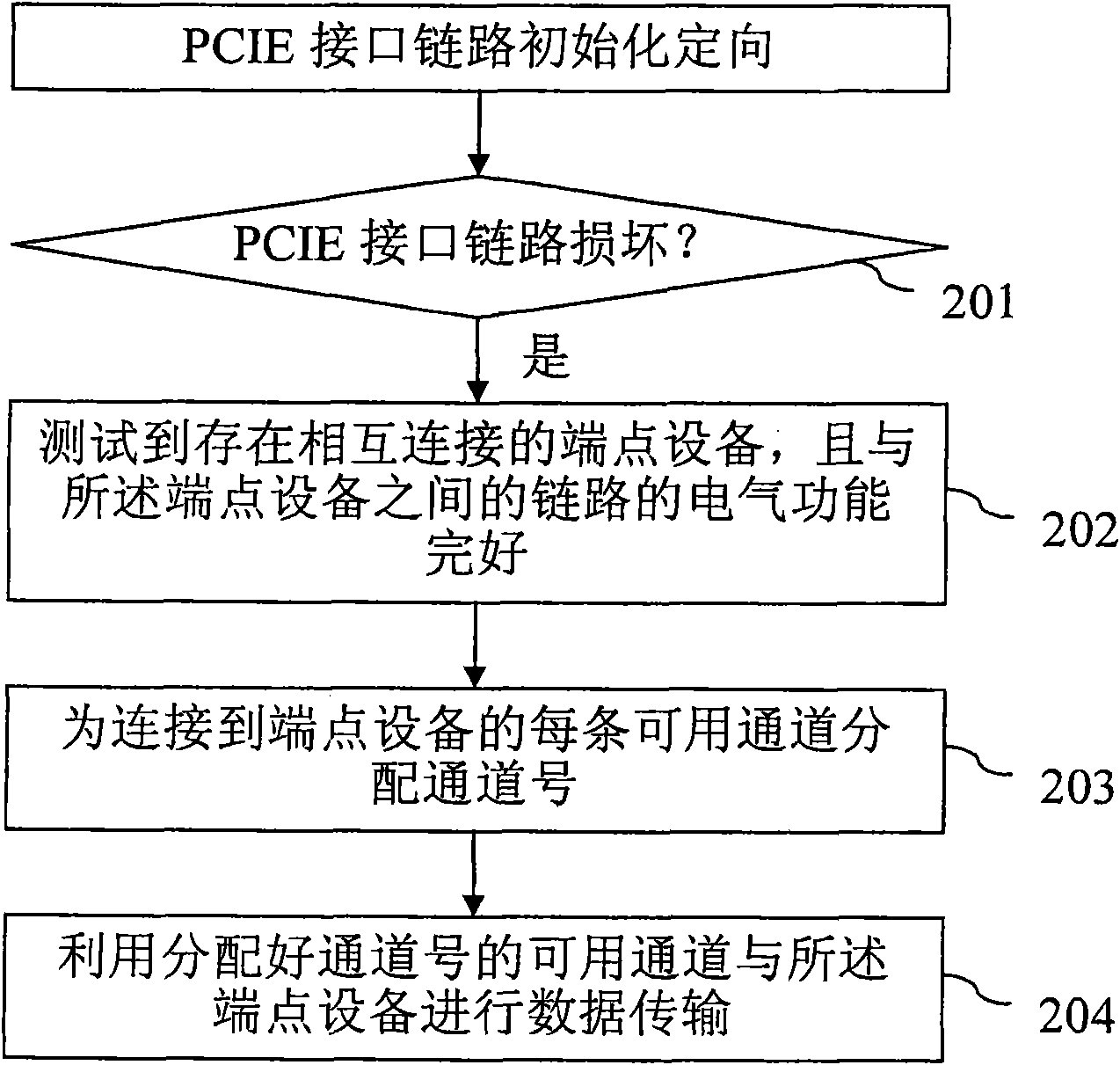

[0031] figure 2 It is the method flowchart of this embodiment, and the method of this embodiment is applied to any device using the PCIE interface. In this embodiment, the PCIE interface is an X16 link as an example for illustration, that is to say, the X16 link has 16 link channels, such as figure 2 As shown, the method of the present embodiment includes:

[0032] 201: If a link channel is damaged in the PCIE interface link, re-initialize the orientation of the PCIE interface link;

[0033] Among them, the link initialization orientation is to configure and initialize the physical layer of the device, the port and the physical layer control of related links, so that the link can transmit normal data packet traffic.

[0034] Generally, when the PCIE interface is working, t...

Embodiment 3

[0059] An embodiment of the present invention also provides a link reorganization device for a PCIE interface, which will be described in detail below in conjunction with the accompanying drawings.

[0060] Figure 5 It is a block diagram of the apparatus of this embodiment, and the apparatus of this embodiment can be applied to any equipment using the PCIE interface, such as Figure 4 As shown, the link reorganization device of the PCIE interface of the present embodiment mainly includes:

[0061] Configuration unit 51, for when the PCIE interface link re-initializes the orientation, if there is an endpoint device that is physically connected through the PCIE interface, and when the electrical function of the link between the endpoint device is intact, it is connected to The available channel allocation channel number of the link of the endpoint device;

[0062] The processing unit 52 is configured to perform data transmission with the endpoint device by using the available...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More