Manufacturing method for protecting interval wall of bipolar transistor circuit

A technology of bipolar transistor and manufacturing method, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of junction leakage current, low current gain β, prolonged dry etching time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below in conjunction with embodiment and accompanying drawing.

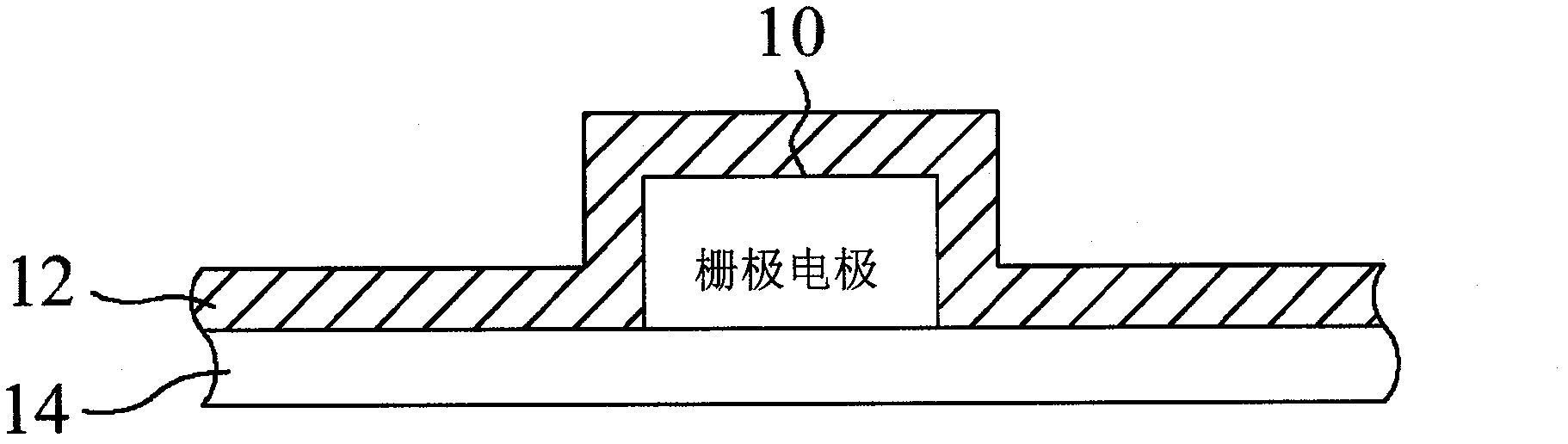

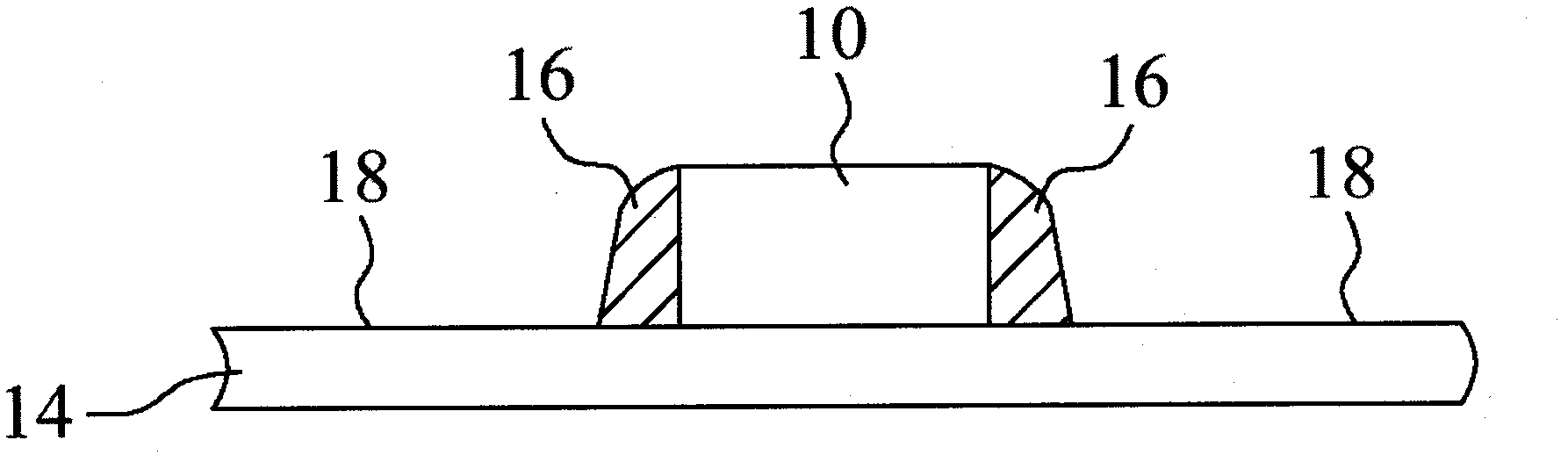

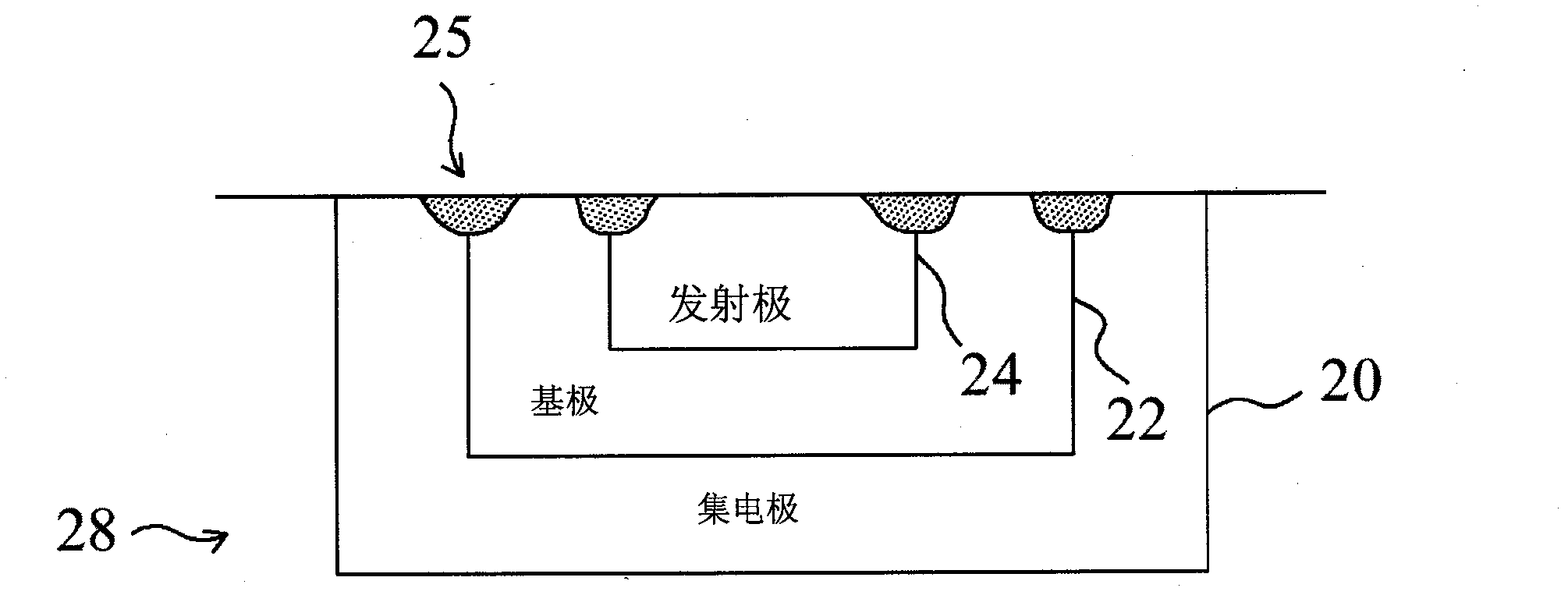

[0027] see now Figure 4 ~ Figure 7 , Figure 4 It is a structural schematic diagram of an embodiment of the present invention, Figure 5 is another structural schematic diagram of an embodiment of the present invention, Image 6 It is another structural schematic diagram of an embodiment of the present invention, Figure 7 It is another structural schematic diagram of the embodiment of the present invention. As shown in the figure, the silicon substrate 30 has a collector 38 and a base 36 of a BJT, and a gate 34 of a MOS transistor. After the spacer material layer 32 is deposited on the surface of the silicon substrate 30, an electrical The slurry or charged particles perform isotropic dry etching on the spacer material layer 32 . Such as Figure 5 As shown, when the spacer material layer 32 is dry-etched until the thin layer 40 is left, the dry etchin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More