Port bandwidth guaranteed packet switching chip and implementation method thereof

A bandwidth guarantee, packet switching technology, applied in the field of data communication, can solve the problems of complex implementation, increased chip cost, increased chip area, etc., to achieve the effect of simple hardware implementation, reduced transmission buffer, and reduced area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

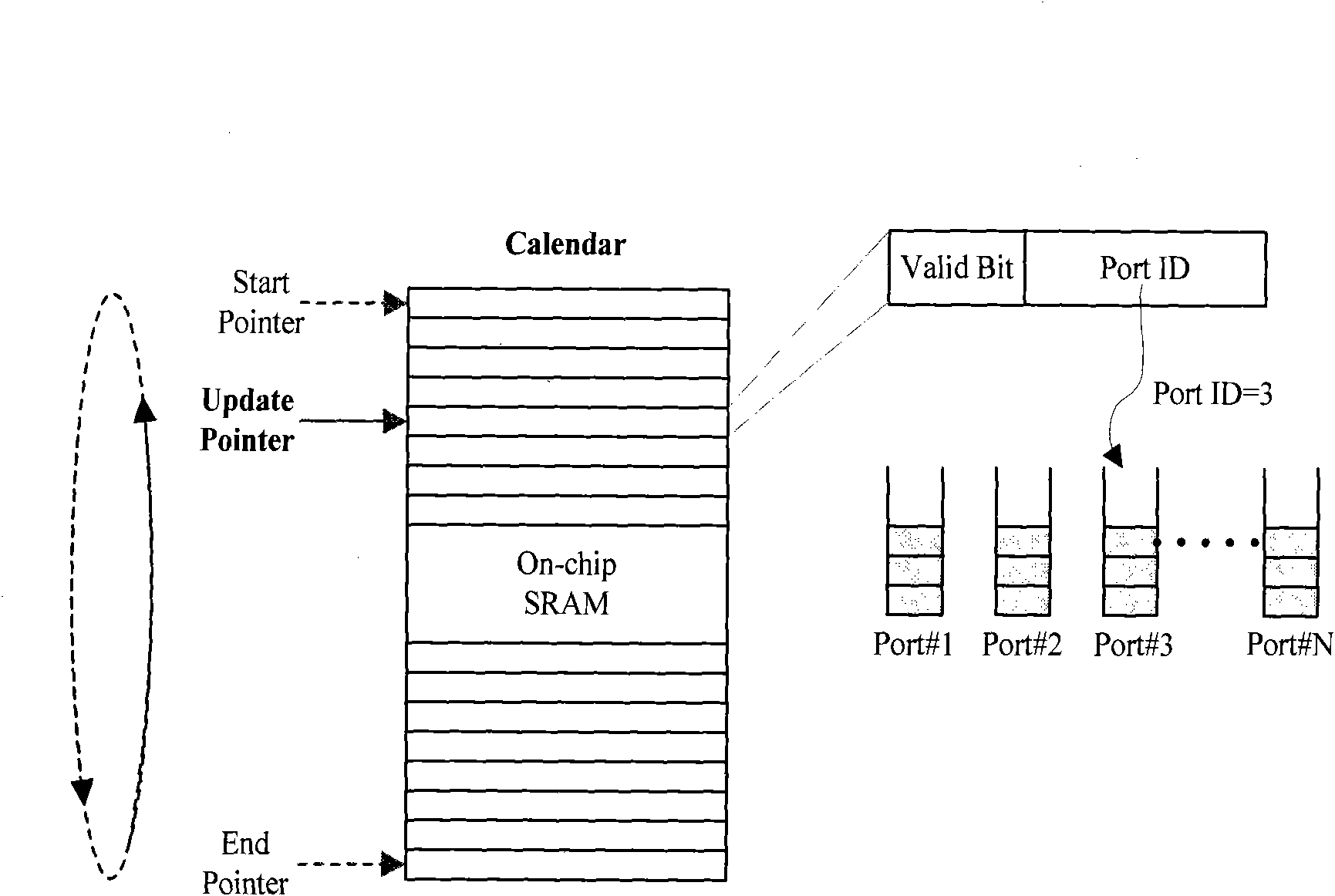

Method used

Image

Examples

Embodiment 1

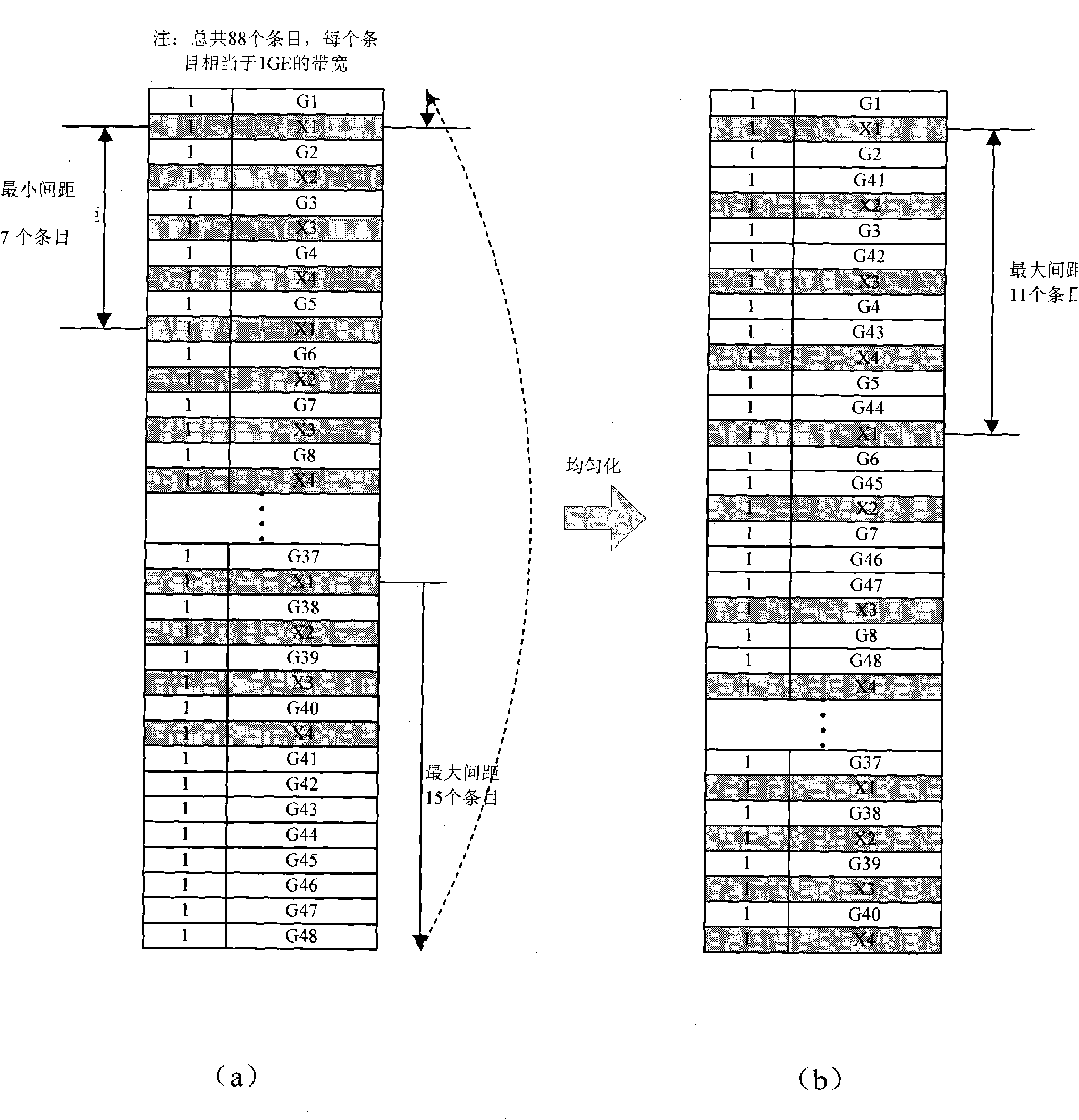

[0037] When the port combination of the packet switching chip is configured as 48 Gigabit ports (numbered {G1, G2, G3,..., G48}) plus 4 10 Gigabit ports (numbered {X1, X2, X3, X4}), its configuration in Calendar can be as figure 2 (a) The way shown. From figure 2 As you can see in (a), there are a total of 88 entries in Calendar. Each entry is equivalent to the bandwidth of a gigabit port. Each gigabit port occupies an entry in Calendar, and a 10-Gigabit port occupies 10 in Calendar. Items. The entries occupied by the four 10 Gigabit ports {X1, X2, X3, X4} are interspersed between the entries of the gigabit ports starting from the entry G1 of the first gigabit port until the entry G40 of the 40th gigabit port. ; And from the entry G41 of the 41st Gigabit port, it is arranged continuously to the entry G48 of the 48th Gigabit port, which makes the distribution spacing of the 10 Gigabit ports in the Calendar quite different, and increases the transmission of the 10 Gigabit port...

Embodiment 2

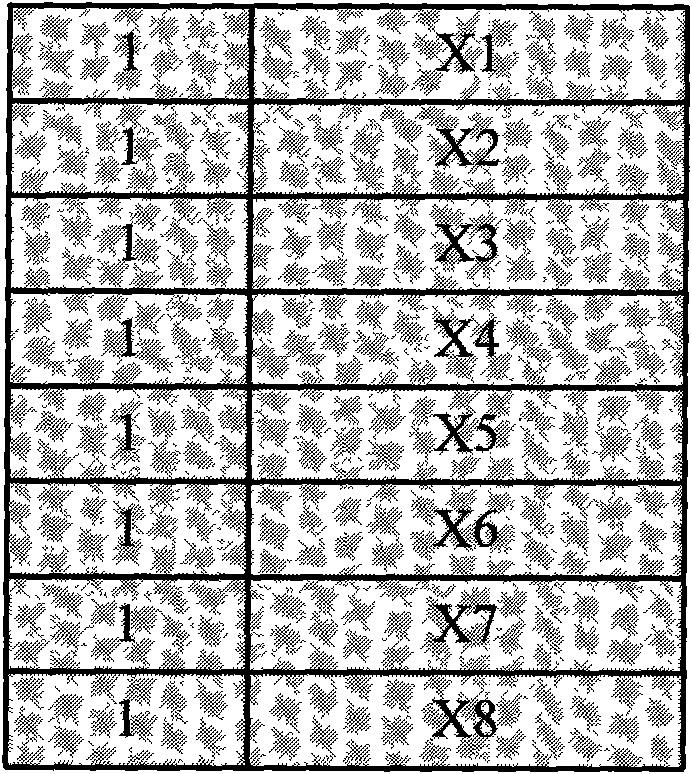

[0040] When the chip’s port combination is configured as 8 10 Gigabit ports (numbered {X1, X2, X3, X4, X5, X6, X7, X8}), its configuration in Calendar is as follows image 3 Shown. From image 3 It can be seen that each entry in the Calendar is equivalent to the bandwidth of a 10 Gigabit port, and each 10 Gigabit port occupies an entry in the Calendar, and such a configuration makes the distribution of the 10 Gigabit ports even.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More