Patents

Literature

84results about How to "Phase accurate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System and method for determination of position

InactiveUS20090149202A1Low costReduce requirementDigital computer detailsPosition fixationTime of arrivalGeographic area

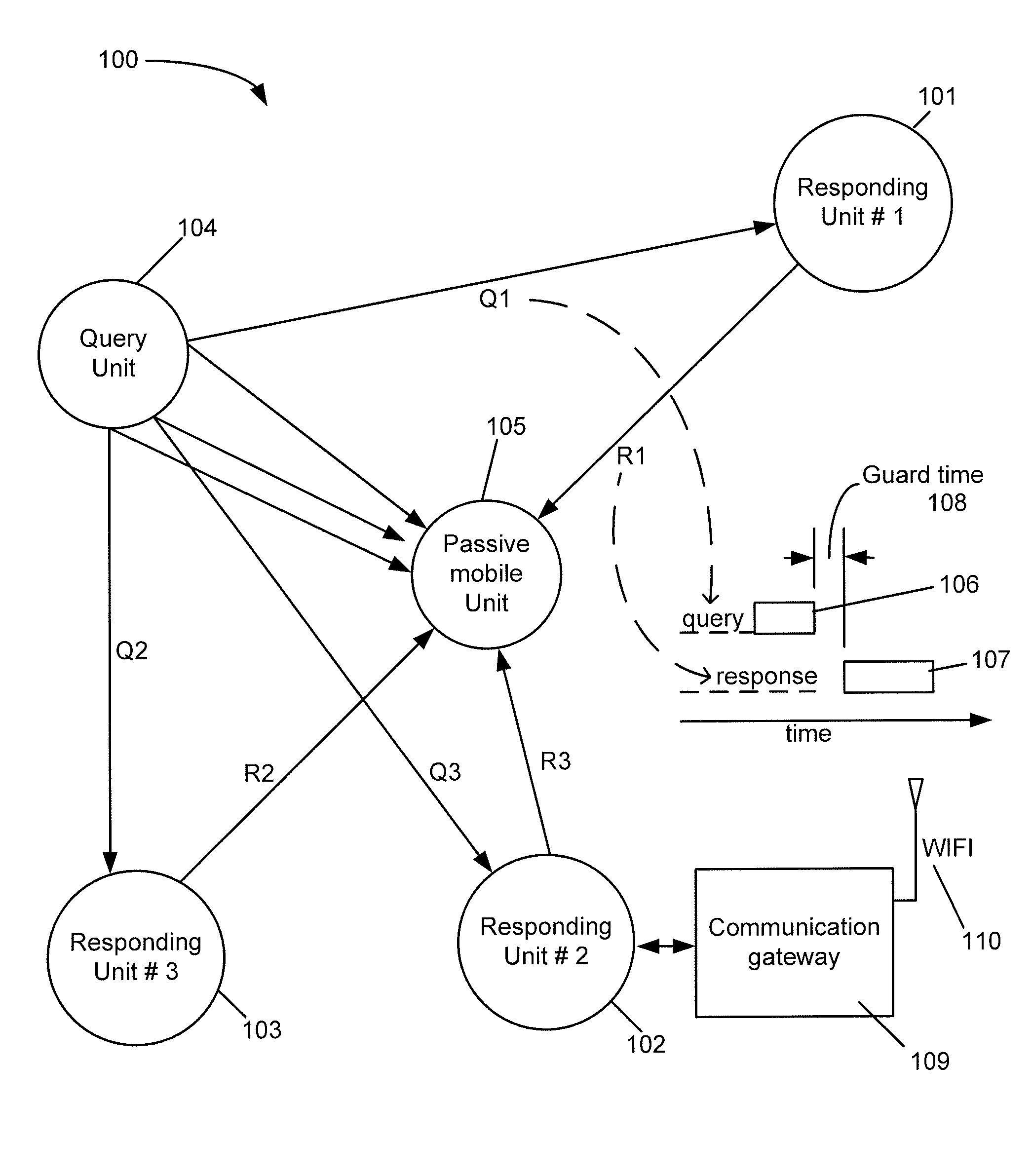

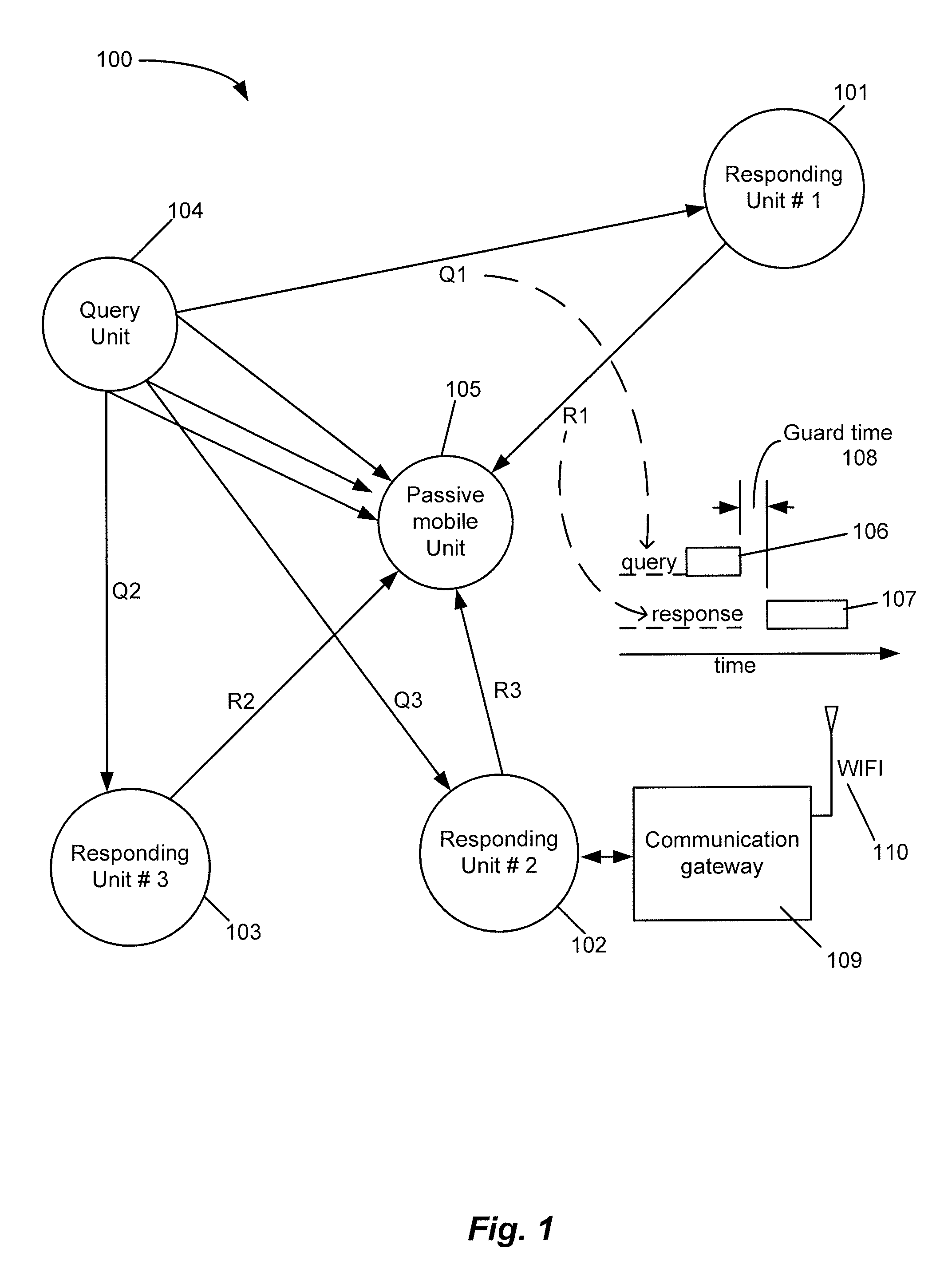

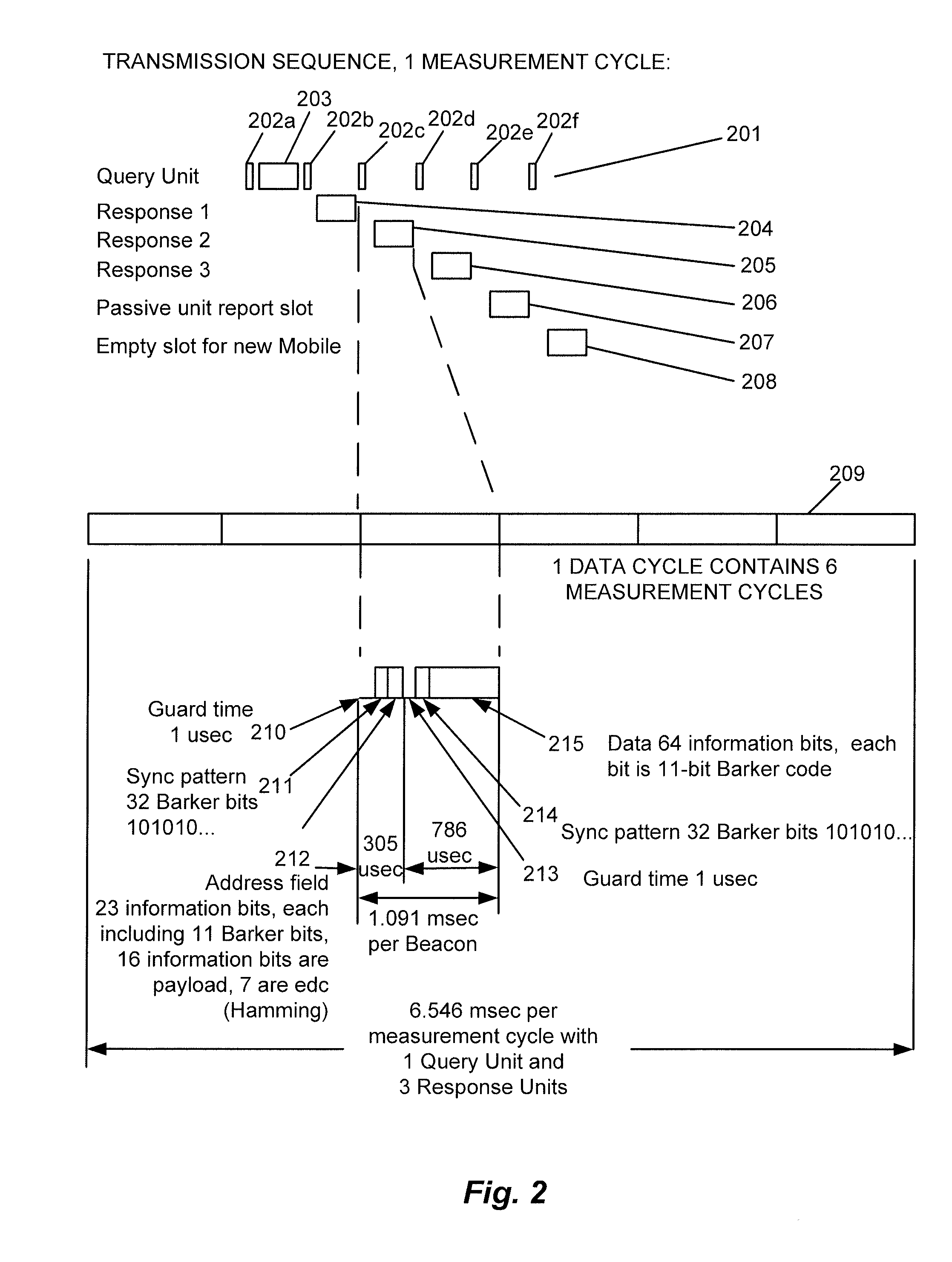

A system and method of determining and reporting on the position of a wireless device relative to a group of other wireless devices dispersed within a specified geographic area. The system includes at least one Query Unit, three or more Responding Units disposed at determinable locations within the specified geographic area, and one or more Mobile Units, which may correspond to additional Responding Units or units that function only as receivers. The Query Unit sequentially queries the Responding Units, and, responsive to the respective query messages, the Responding Units transmit corresponding response messages. One or more of the Mobile Units receive the query and response messages, and generate, for each query-response message pair, a set of time-difference-of-arrival (TDOA) measurements, which are used by the Mobile Units to determine their positions relative to the Responding Units. The Mobile Units record the times-of-arrival (TOAs) of the query message and the response messages at their respective receivers, and calculate the TDOAs based on the recorded TOAs. The TDOAs are then analyzed to determine the time differences due to the differences in lengths of the respective message propagation paths. The position of each Mobile Unit can then be computed using computation techniques typically employed in Long Range Navigation (LORAN) receivers, or any other suitable computation technique.

Owner:STEELE CHRISTIAN

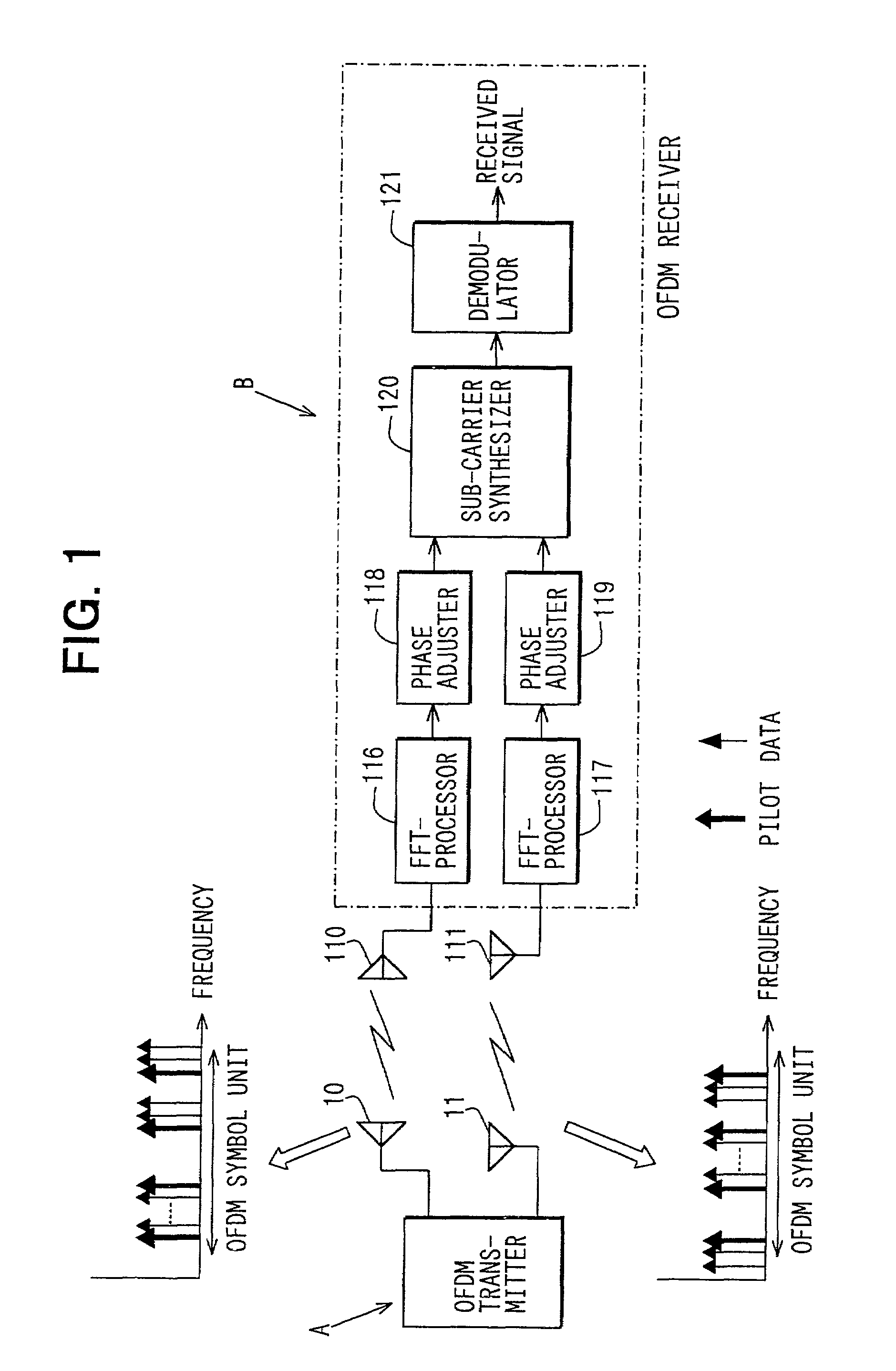

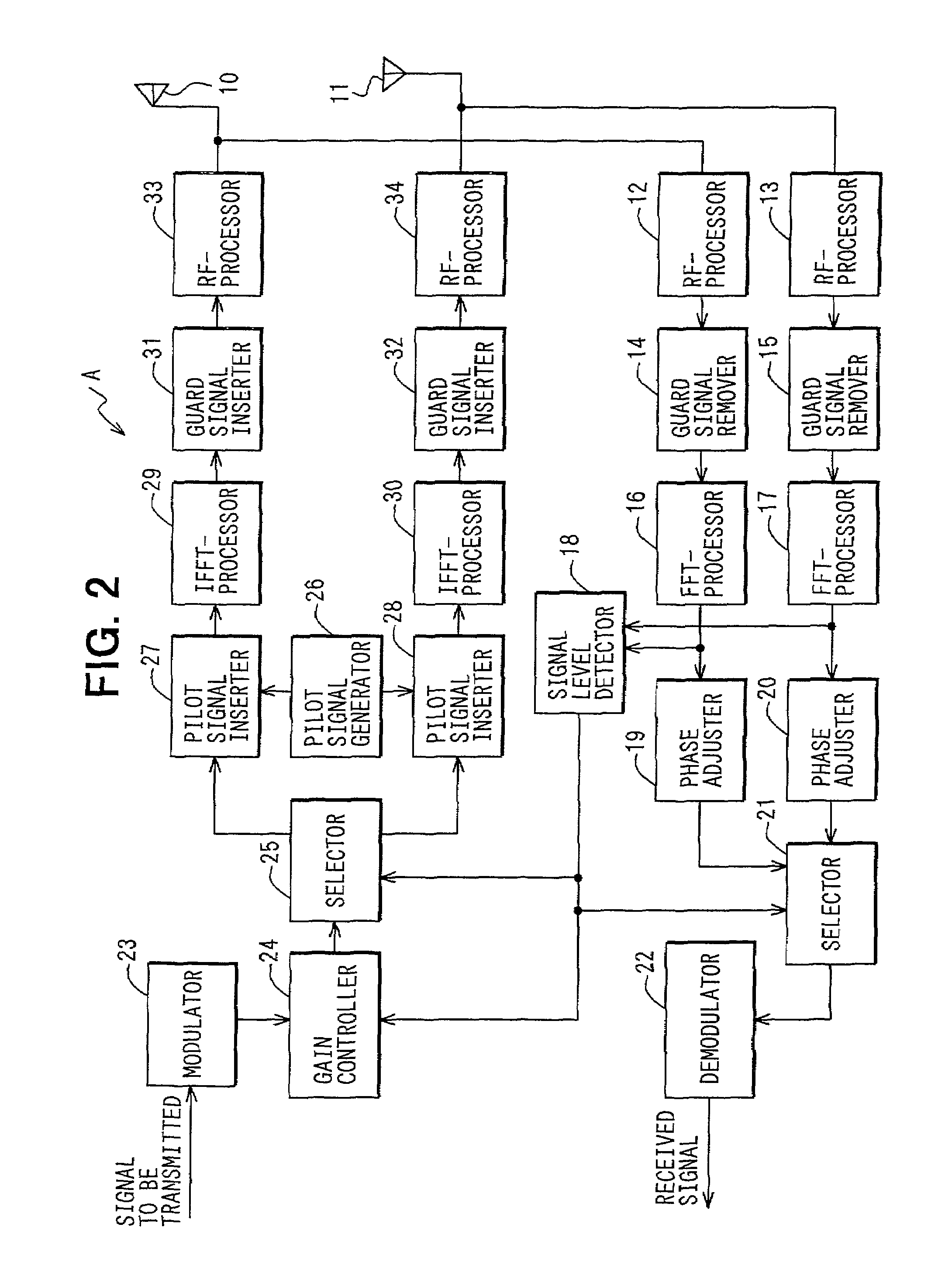

OFDM communication system and transmitter-receiver for use in the system

ActiveUS7099265B2Easy to adjustFacilitate communicationModulated-carrier systemsPolarisation/directional diversityData signalTransmission channel

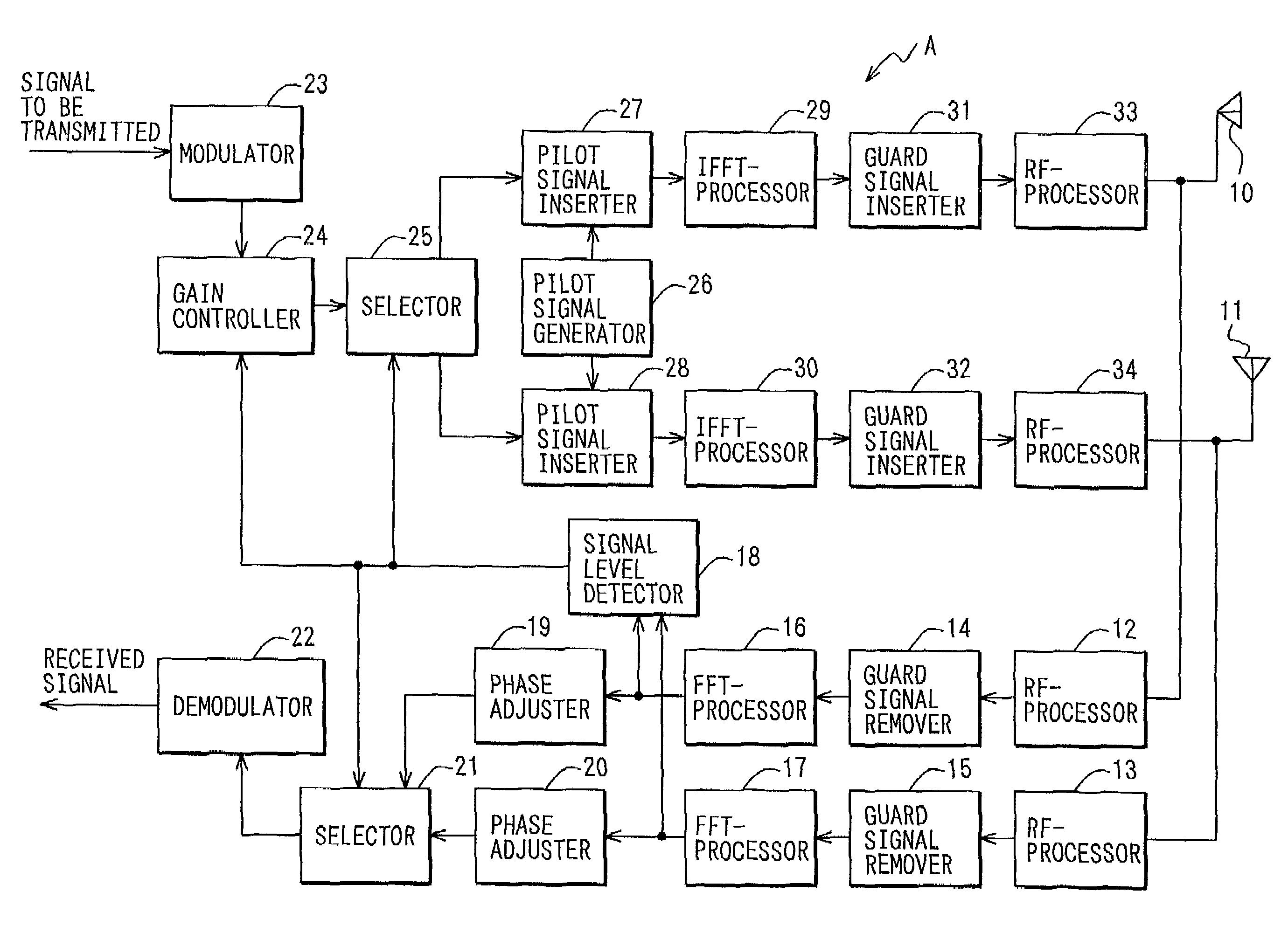

A diversity OFDM communication is performed between a base terminal and a mobile terminal, both having a horizontal polarization antenna and a vertical polarization antenna forming two transmission channels. In the base terminal, data signals to be transmitted are divided into two channels to transmit the data signals through either one of the channels having a higher transmission performance for each sub-carrier. Common pilot signals are transmitted through both channels. The data signals received by the mobile terminal are phase-adjusted using the common pilot signals. The phase-adjusted data signals in both channels are synthesized and then demodulated.

Owner:DENSO CORP

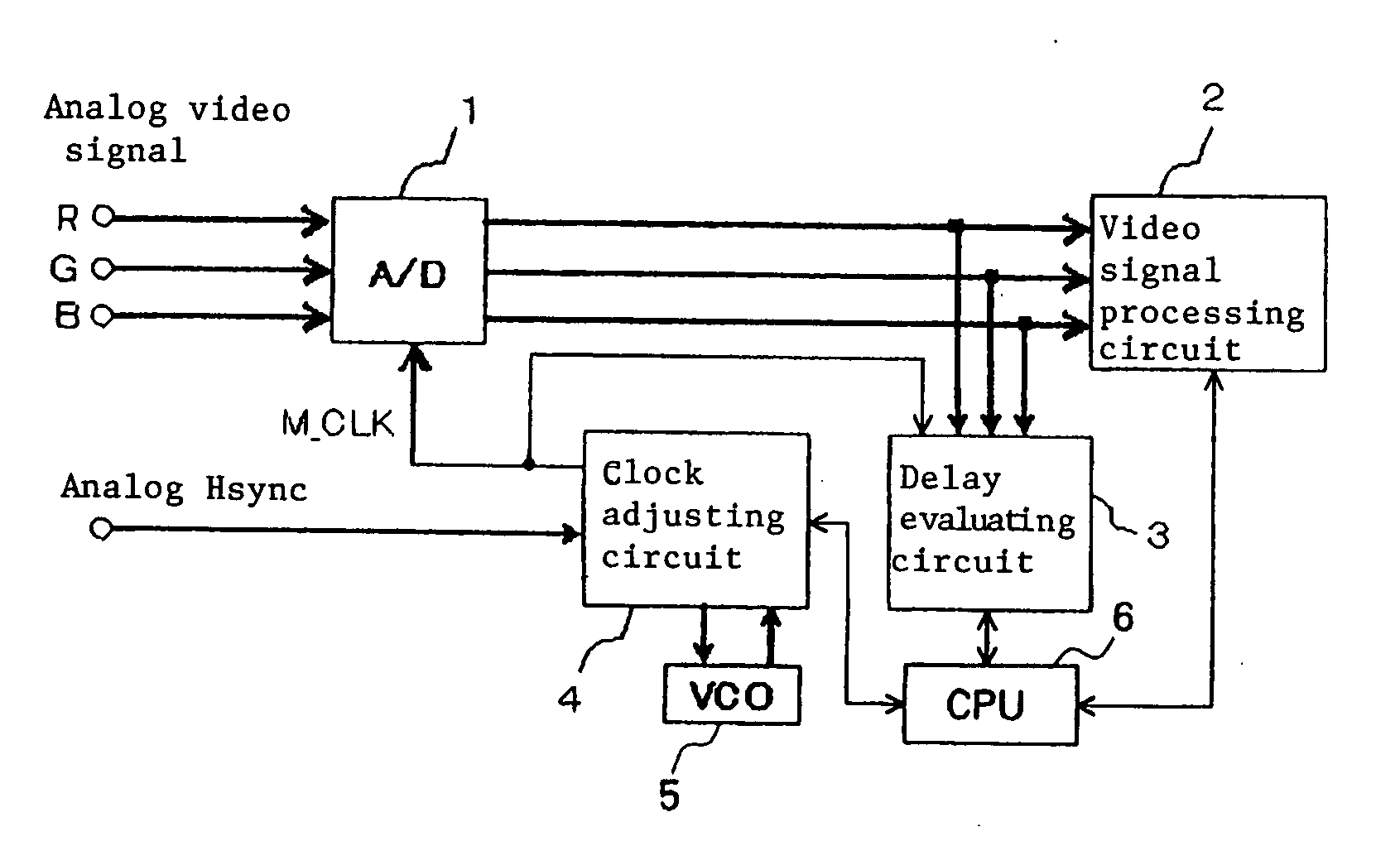

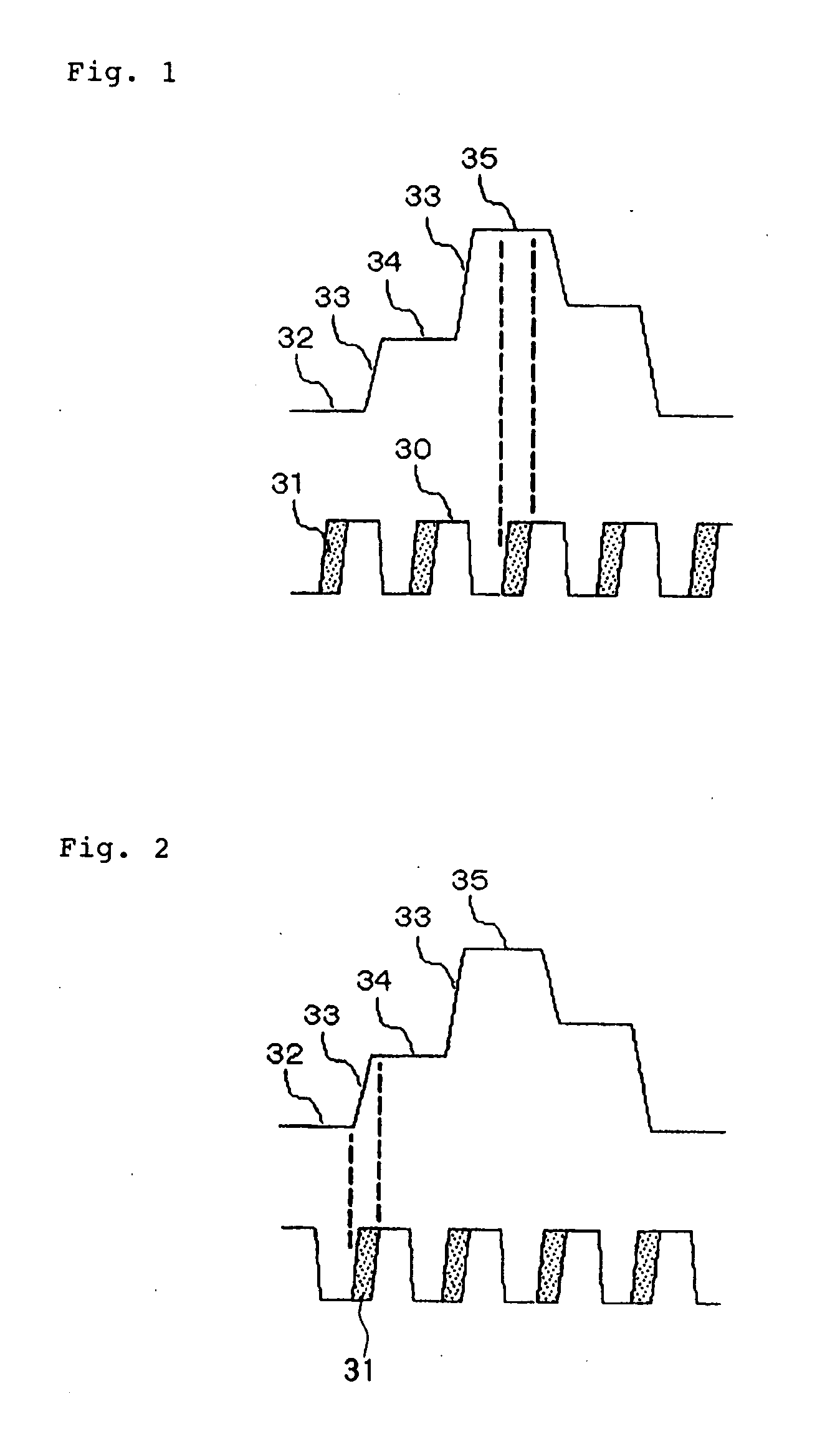

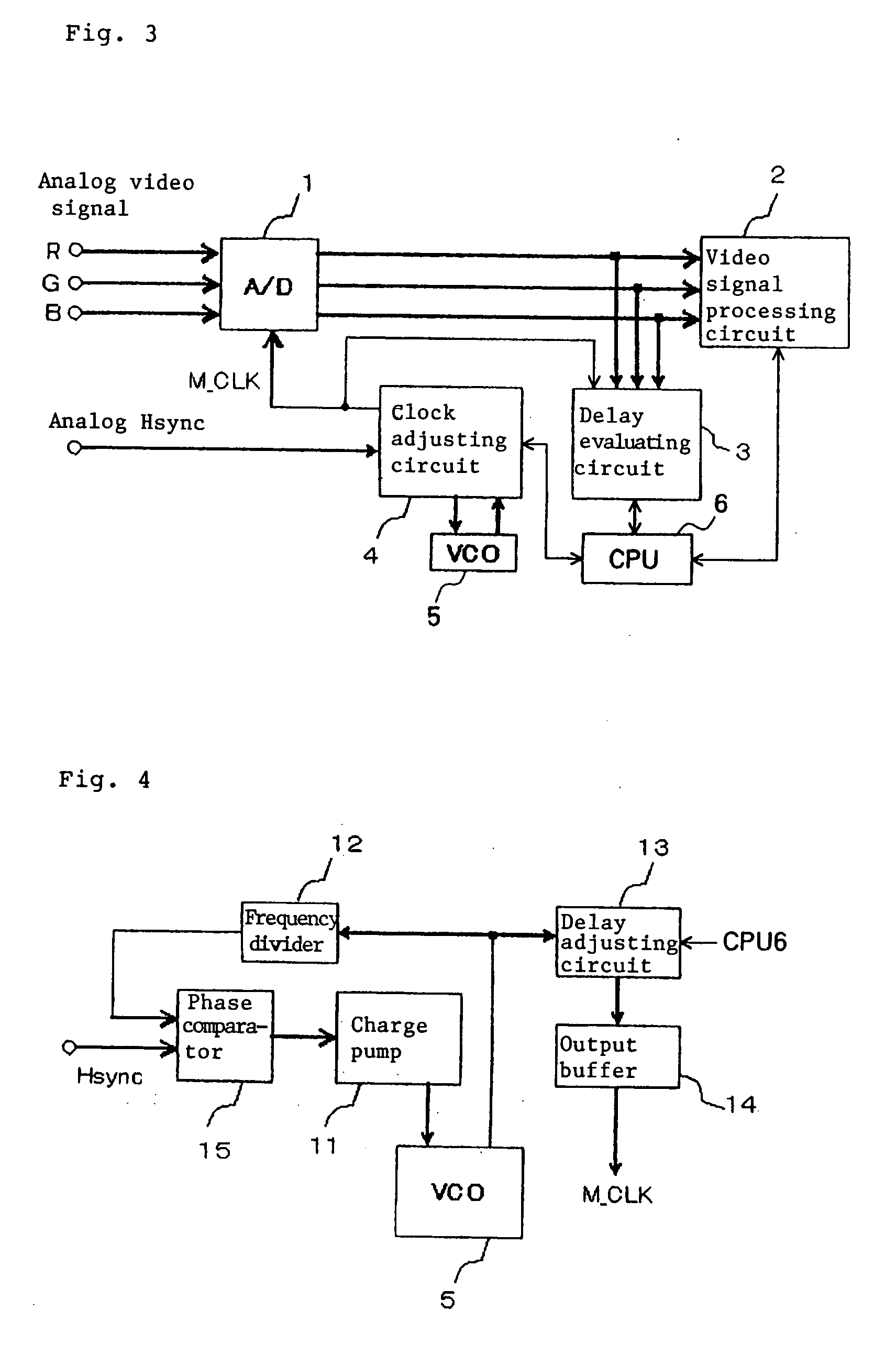

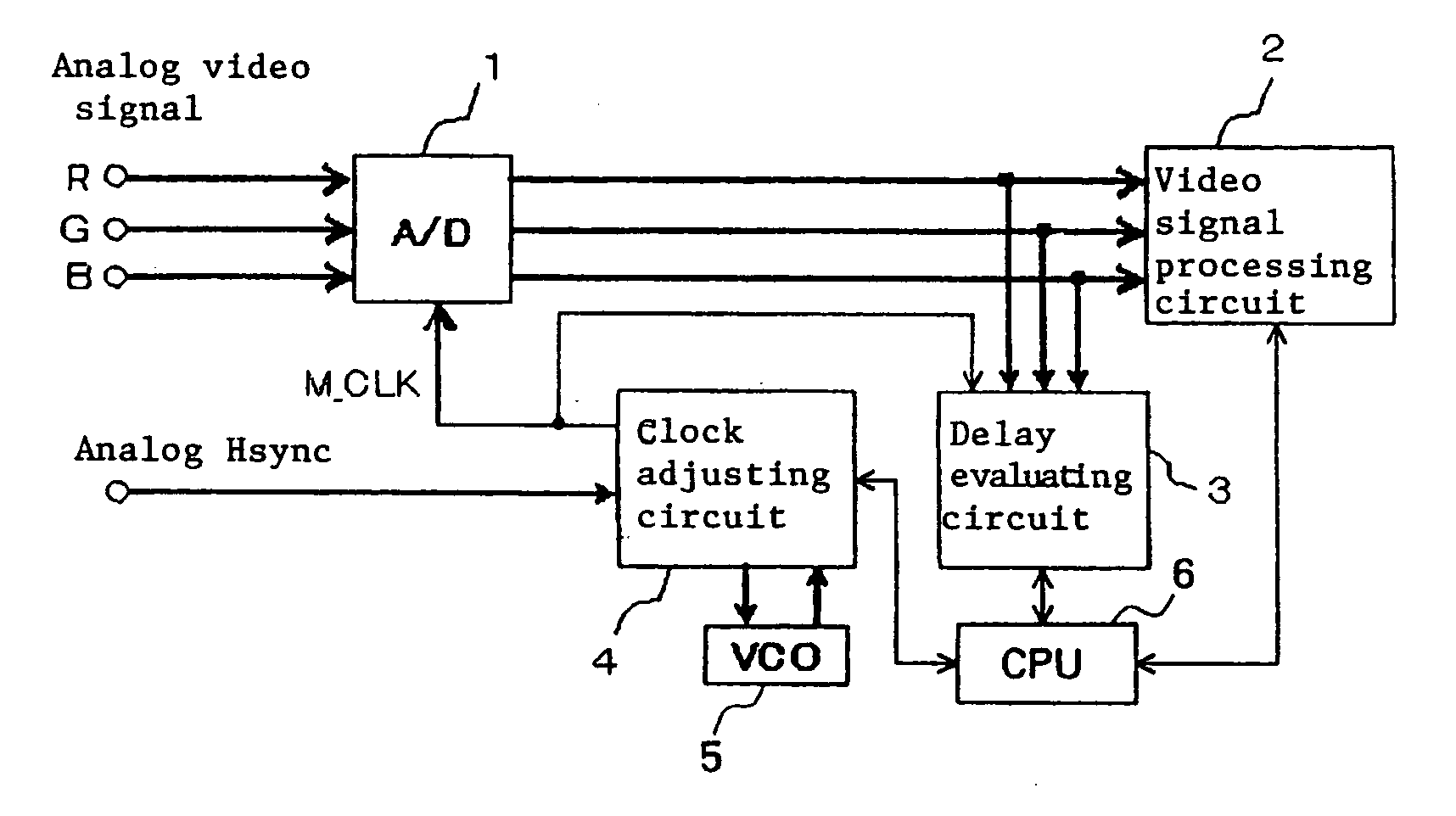

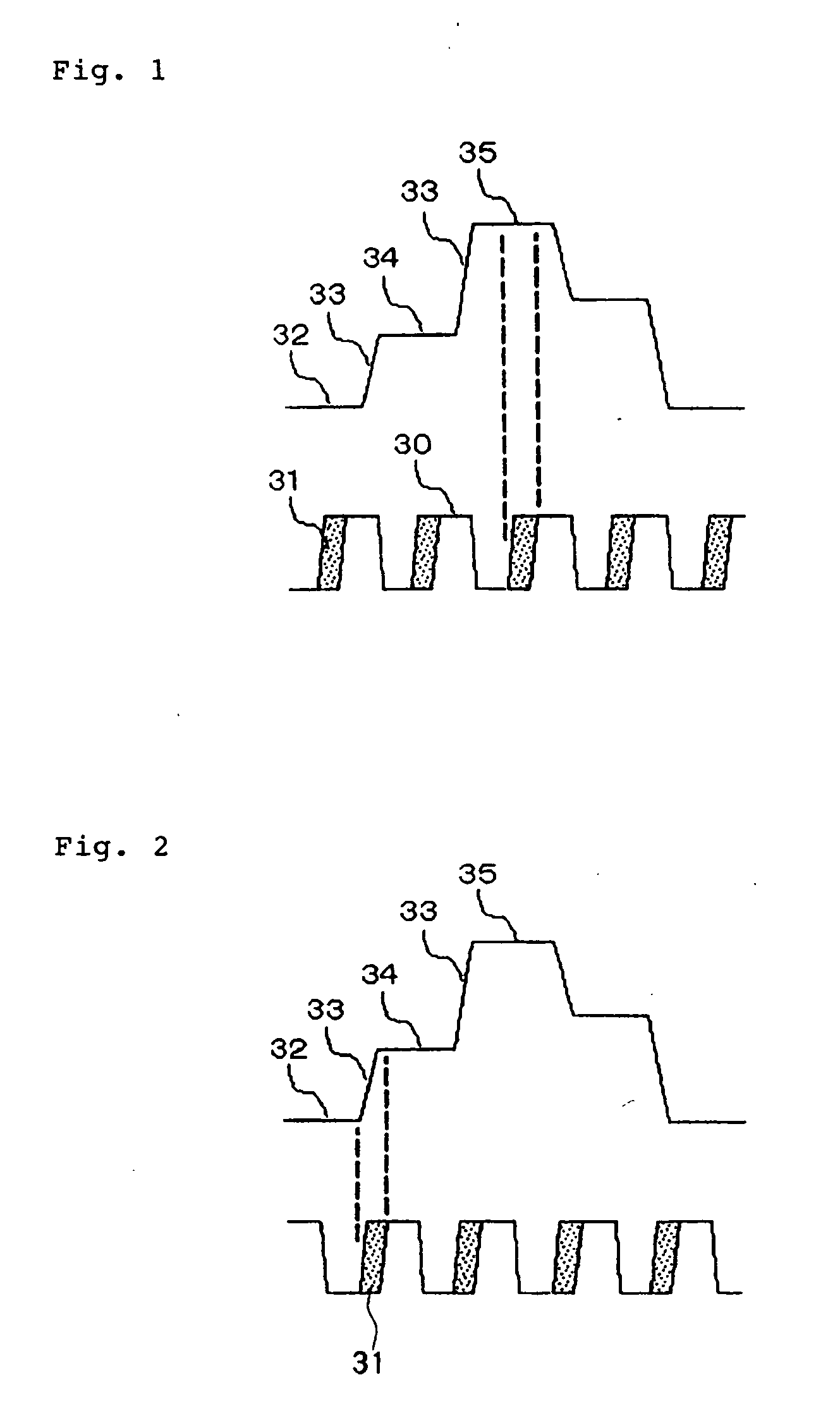

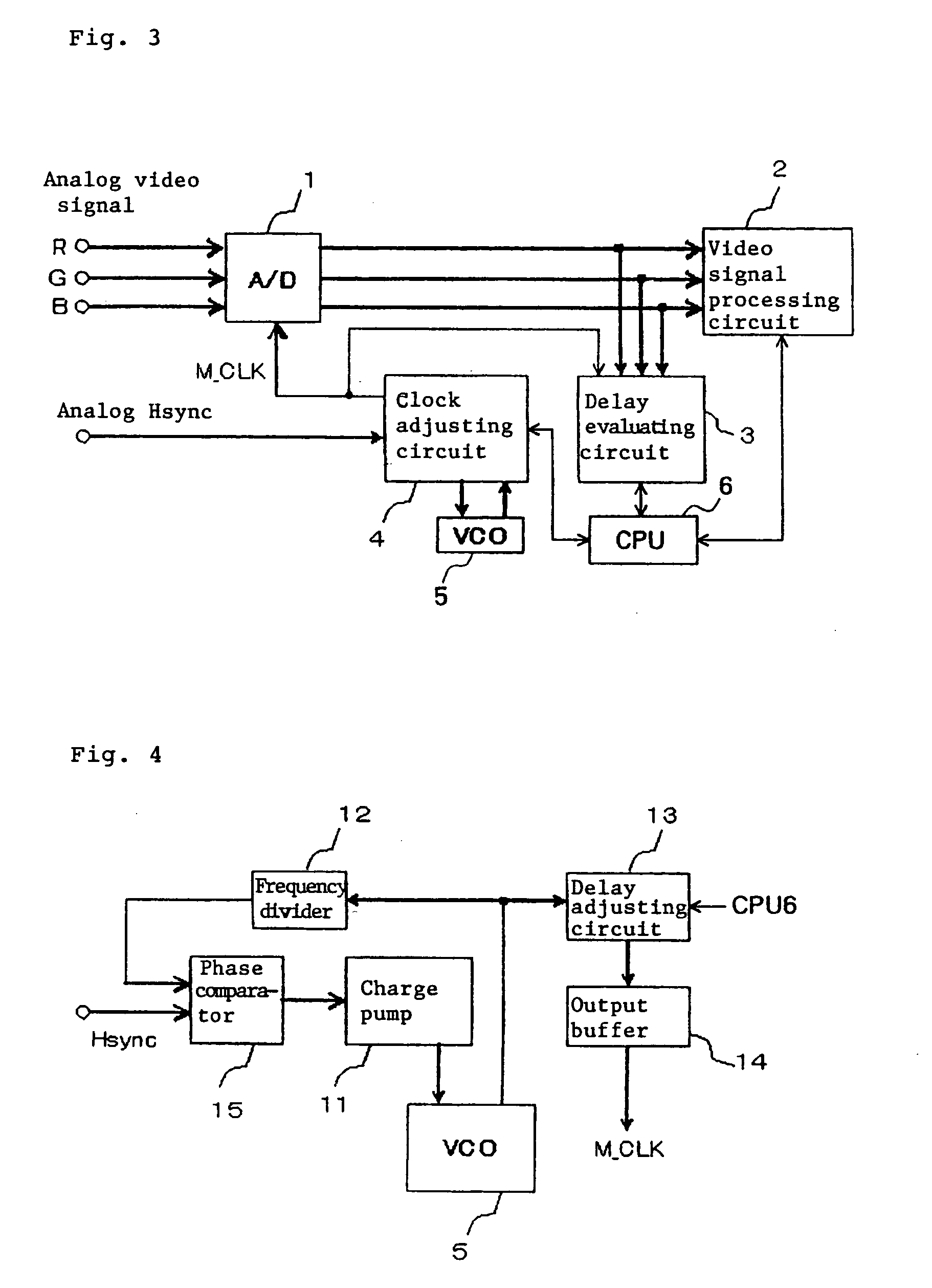

Image display apparatus and method of adjusting clock phase

InactiveUS20080002058A1Automatically adjusting phasePhase accuratePulse automatic controlCathode-ray tube indicatorsDigital videoClock phase

An image display apparatus has an A / D converter for sampling an analog video signal whose signal level changes at a frequency higher than the frequency of a synchronizing signal, based on a reproduced dot clock, and converting the sampled analog video signal into a digital video signal, a clock adjusting circuit for generating a clock in synchronism with the synchronizing signal, delaying the phase of the clock according to set delays, and outputting the delayed clock as the reproduced dot clock, a controller for dividing an area of an image displayed based on the converted digital video signal, into a plurality of image areas defined by display lines in a horizontal direction, and establishing different delays for the divided image areas, and a delay evaluating circuit for converting differential data between adjacent signal levels on the display lines for the respective image areas, into absolute values and accumulatively adding the absolute values, thereby producing accumulated sums. The controller judges the delay established for the divided area with the maximum accumulated sum, as an optimum delay.

Owner:NEC DISPLAY SOLUTIONS LTD

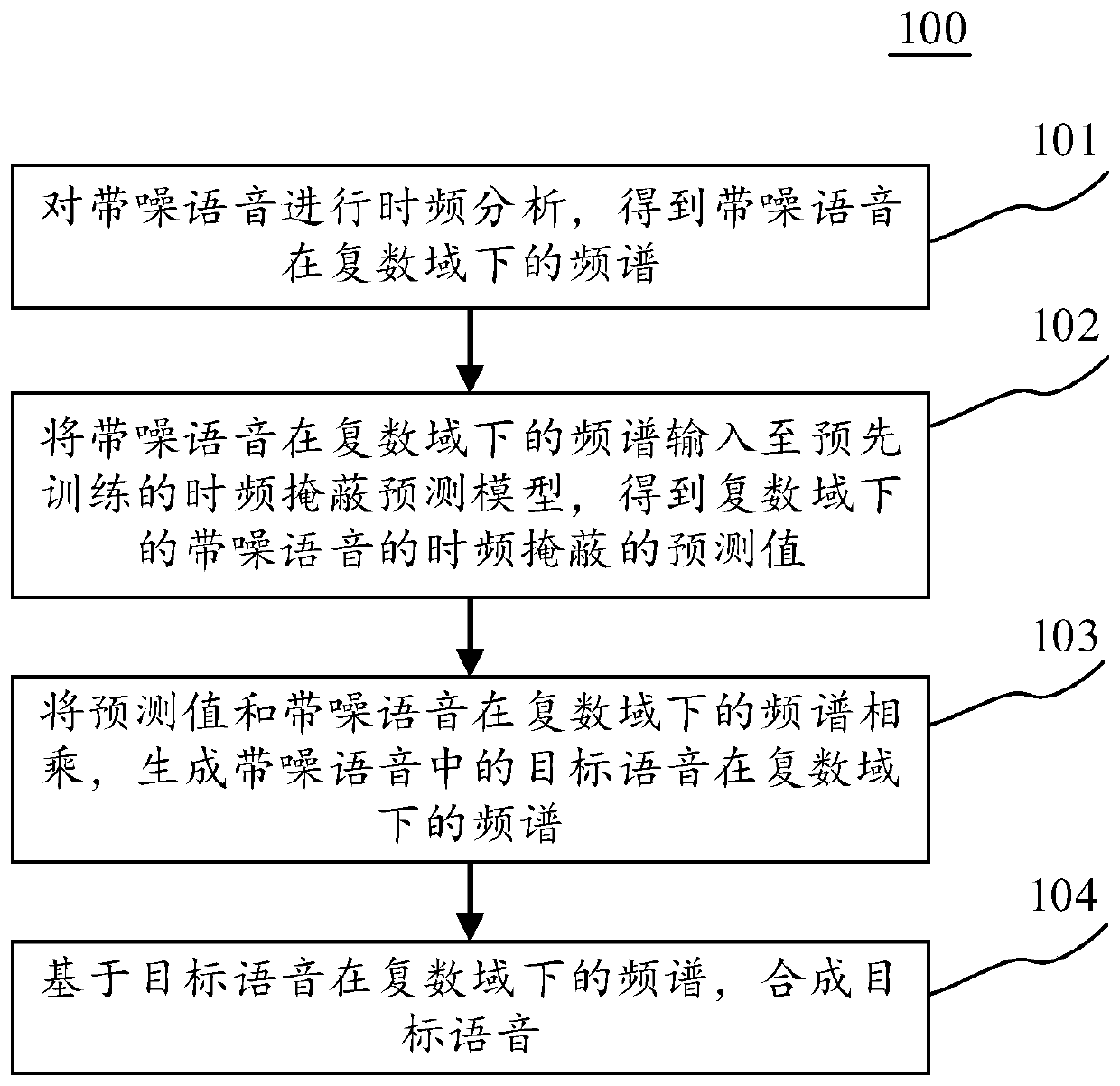

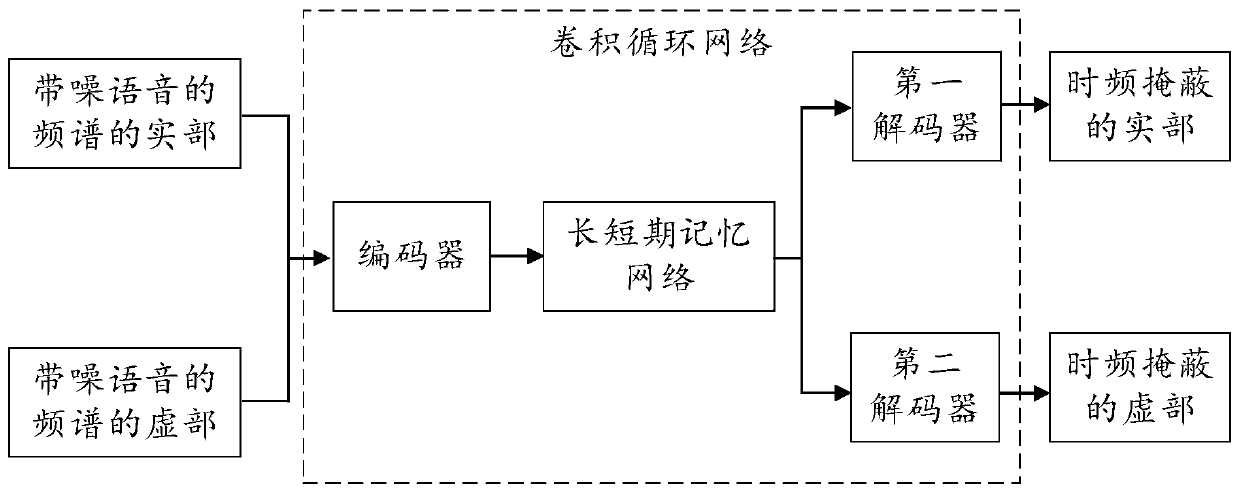

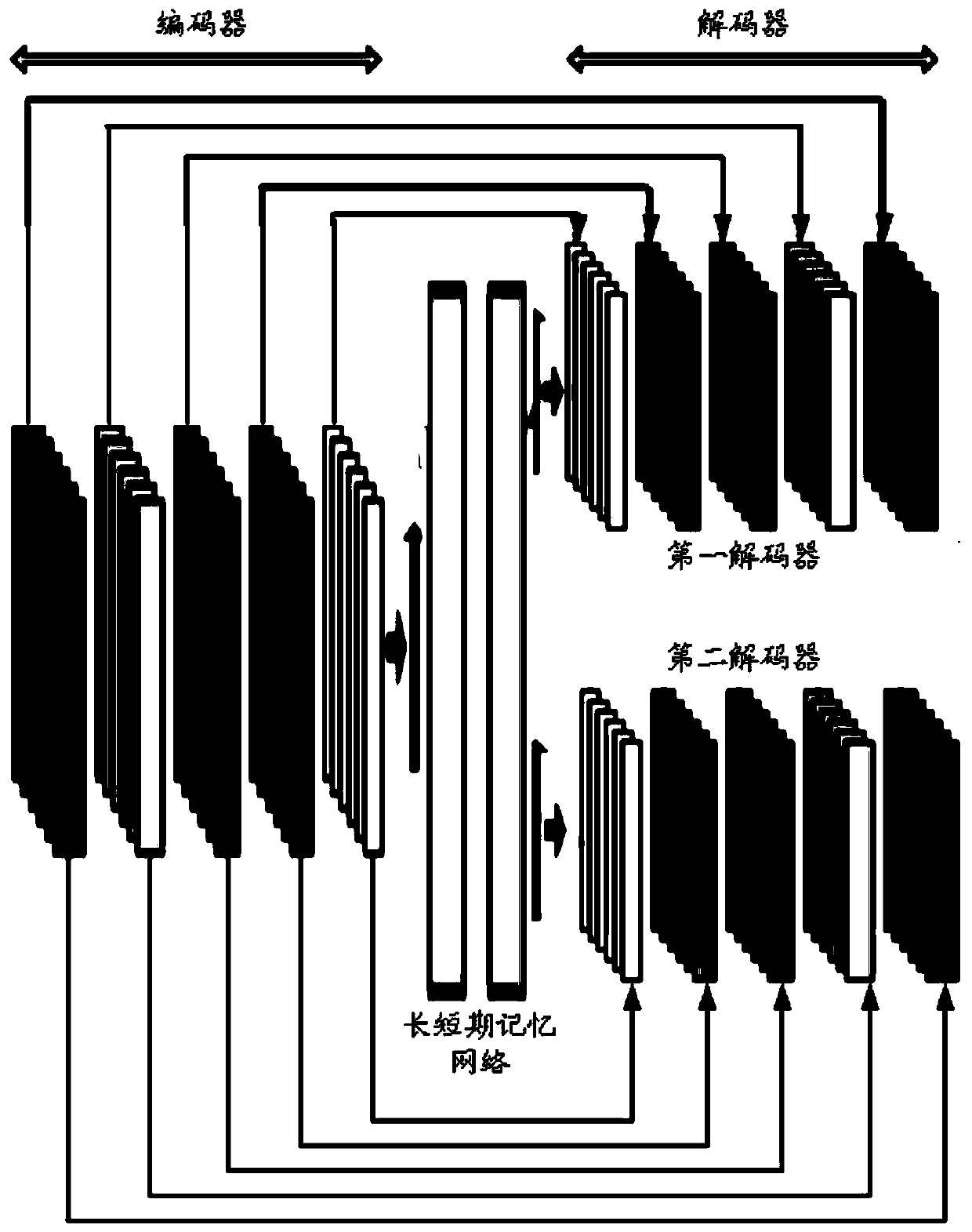

Voice processing method, voice processing device and device for processing voice

InactiveCN110808063APhase accurateReduce voice distortionSpeech analysisFrequency spectrumTime frequency masking

The embodiment of the invention discloses a voice processing method, a voice processing device and a device for processing voice. The embodiment of the method comprises the following steps of performing time-frequency analysis on noisy voice to obtain the frequency spectrum of the noisy voice in complex domains; inputting the frequency spectrum of the noisy voice in the complex fields into a pretrained time-frequency shielding prediction model; obtaining a prediction value of time-frequency masking of the noisy voice in the complex domains; multiplying the prediction value by the frequency spectrum of the noisy voice in the complex domains; generating the frequency spectrum of target voice in the noisy voice in the complex domains; and synthesizing the target voice on the basis of the frequency spectrum of the target voice in the complex domains. The embodiment has the advantages that the voice distortion degree is reduced, and the voice noise reduction effect is improved.

Owner:BEIJING SOGOU TECHNOLOGY DEVELOPMENT CO LTD

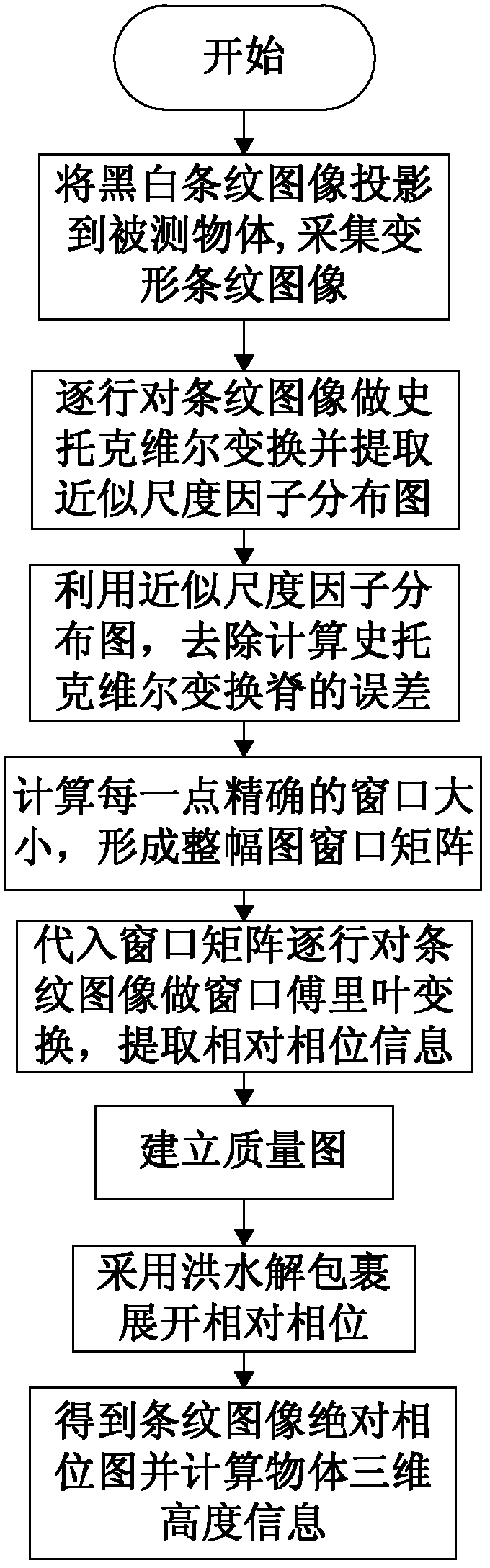

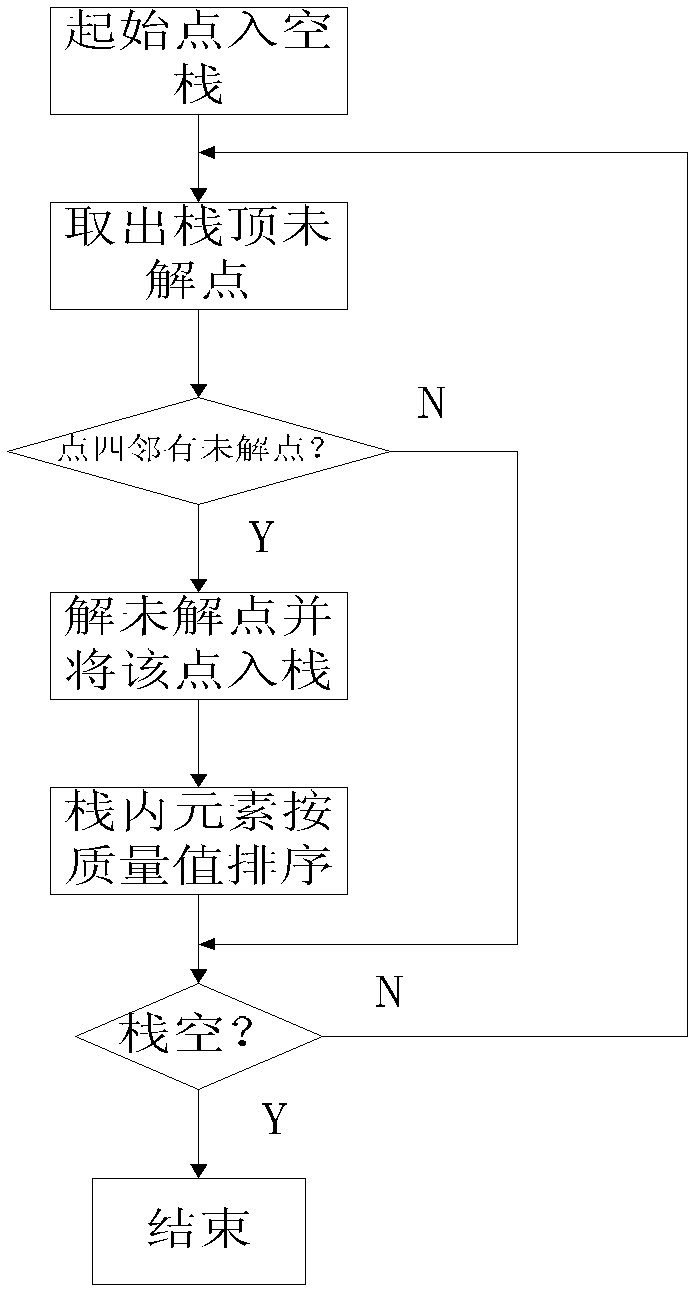

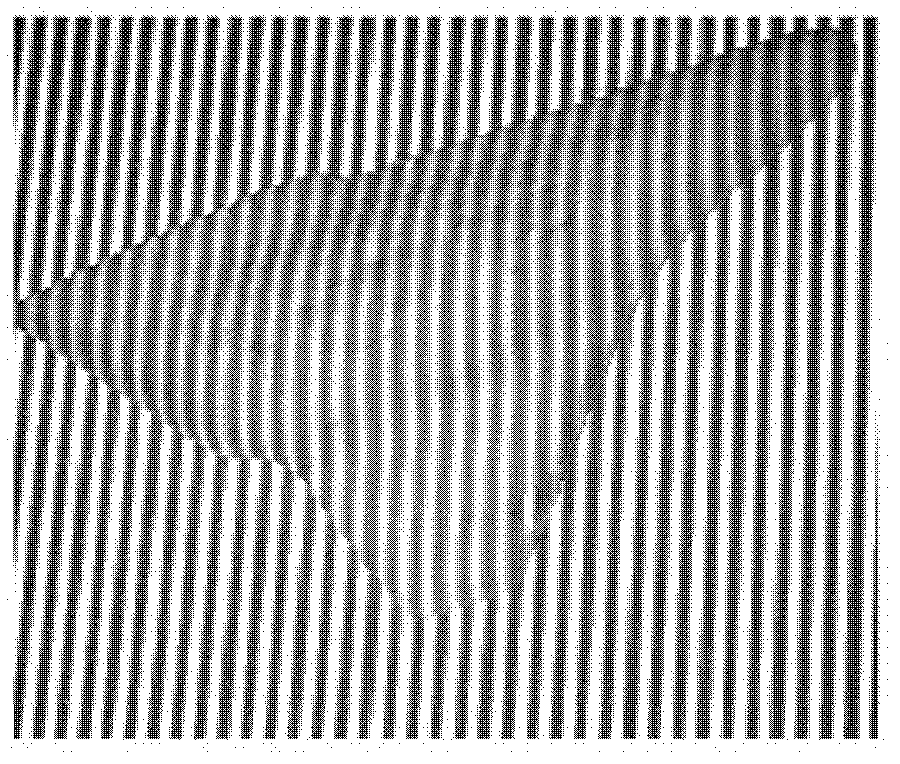

Improved window Fourier three-dimensional measurement method based on Stockwell transform

InactiveCN102620685AImprove noise immunityReduce the calculation errorUsing optical meansPhase unwrappingFlood fill

The invention relates to a new improved three-dimensional measurement method based on Stockwell transform. The invention mainly aims at precisely solving the phase distribution of a stripe image and getting three-dimensional appearance information of an object by the phase distribution. The implementation steps are as follows: projecting a black and white sine stripe image on the measured object; performing the Stockwell transform on the deformation stripe image which is collected by a CCD (charge coupled device) line by line, extracting a Stockwell transform ridge, then figuring out and removing errors caused by phase two-order derivation during the process of seeking the ridge, and finally getting a precise window size matrix; substituting the precise window matrix into a window Fourier transform, and calculating relative phase information of a deformation stripe pattern through filtration and other steps; establishing a quality map of the stripe pattern, then performing phase unwrapping by adopting a flood fill algorithm, and getting the absolute phase distribution of the stripe image; and getting the three-dimensional information of the measured object by the absolute phase distribution according to a phase-to-height conversion formula.

Owner:SOUTHEAST UNIV

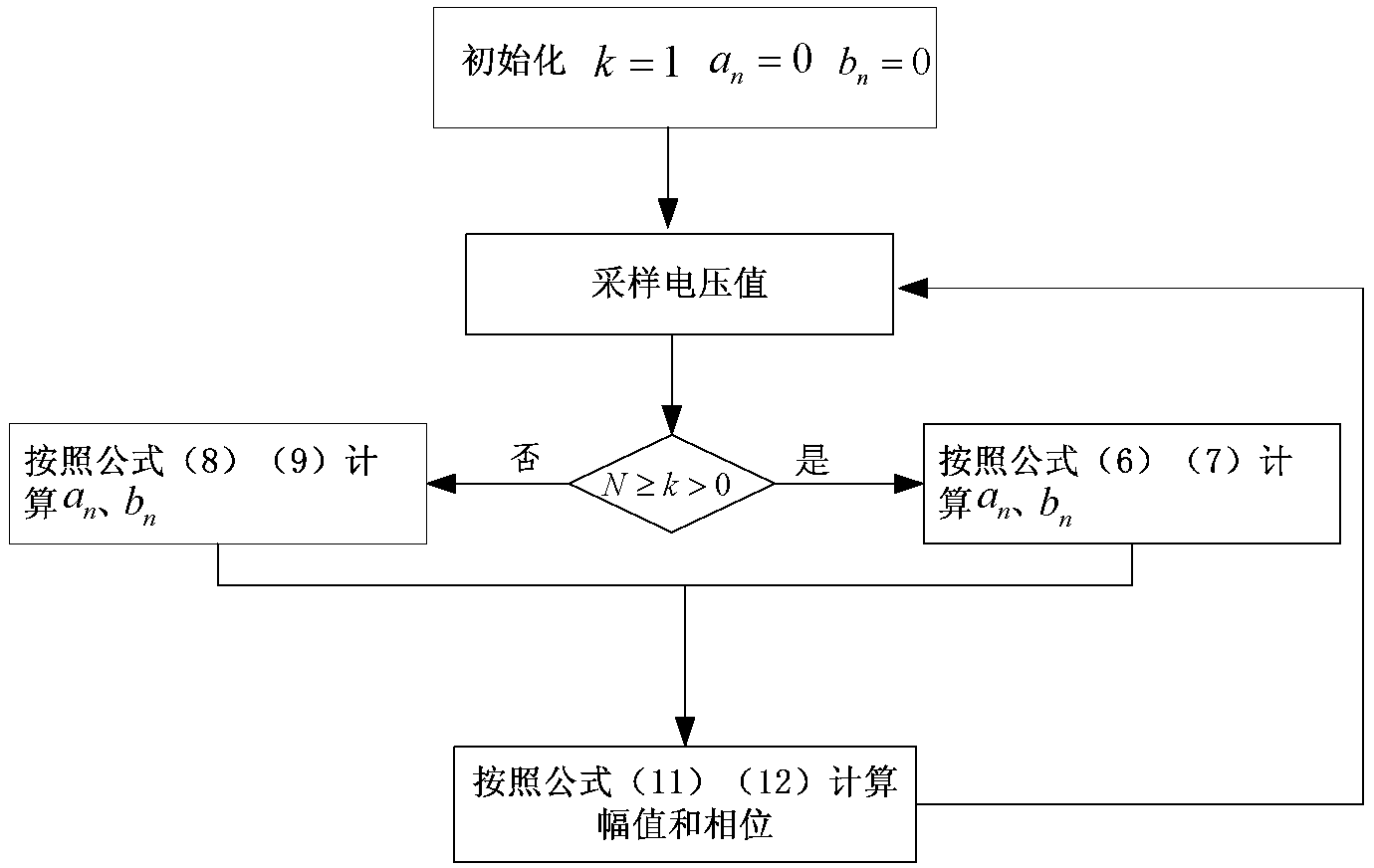

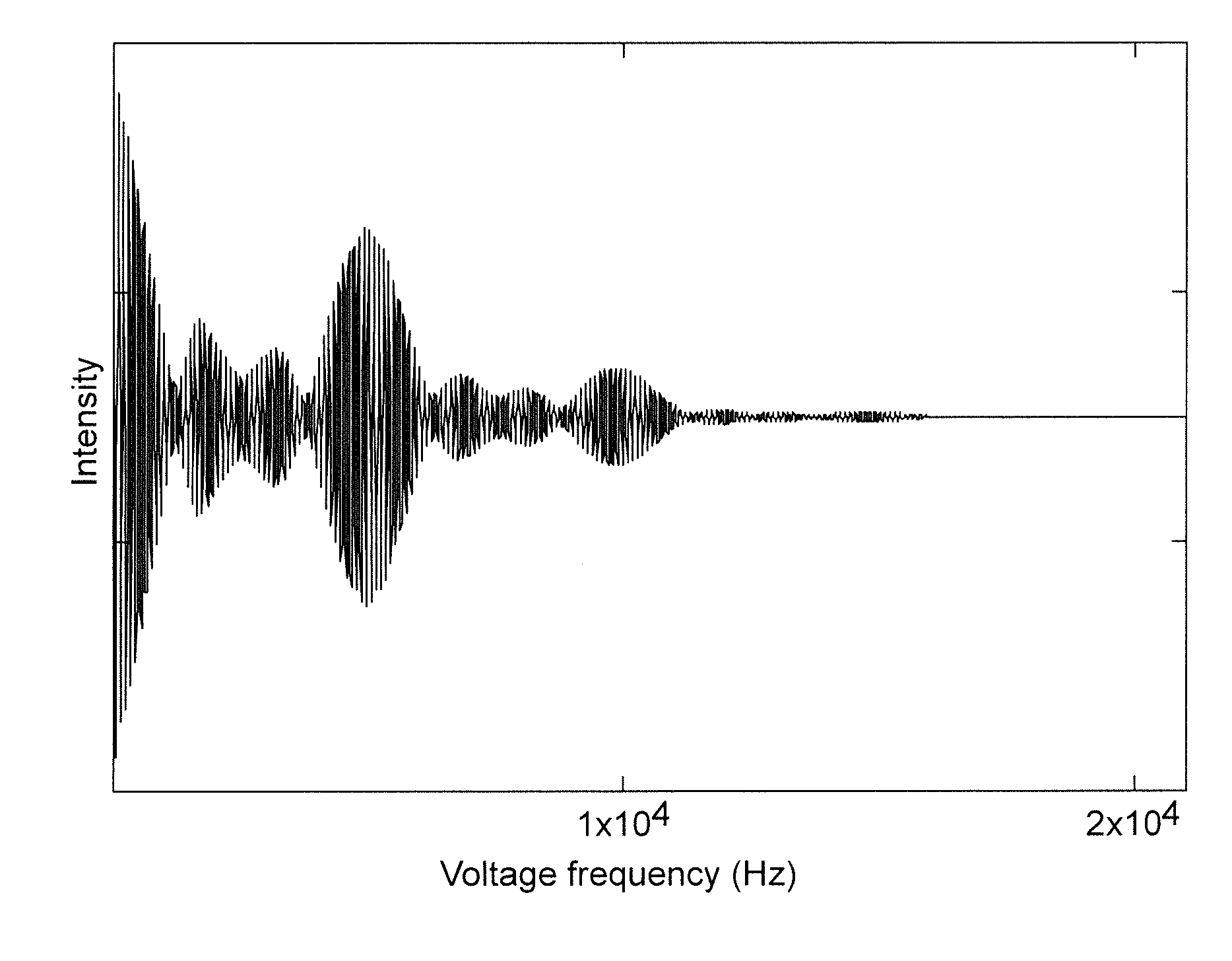

Method for calculating amplitude and phase of alternating-voltage signal based on iteration Fourier transform

ActiveCN102798748APhase accurateFast lock speedSpectral/fourier analysisCurrent/voltage measurementVoltage amplitudeHarmonic

The invention discloses a method for calculating the amplitude and phase of an alternating-voltage signal based on an iteration Fourier transform and belongs to the technical field of electric power supply. The method comprises the following steps of: determining a sampling frequency and initializing parameters; determining an alternating voltage frequency to be extracted; calculating a sine function and a cosine function; sampling an alternating voltage value; judging a sampling sequence and calculating an alternating voltage sub-harmonic cosine amplitude and a cosine amplitude; and obtaining an alternating voltage sub-harmonic voltage amplitude and the phase. The method disclosed by the invention utilizes sampling data of each time to carry out primary addition and subtraction calculation to obtain accurate fundamental wave voltage amplitude and phase; and compared with the traditional Fourier transform, a lot of calculation processes are reduced; and the requirements of the rapidness and the accuracy of signal detection of an electric power system are met.

Owner:WISDRI ENG & RES INC LTD

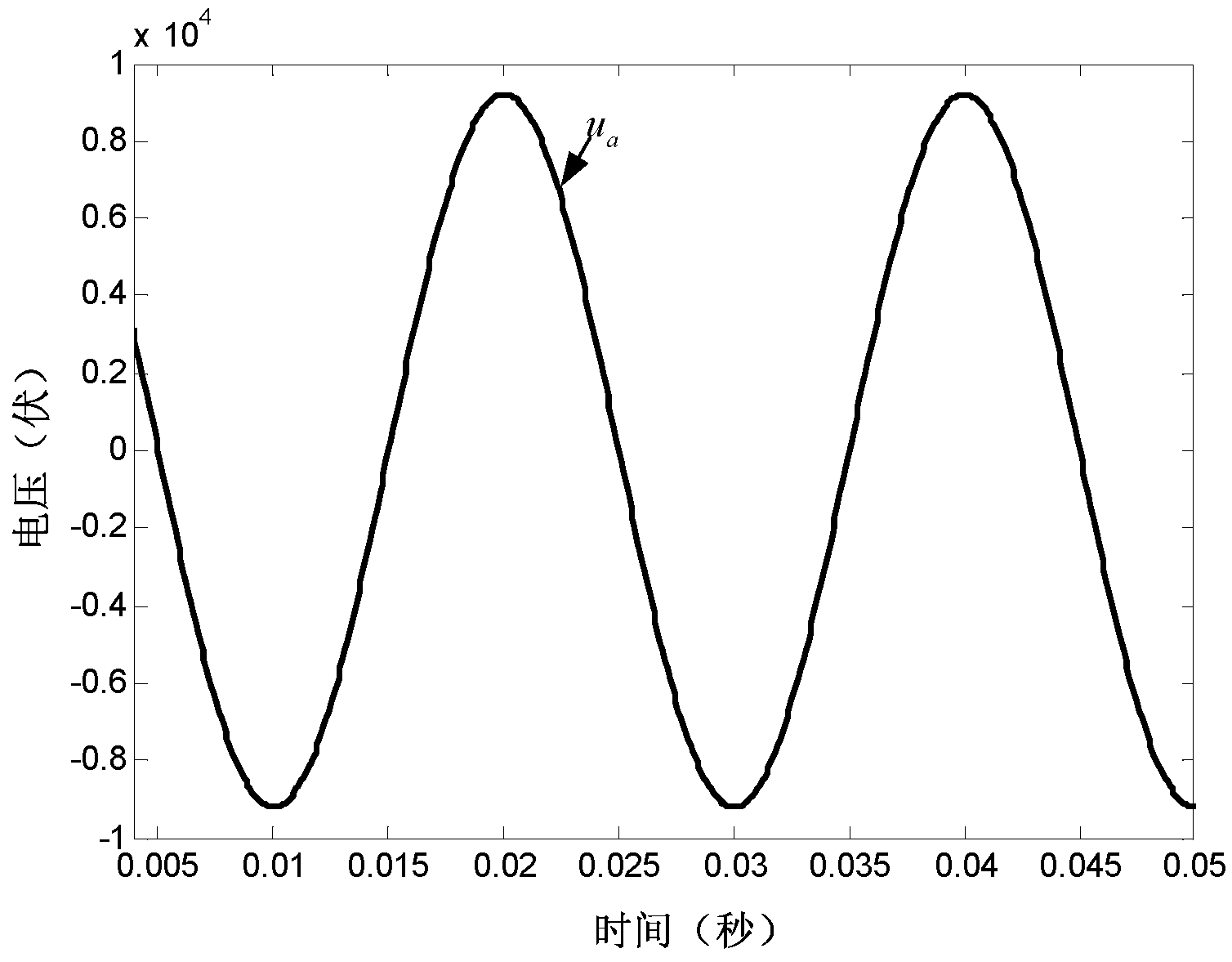

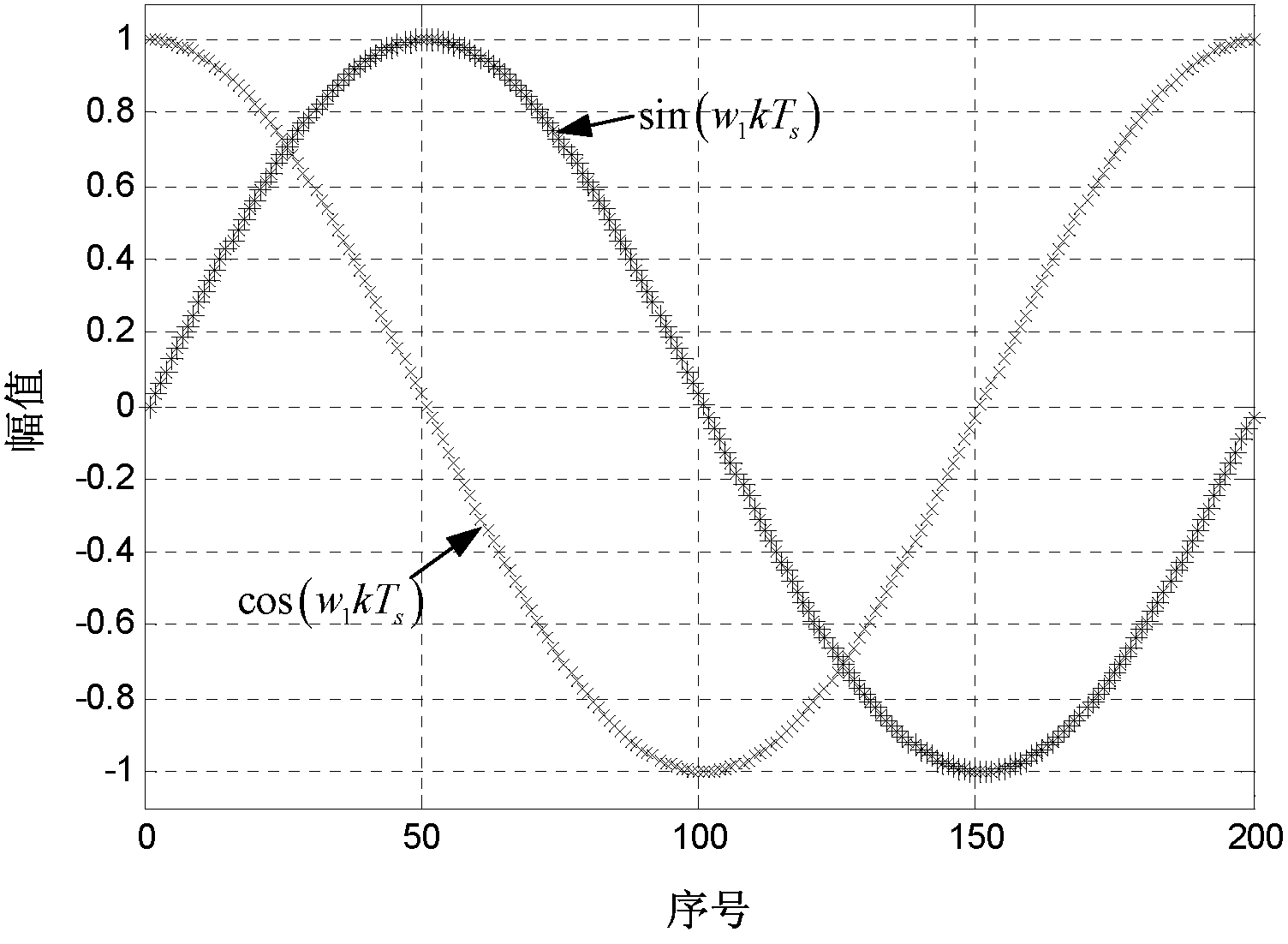

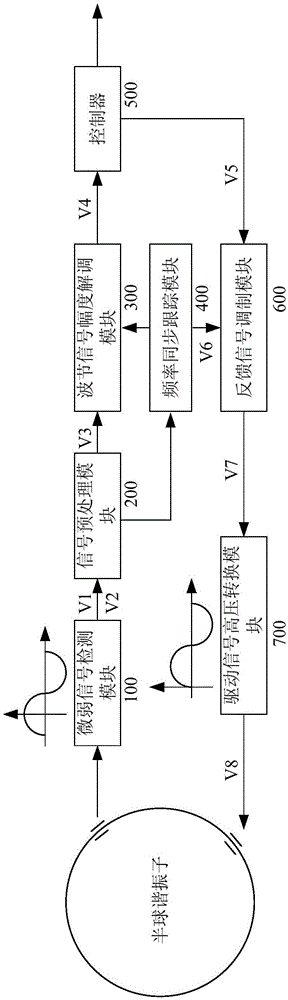

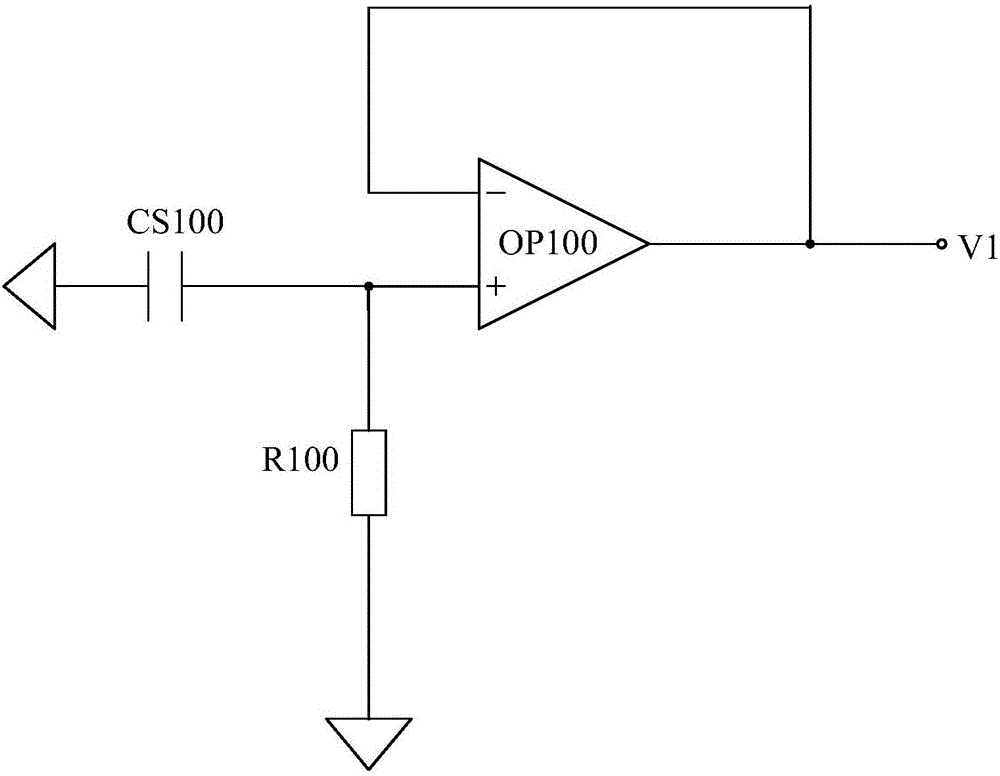

Force feedback control system and method for hemispherical resonator gyroscope

ActiveCN106482723AImprove performanceHigh measurement accuracySpeed measurement using gyroscopic effectsGyroscopes/turn-sensitive devicesControl systemHemispherical resonator gyroscope

The invention relates to a force feedback control system and method for a hemispherical resonator gyroscope and belongs to the technical field of control of inertial instruments; the control system and method are applied to a force feedback working mode of the hemispherical resonator gyroscope, and the method is a way to implement a hemispherical resonator gyroscope control method. By using a hemispherical resonator gyroscope force feedback circuit designed by using the method, it is possible to synchronously track the operating frequency of the hemispherical resonator gyroscope, demodulate the amplitude and phase of gyroscope wave node signals, and modulate high-voltage signals of force feedback control signals; in addition, not by modifying the configuration of a controller but just correcting controller parameters, it is possible to meet different environmental application needs of the hemispherical resonator gyroscope.

Owner:BEIJING INST OF CONTROL ENG

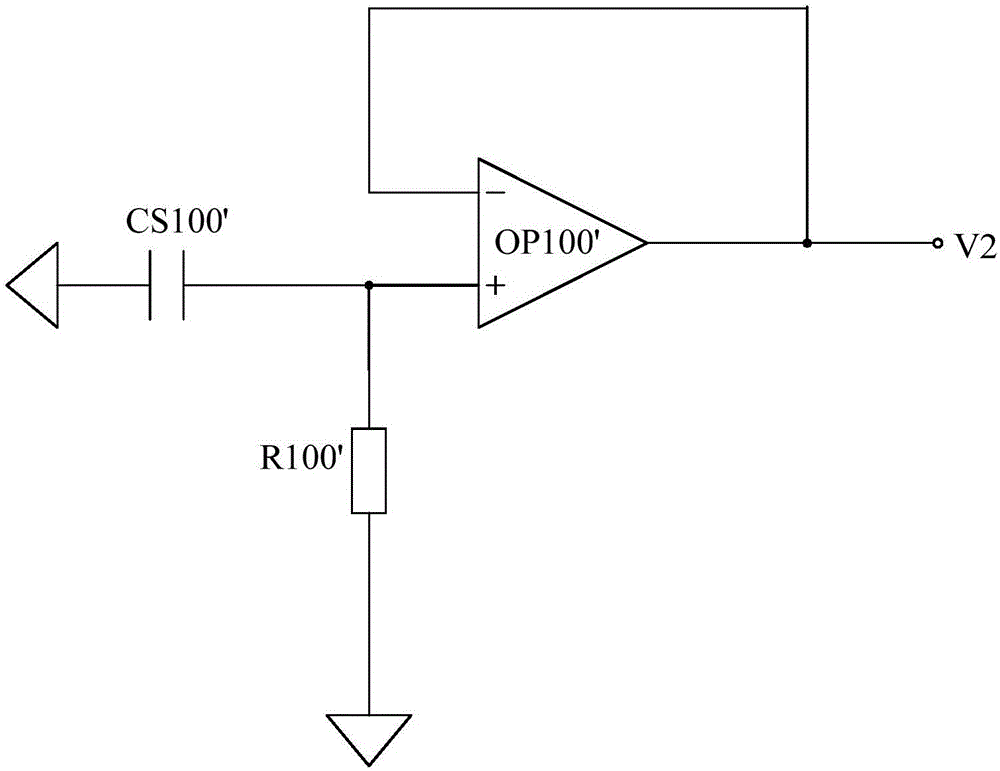

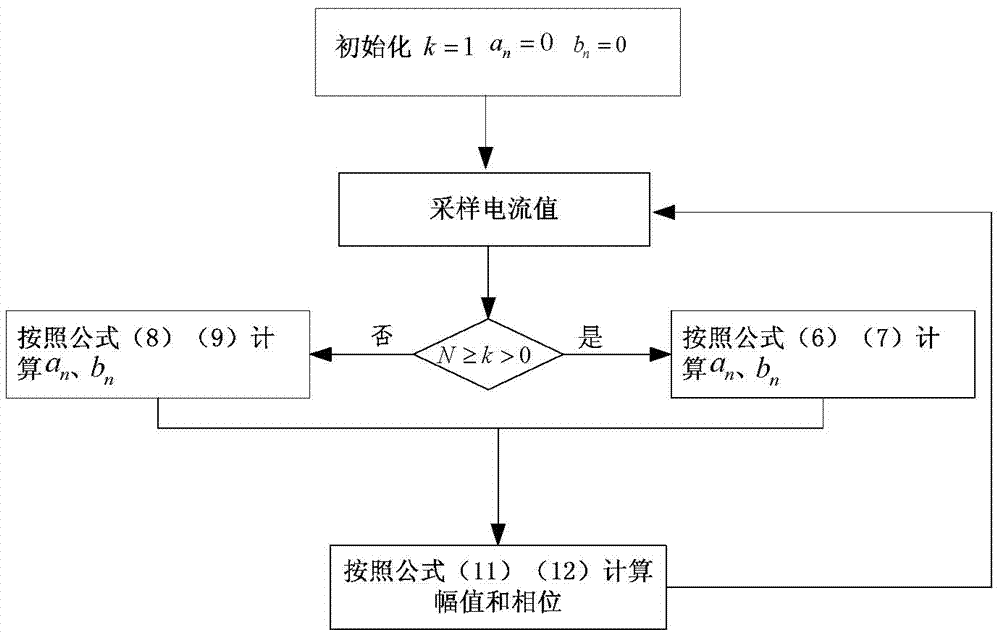

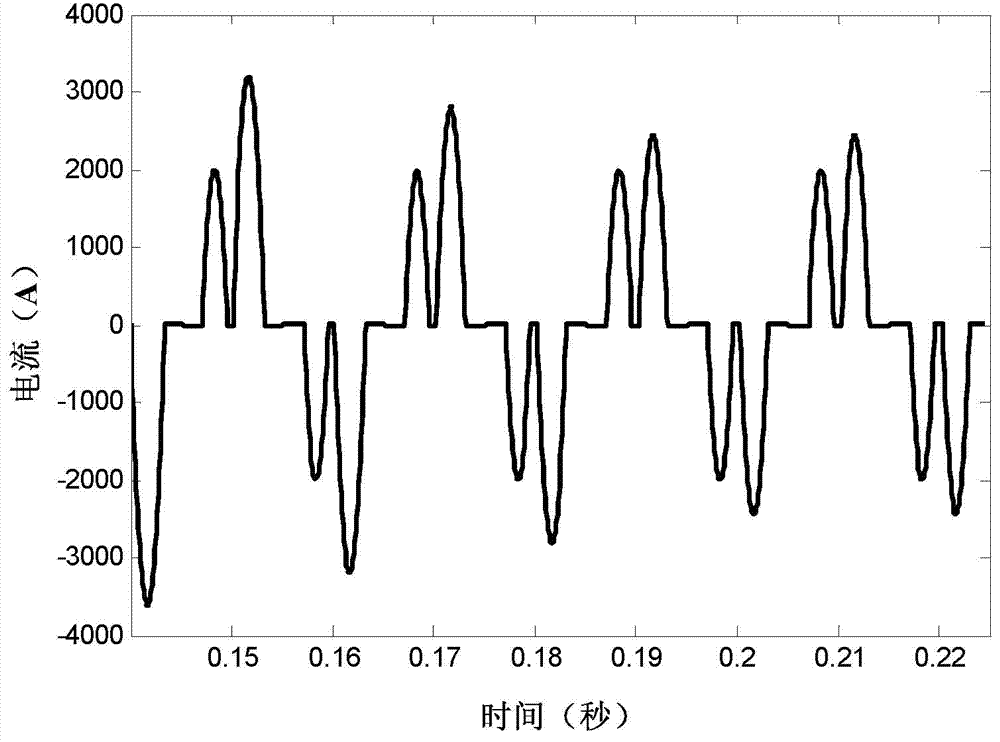

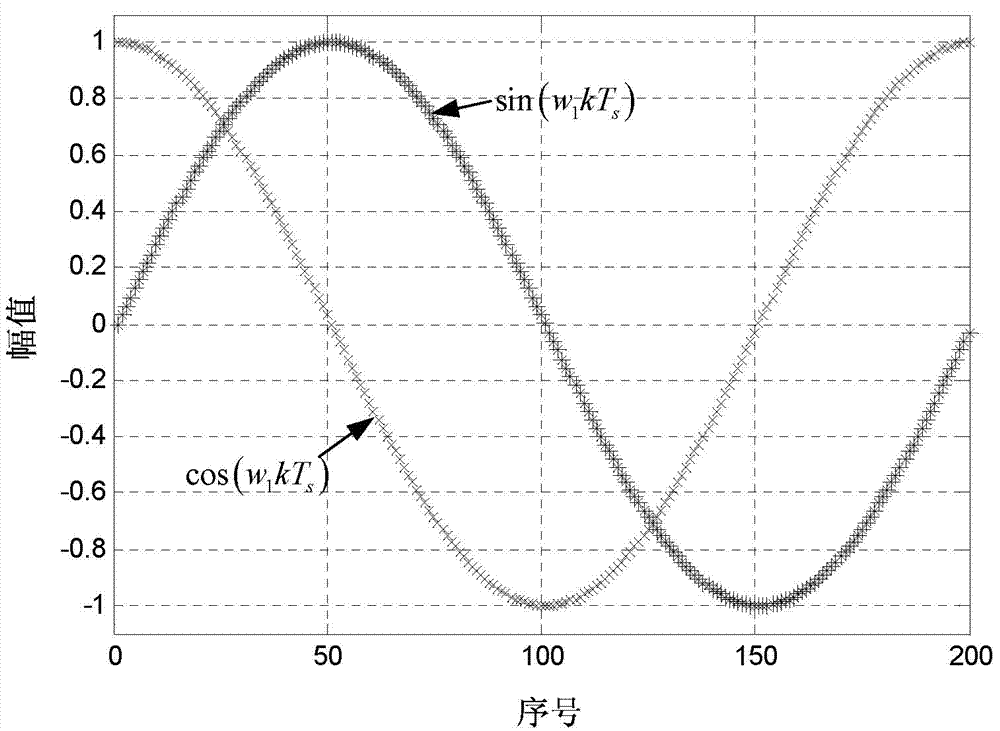

Method for calculating amplitude and phase of alternating current signal based on iterative Fourier transform

InactiveCN102818921APhase accurateFast lock speedSpectral/fourier analysisCurrent/voltage measurementElectric power systemHarmonic

The invention discloses a method for calculating the amplitude and phase of alternating current based on iterative Fourier transform, and belongs to the technical field of power supply. The method comprises the following steps of: determining sampling frequency, and initializing parameters; determining the frequency of the alternating current to be extracted; calculating a sine function and a cosine function; sampling an alternating current value; judging a sampling number, and calculating the cosine amplitude and sine amplitude of sub-harmonics of the alternating current; and obtaining the amplitude and phase of sub-harmonic current of the alternating current. Accurate fundamental current amplitude and phase can be obtained by performing addition and subtraction once on data obtained by the sampling of each time; and compared with the conventional Fourier-transform-based method, the method has the advantages that calculation processes are greatly reduced, and requirements for the high speed and accuracy of signal detection in a power system can be met.

Owner:TIANJIN ZHONGKE HUARUI ELECTRICAL TECH DEV CO LTD

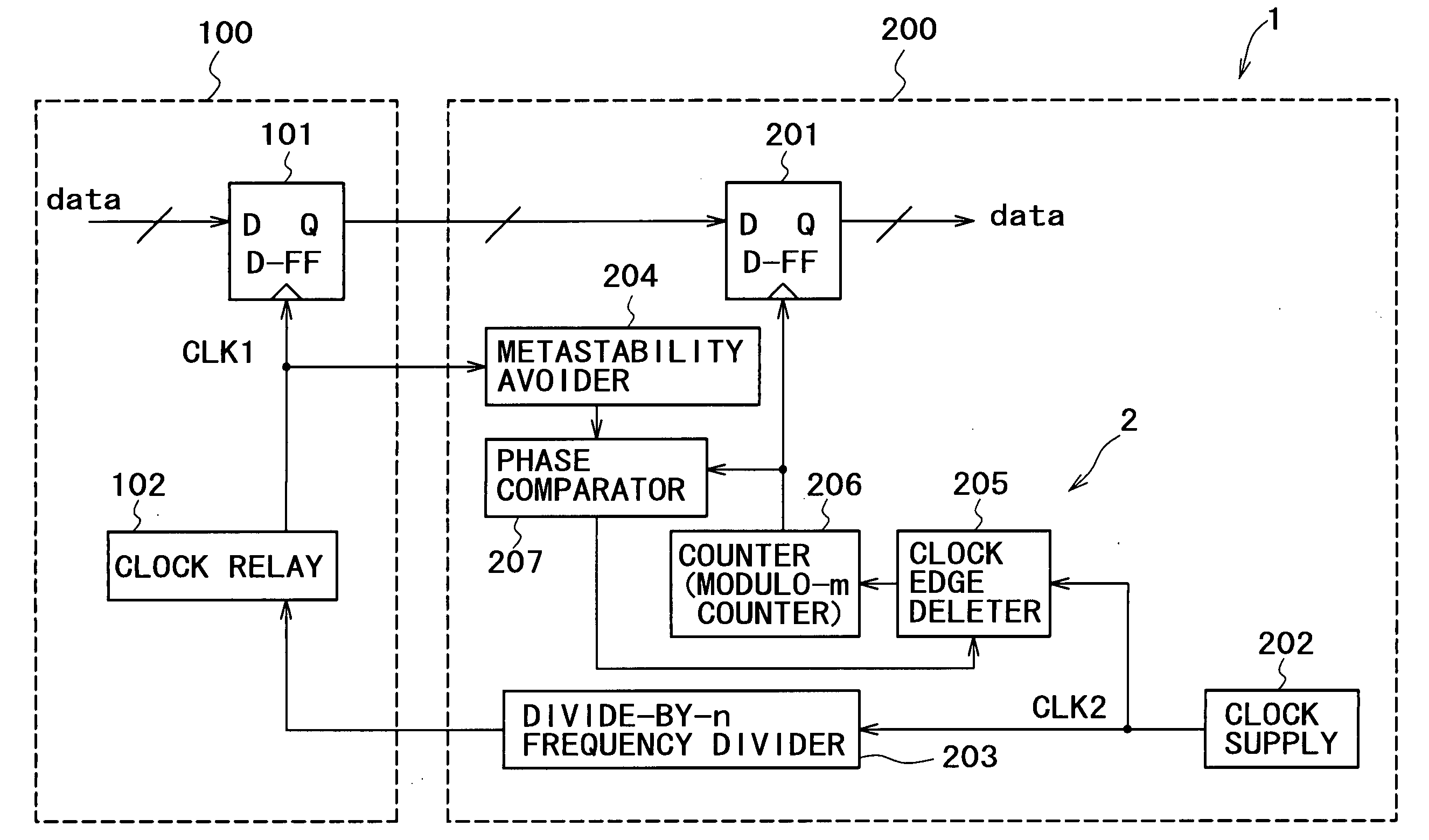

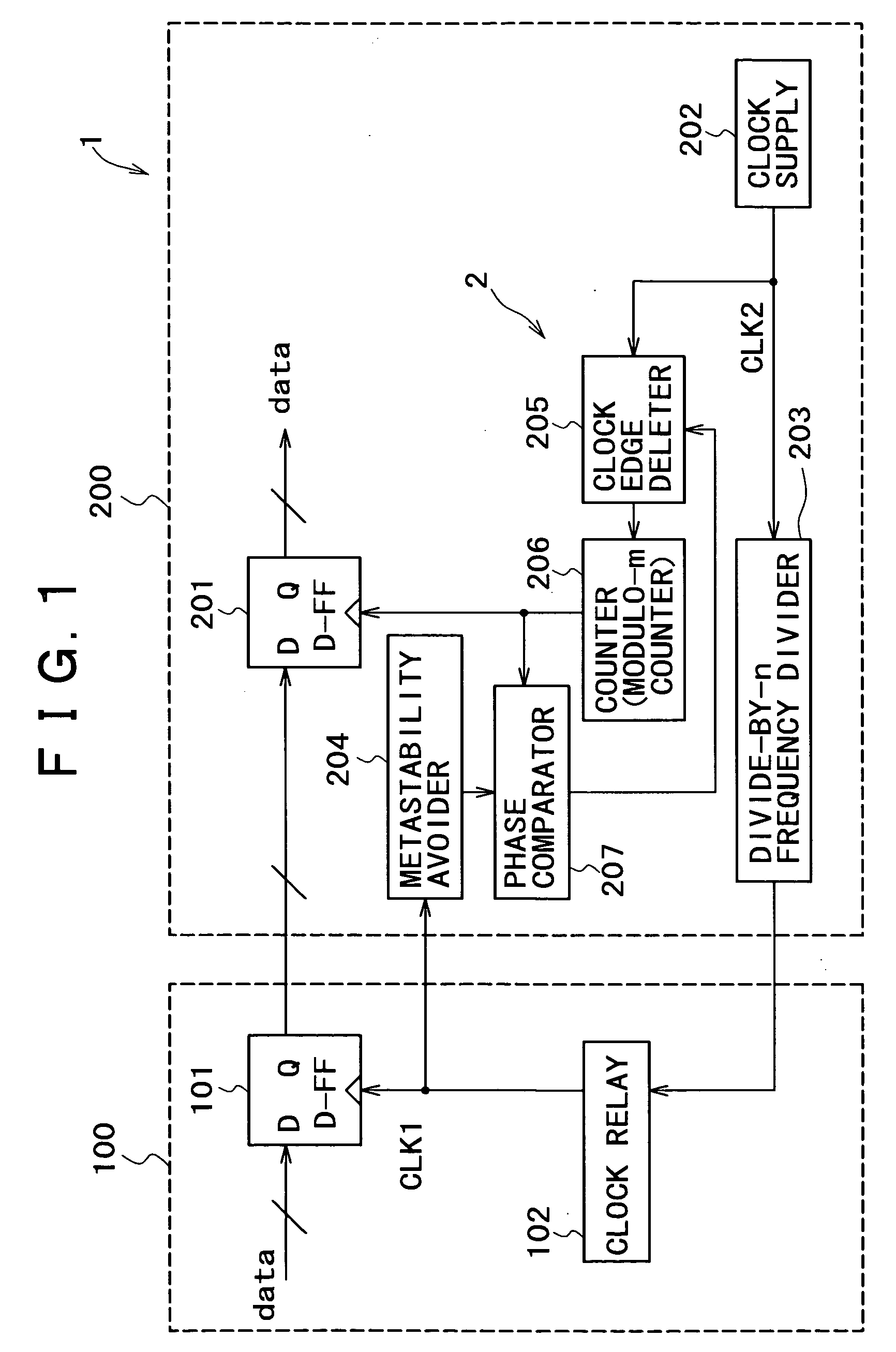

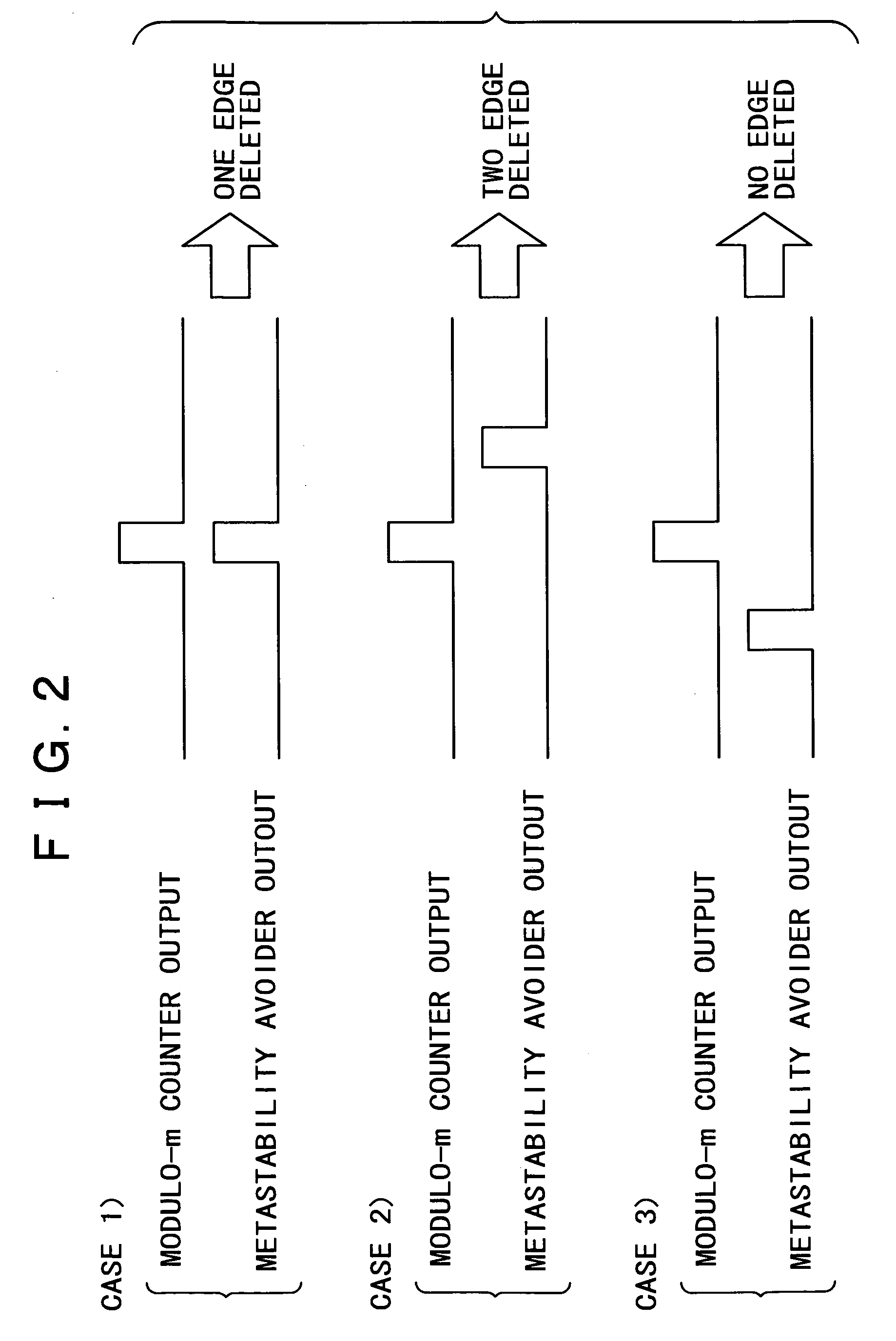

Data transmission system and data transmission apparatus

InactiveUS20050111572A1Reduce circuit sizeReduce power consumptionSynchronisation information channelsSynchronisation signal speed/phase controlClock shiftComparator

A data transmission system having a clock shift compensating function is designed for a reduced circuit scale and reduced electric power consumption. A data transmission D flip-flop in a transmitter is supplied with a clock signal for transmitting data from a clock delay. A transmitter has a data reception D flip-flop, a clock supply, a divide-by-n frequency divider for frequency-dividing a clock signal, and a metastability avoider for removing a metastable state from a clock signal received via the clock delay. The transmitter also has a phase comparator for comparing output signals from the metastability avoider and a modulo-m counter, and a clock edge deleter for controlling the number of pulses or edges of the clock signal from the clock supply depending on an output signal from the phase comparator. Pulses of the clock signal from the clock edge deleter are counted by the counter and supplied to the data reception D flip-flop.

Owner:SONY CORP

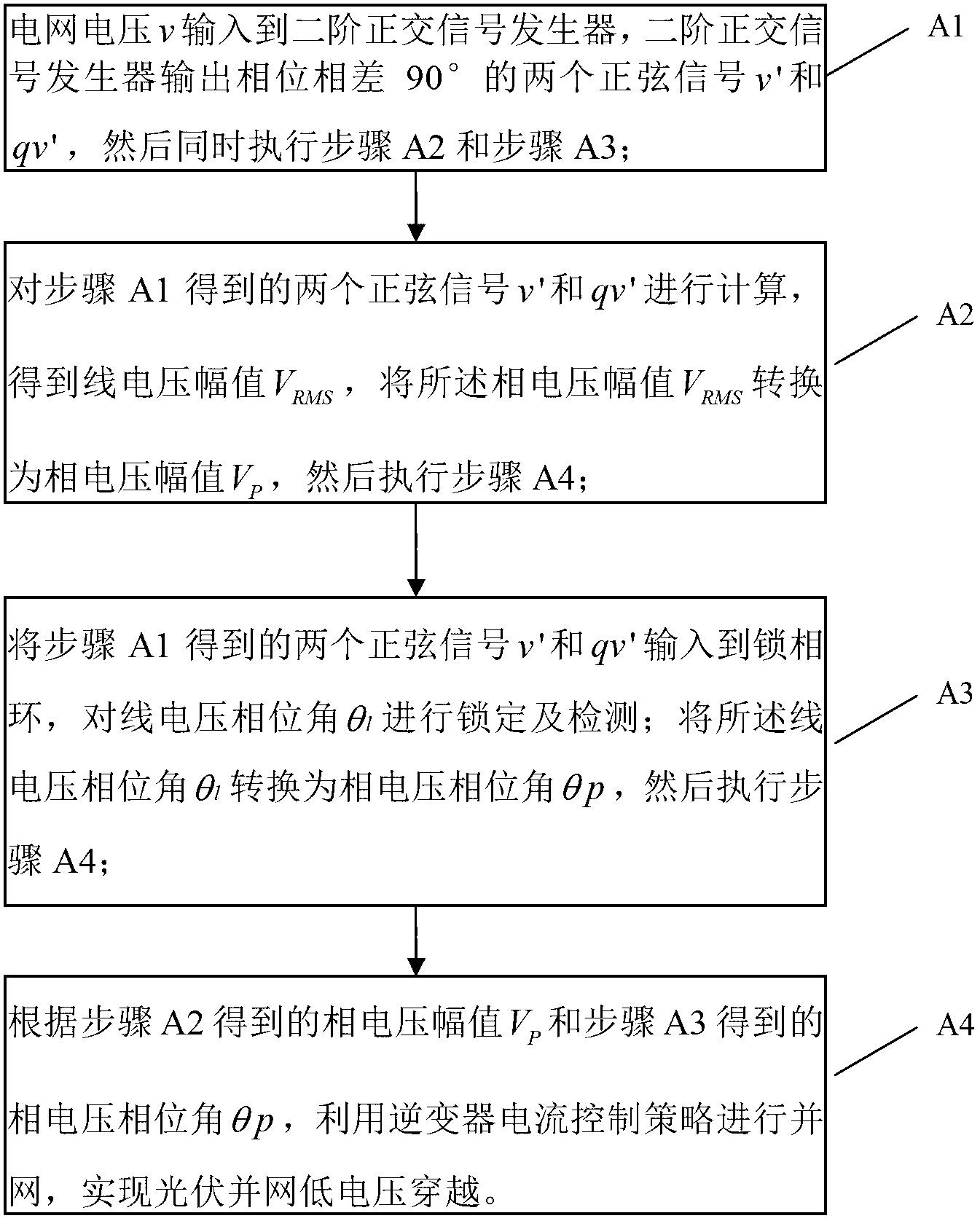

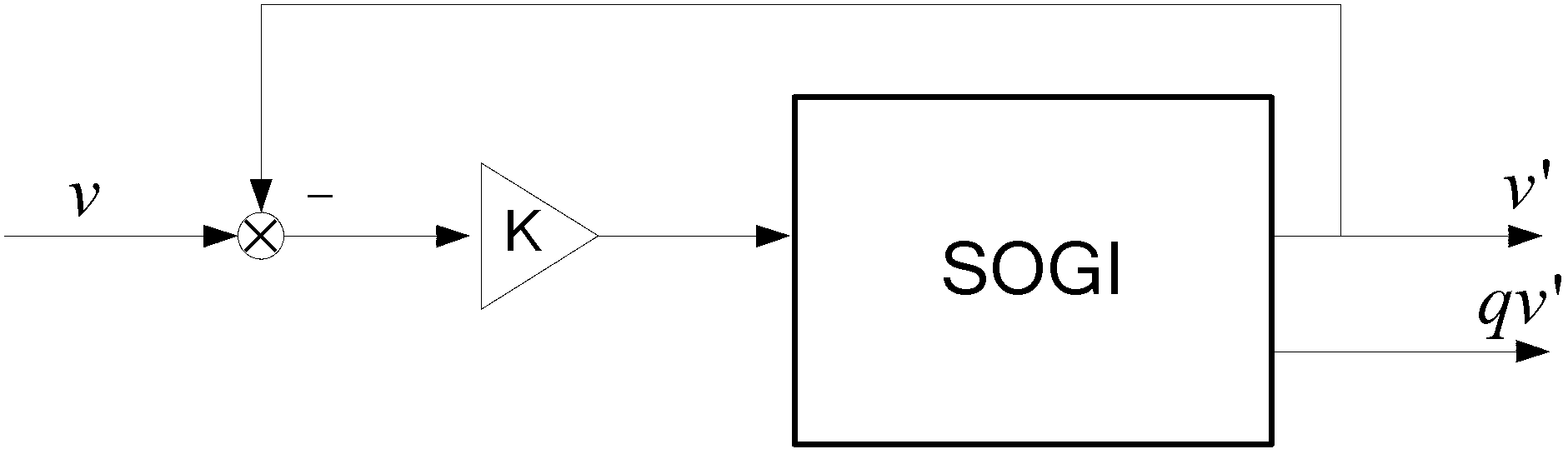

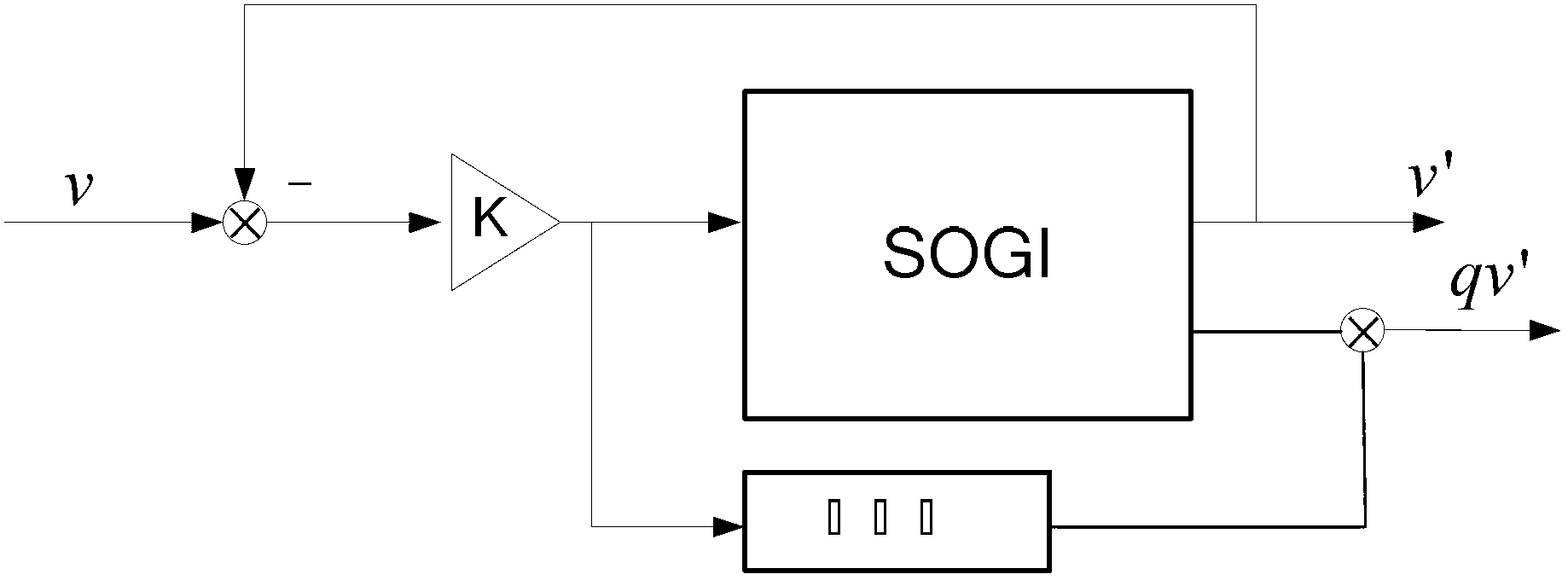

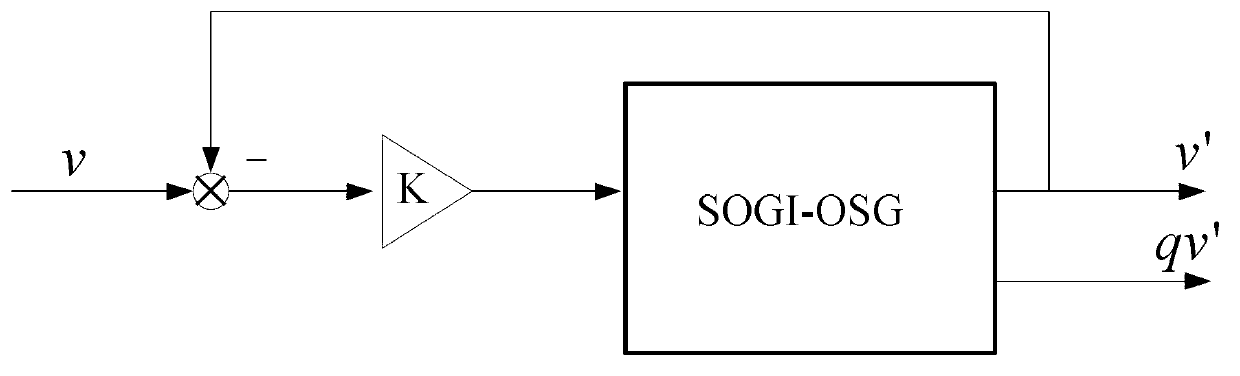

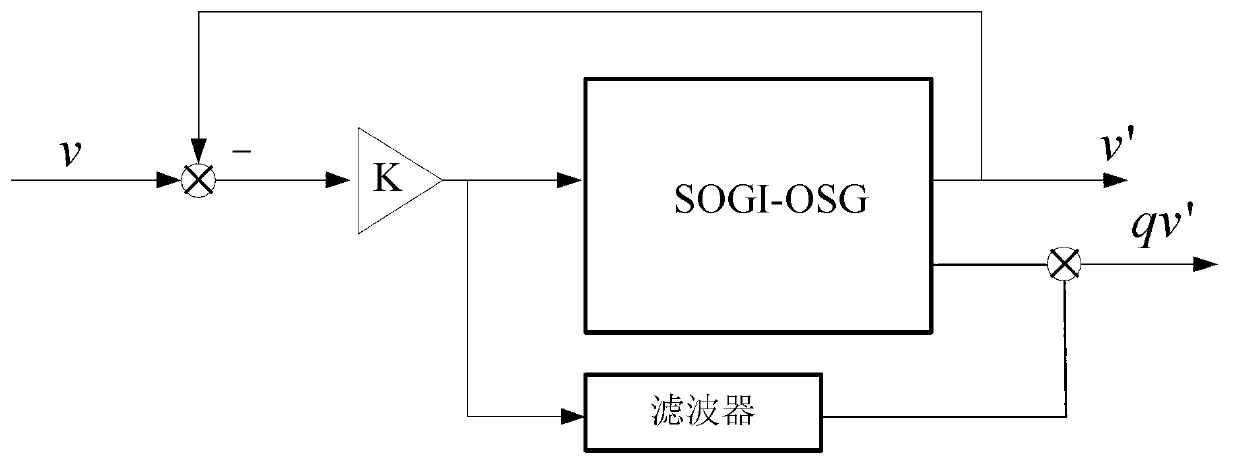

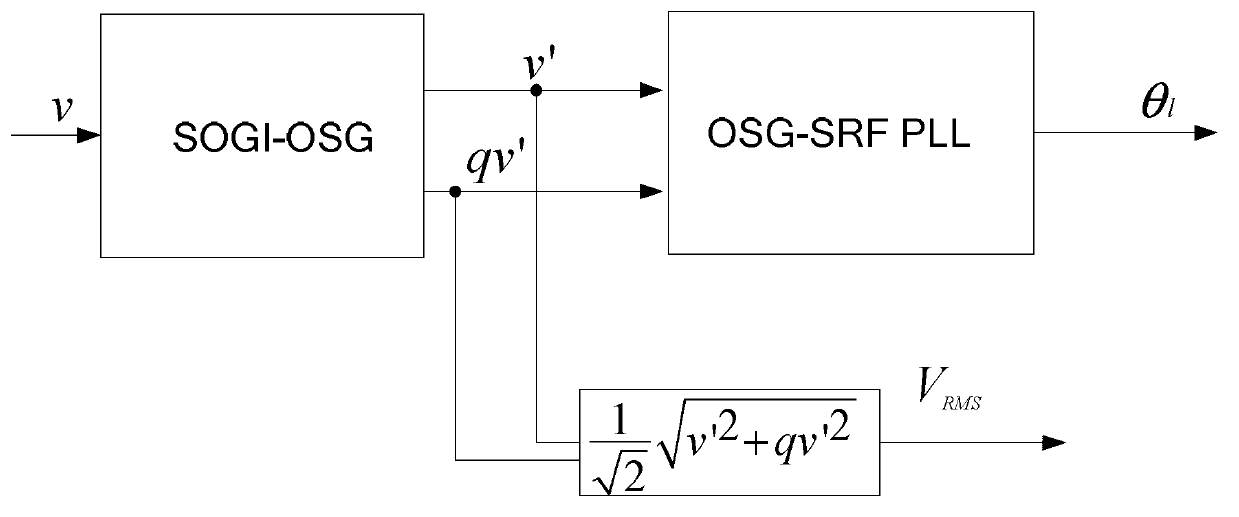

Three-phase phase-locked loop method appropriate for photovoltaic grid connected low voltage ride through

InactiveCN103219731AEliminate the effects ofPhase accurateVoltage-current phase angleAc network voltage adjustmentVoltage amplitudeSolar power

The invention provides a three-phase phase-locked loop method appropriate for photovoltaic grid connected low voltage ride through and relates to the field of solar power generation power supply, in particular to a three-phase phase-locked loop which has a function of low voltage ride through. The three-phase phase-locked loop method appropriate for the photovoltaic grid connected low voltage ride through solves the problems that an existing phaselock technique needs to consider influences of zero wander, and an existing detection method does not consider influences brought by measuring voltage deviation on voltage detection. The three-phase phase-locked loop method appropriate for photovoltaic grid connected low voltage ride through includes a first step of inputting network voltage v to a second-order orthogonal signal generator and outputting two sinusoidal signals v' and qv', wherein phases of the two sinusoidal signals differs by 90 degrees; a second step of calculating the signals v' and qv', obtaining line voltage amplitude VRMS, and converting the line voltage amplitude VRMS into phase voltage amplitude VP; a third step of inputting the signals v' and qv' into the phase-locked loop, locking a line voltage phase angle theta1, detecting the line voltage phase angle theta1, and converting the line voltage phase angle theta1 into phase voltage phase angle thetap; and a fourth step of conducting grid connection according to the phase voltage amplitude VP and the phase voltage phase angle thetap by means of an inverter current control strategy, and achieving the photovoltaic grid connected low voltage ride through. The three-phase phase-locked loop method appropriate for the photovoltaic grid connected low voltage ride through is appropriate for photovoltaic power stations.

Owner:WUXI MEIKAI ENERGY TECH

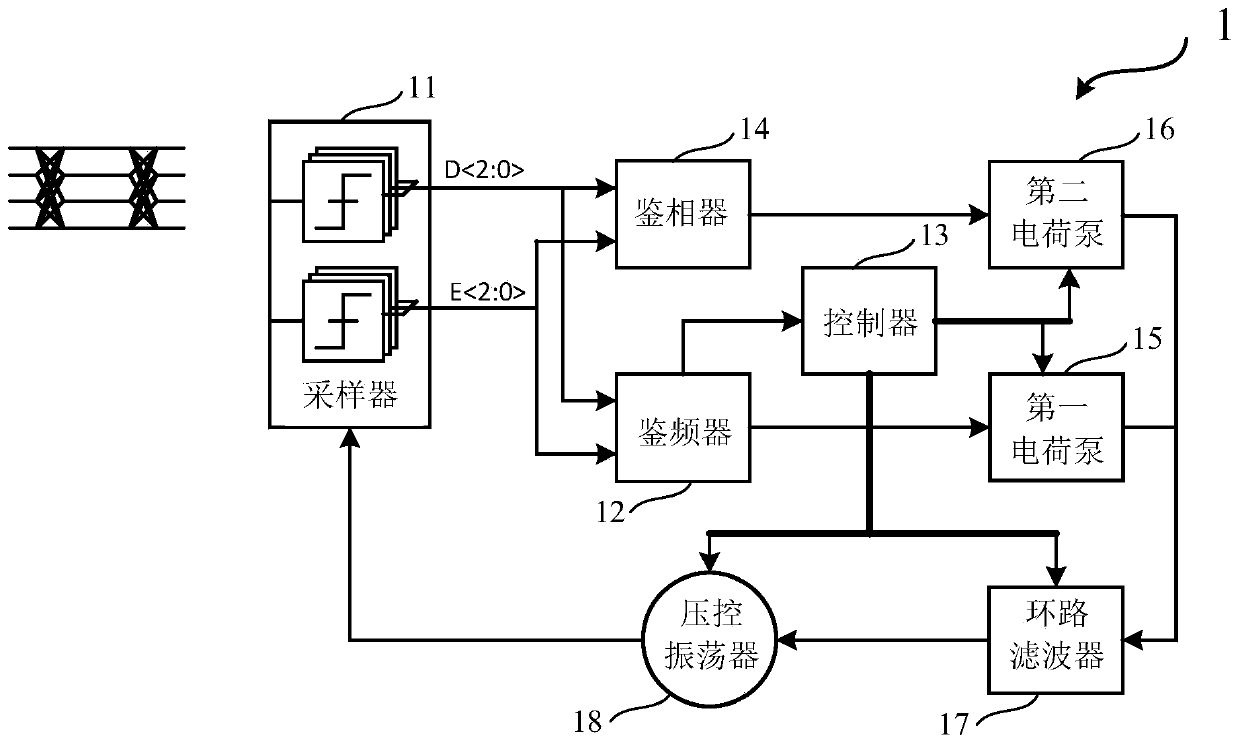

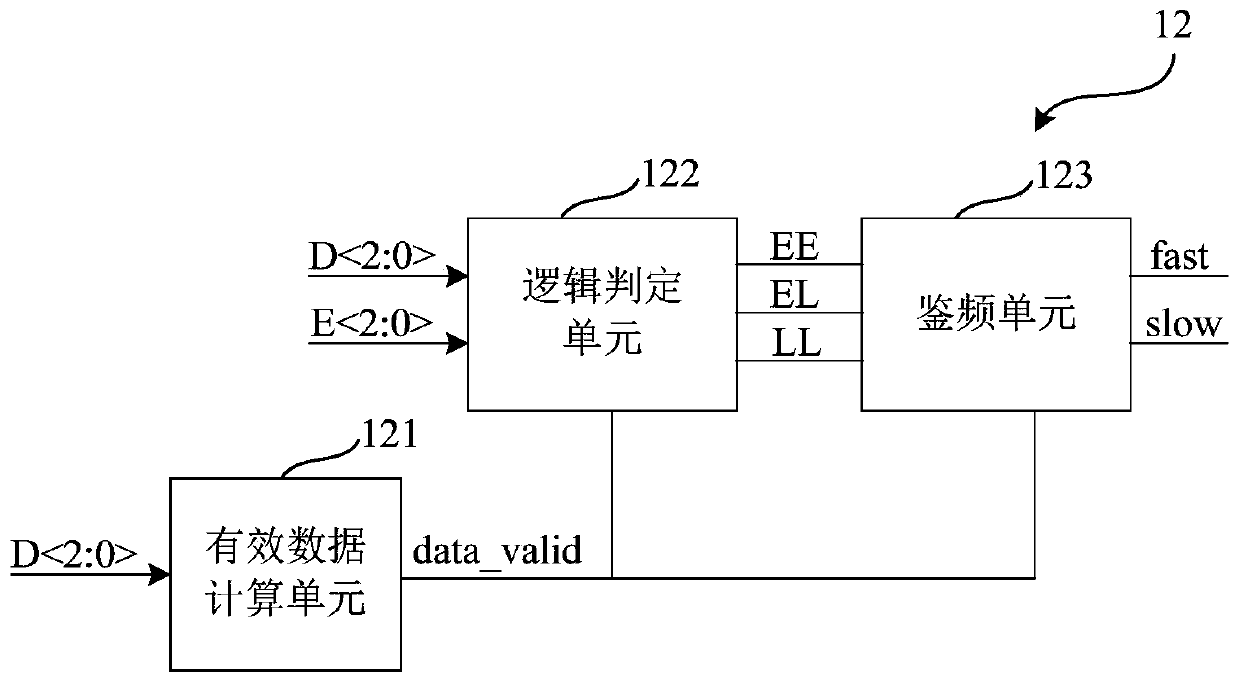

Frequency discriminator, PAM4 clock data frequency locking method, recovery method and circuit

ActiveCN109787615AReduce frequencyLower requirementPulse automatic controlDiscriminatorRecovery method

The invention provides a frequency discriminator, a PAM4 clock data frequency locking method, a PAM4 clock data frequency recovery method and a PAM4 clock data frequency locking circuit. The method comprises the following steps: respectively sampling data and edges of an input signal by adopting a data and edge sampling clock; Obtaining a logic result of the speed of the sampling clock according to the sampling data of at least two adjacent clock periods and the sampling edge between the two sampling data; Determining the frequency of the sampling clock relative to the input signal based on the logic results of at least three adjacent clock periods, and enabling the frequency of the sampling clock to be equal to that of the input signal; based on the Bang-Bang logics, adjusting the phase of the sampling clock, so that the sampling edge of the sampling clock is respectively positioned in the data of the input signal and the middle area of the edge. The non-reference clock frequency locking and phase locking technology is adopted, so that the frequency and the phase can be accurately locked; The requirement for the frequency difference between the starting frequency of the voltage-controlled oscillator and an input signal is low, the clock data recovery function of the large-range input data rate can be supported, the application range is wide, and the stability is high.

Owner:PHOTONIC TECH SHANGHAI CO LTD

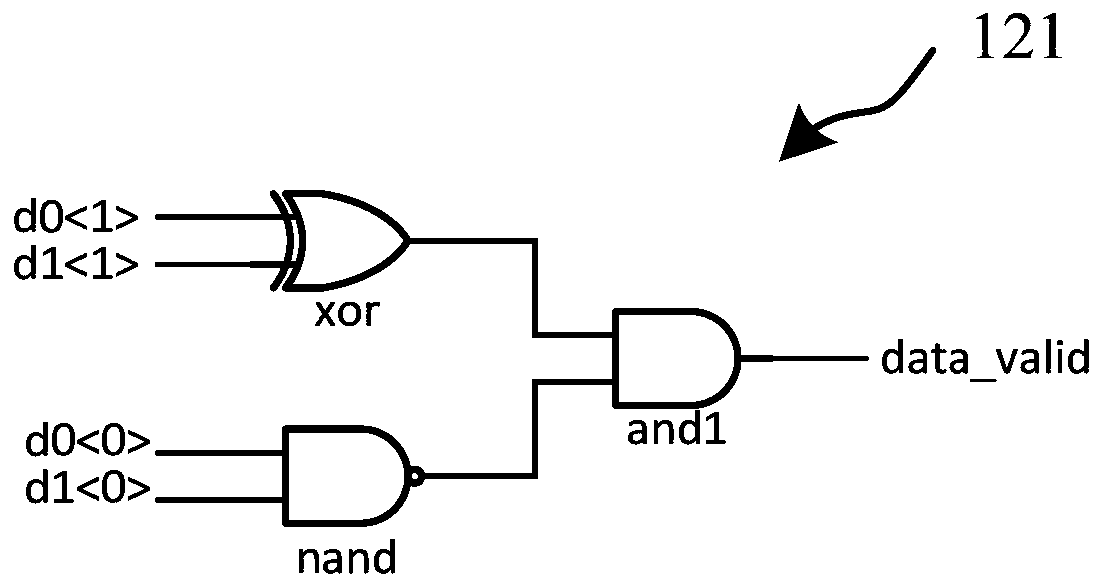

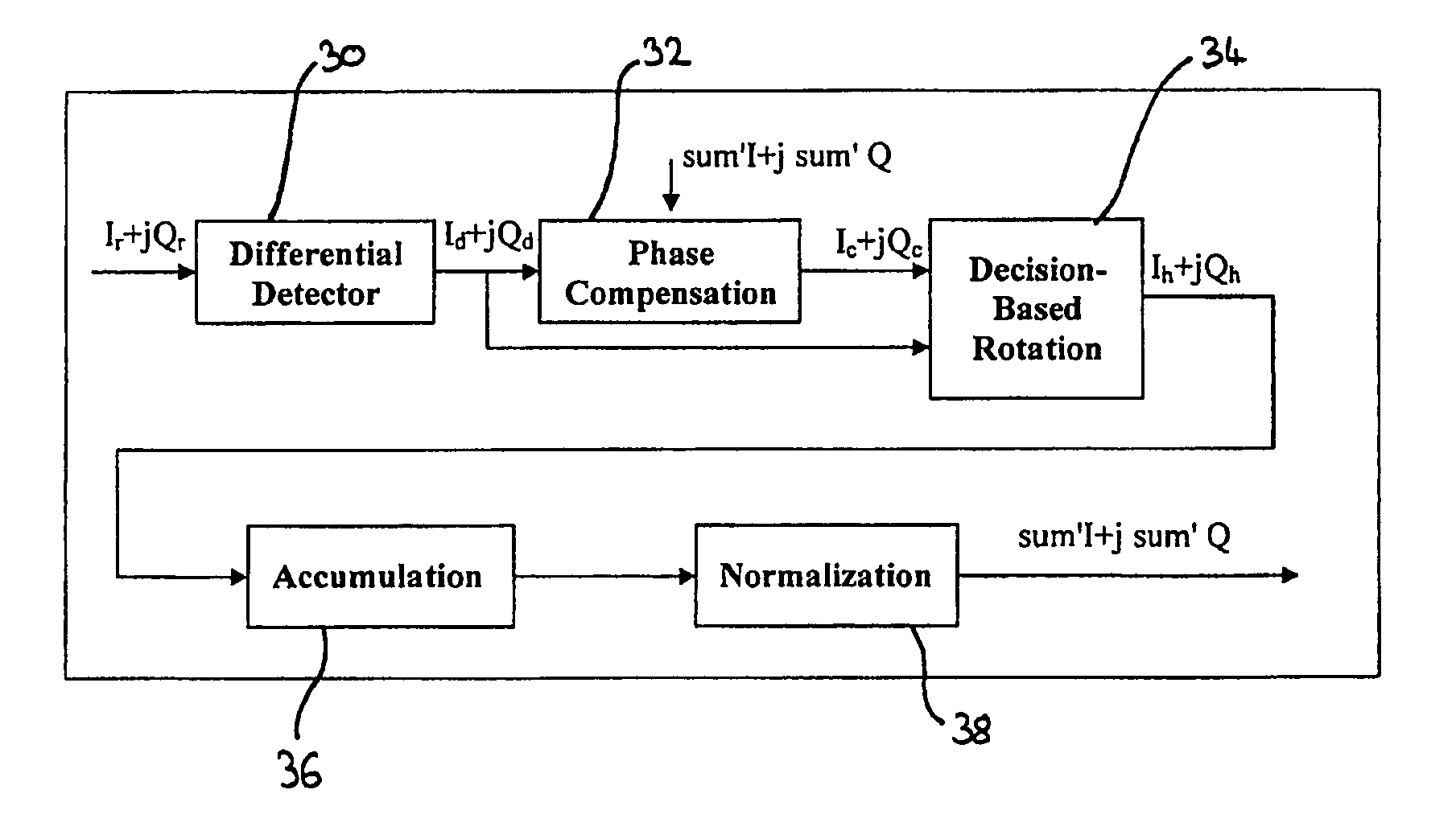

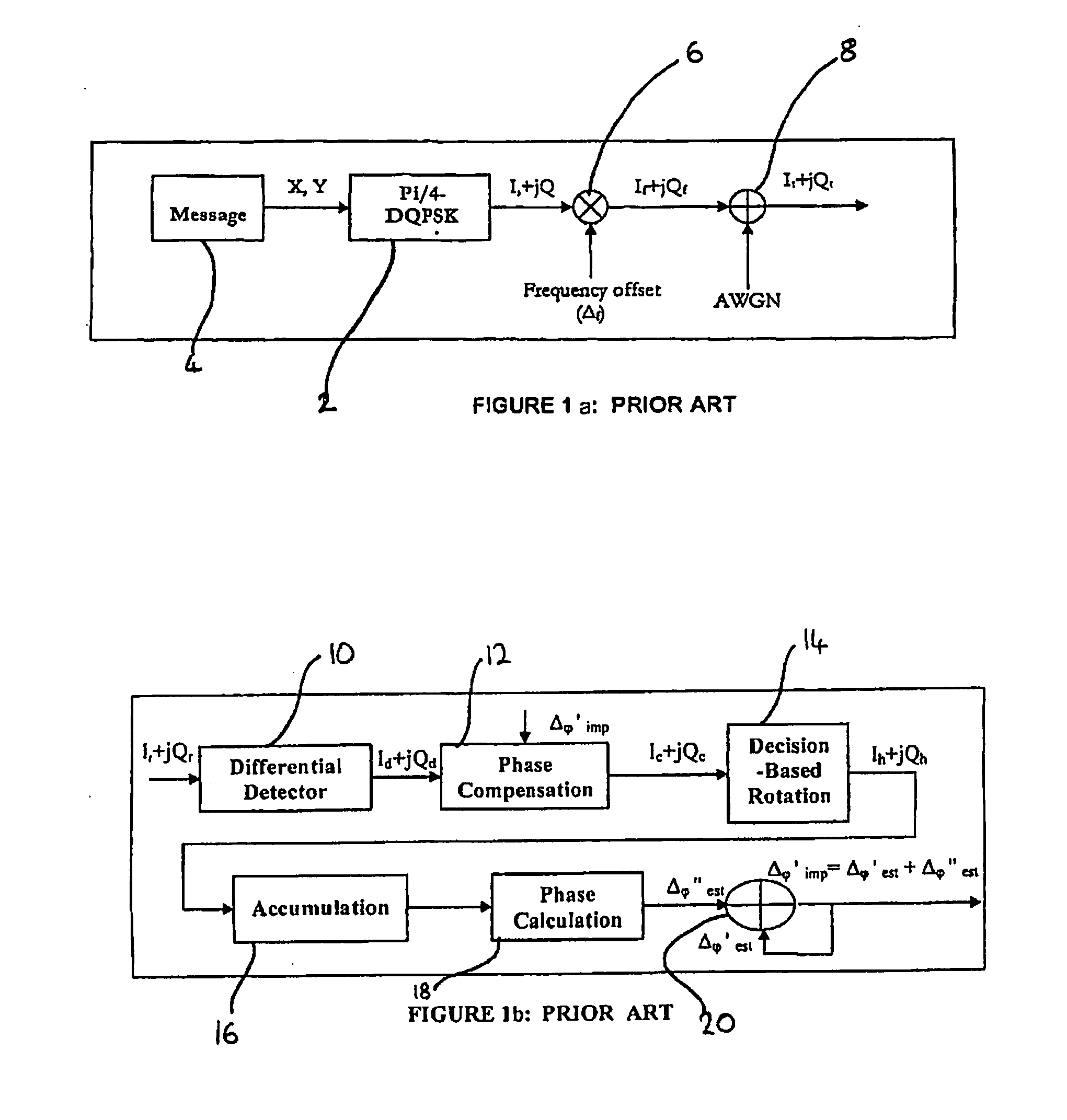

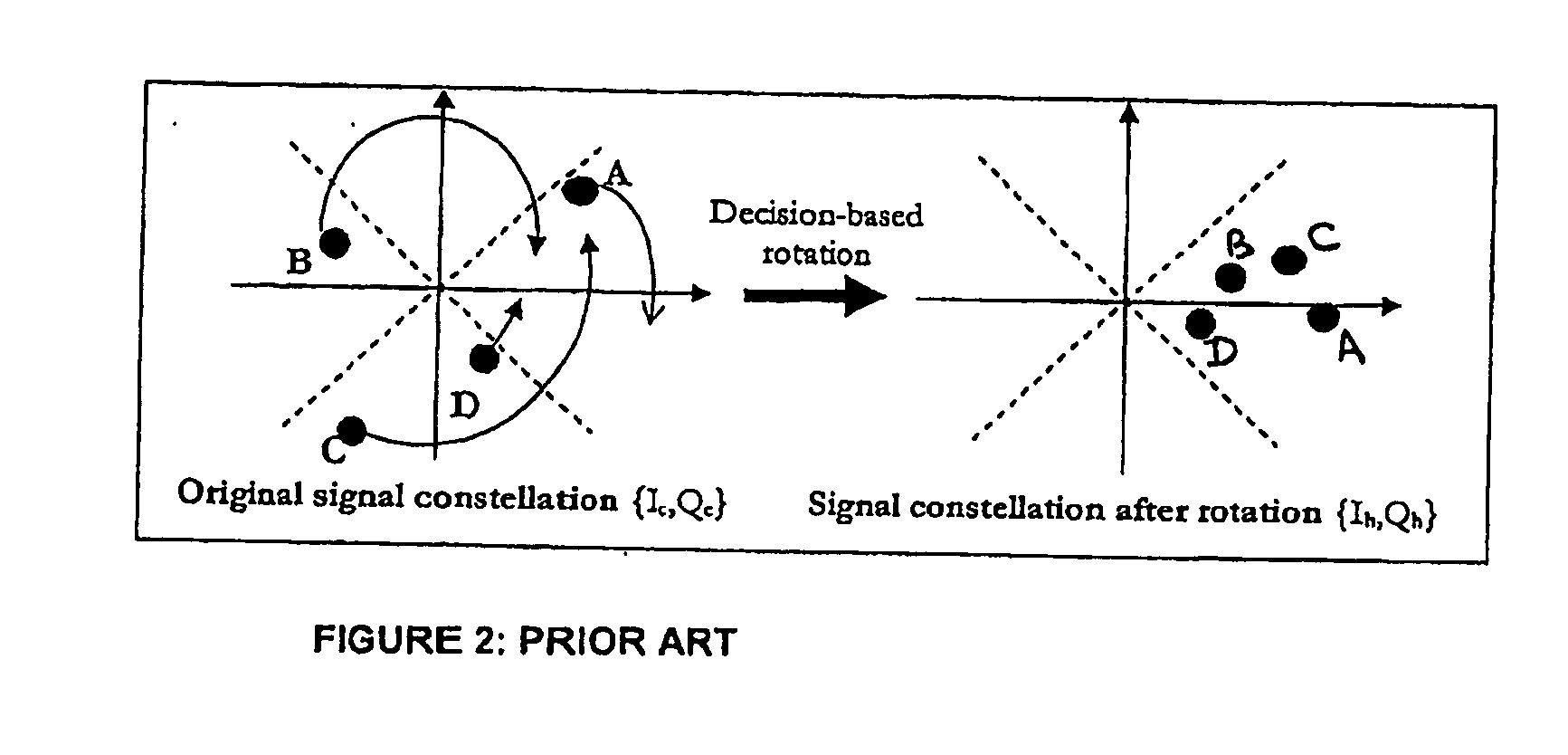

System and method for estimating phase offset in a communication system

InactiveUS20070192048A1Simple hardware implementationPhase accurateNoise figure or signal-to-noise ratio measurementAmplifier modifications to reduce noise influenceCommunications systemLocal oscillator

A system and method for estimating phase offset between a local oscillator and a transmitted input signal in a communication system comprises a differential detector and a phase compensation stage for compensating for phase errors in an output signal from the differential detector. The output signal from the differential detector is rotated in a decision-based rotation stage coupled to the outputs of the differential detector and the phase compensation stage. The rotation is based on a decision made using the output signal from the phase compensation stage. An accumulation stage accumulates the output signal from the decision-based rotation stage for a number of symbols in the transmitted input signal. A normalization stage normalizes the output signal from the accumulation stage and the normalized output signal corresponds to a phase offset of the local oscillator relative to the transmitted input signal. The phase compensation stage has a further input to which the phase offset is applied to compensate the phase of a subsequently received symbol in the transmitted input signal. The phase offset between the local oscillator and the transmitted input signal is then estimated.

Owner:OKI TECHNO CENT SINGAPORE PTE

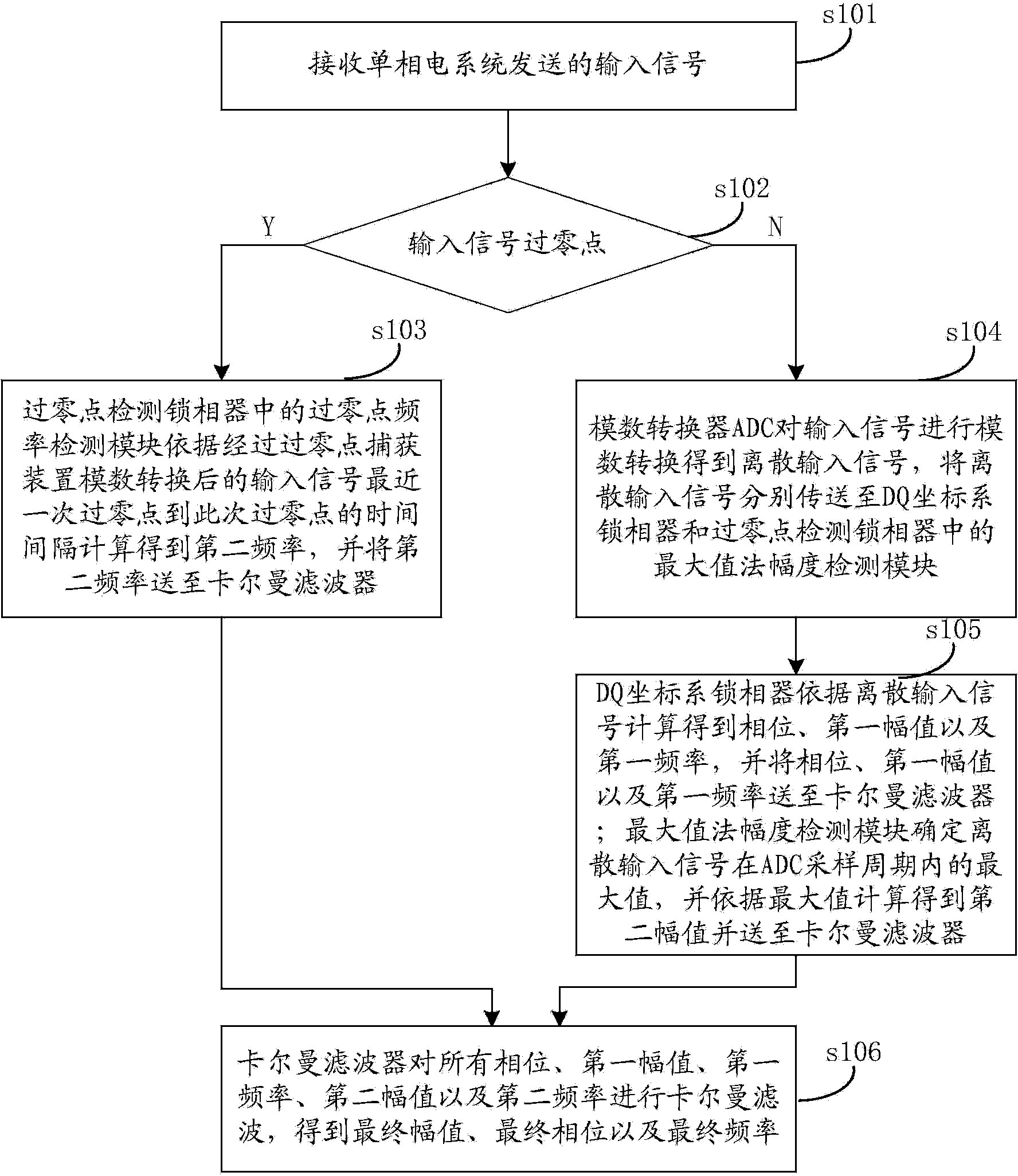

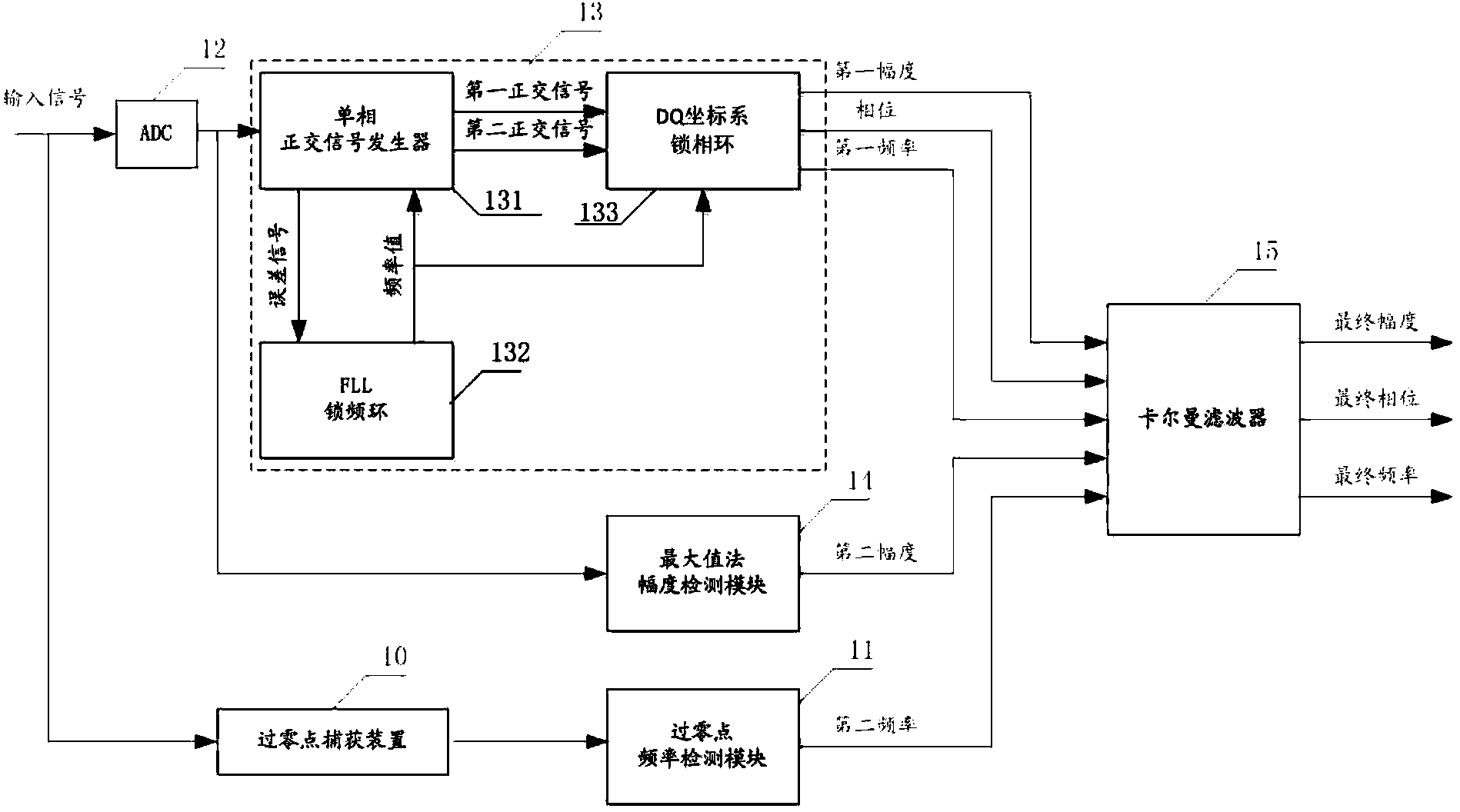

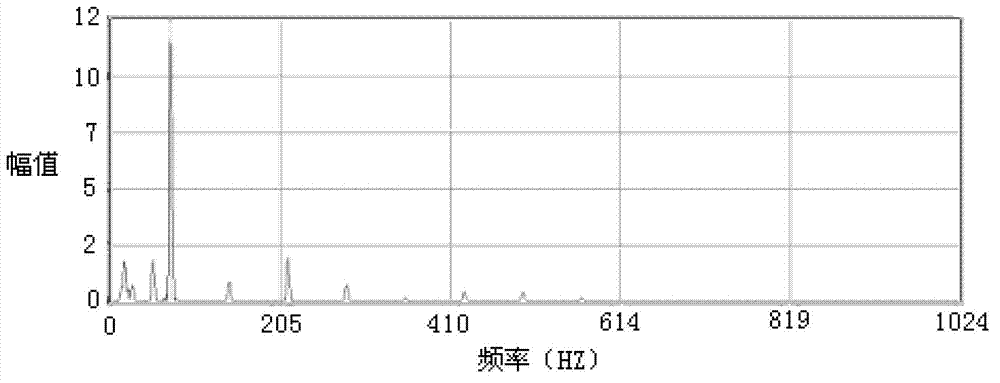

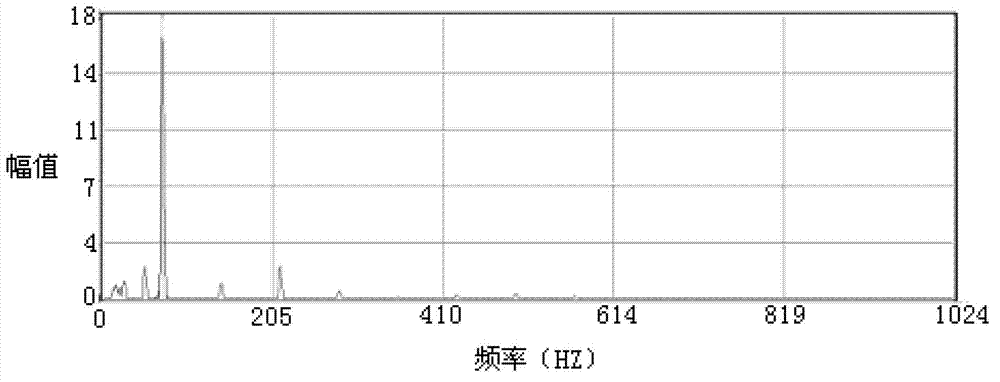

Single phase locking method and device

ActiveCN104410408AQuick lock functionAccurate phase lock functionPulse automatic controlKaiman filterFiltration

The invention discloses a single phase locking device. In the device, a Kalman filter is used for combing a zero crossing point detection phase locker and a DQ coordinate system phase locker and performing Kalman filtration on frequency values, phase positions and amplitude values sent by the zero crossing point detection phase locker and the DQ coordinate system phase locker so as to obtain a final phase position, a final amplitude and a final frequency. The invention also discloses a single phase locking device which can realize a rapid and accurate phase locking function on an input signal sent by a single-phase electrical system by utilizing the advantages that sampling errors can be greatly eliminated due to the Kalman filtration and the recursive computation is high in response speed, so that the device is far better than a traditional phase locking ring in dynamic performance and static performance, overcomes the shortcomings that a traditional single phase locking method is low in speed and easy to affect, and realizes a rapid and accurate phase locking function on the phase position, amplitude and frequency of an input signal of a single-phase power grid.

Owner:STATE GRID CORP OF CHINA +1

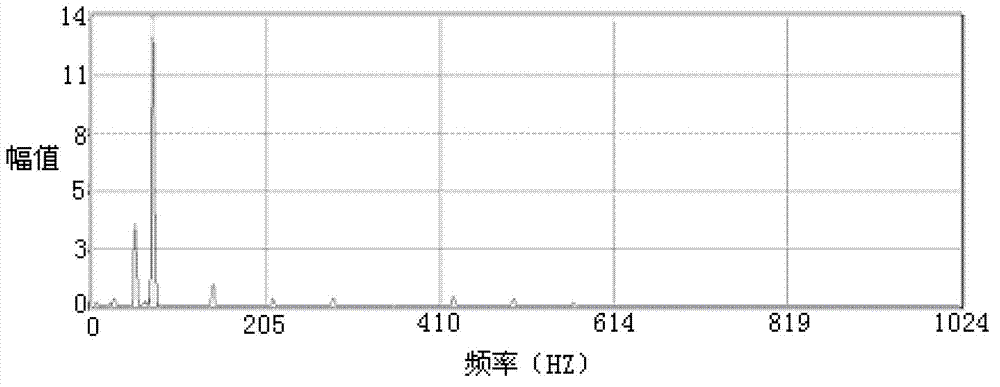

Diagnosis method for low-frequency fluid vibration excitation failure of compressor based on axial vibration analysis

ActiveCN102966526AAccurate distinctionReduce troubleshooting timePump testingPositive-displacement liquid enginesFrequency spectrumEngineering

The invention discloses a diagnosis method for a low-frequency fluid vibration excitation failure of a compressor based on axial vibration analysis. The method comprises the steps that an acquired shaft vibration signal is resolved into a direct current component and a dynamic alternating current component; then dynamic signal frequencies related to axial movement of a rotor are removed by coherence analysis; a residual frequency spectrum is continuously refined by further local frequencies; fluid impact characteristic frequency range energy in a low-frequency component is analyzed; analysis and comparison with a typical failure characteristic signal are conducted; and the low-frequency fluid vibration excitation failure can be quickly distinguished and judged. With the adoption of the method, quantification description of states of vane blades impacted by abnormal fluid is conducted with energy spectrum density of a low-frequency air flow characteristic frequency range, and the low-frequency fluid vibration excitation failure is accurately identified and quantified, tracked and monitored in real time through trend tracking analysis.

Owner:XIAN SHAANGU POWER

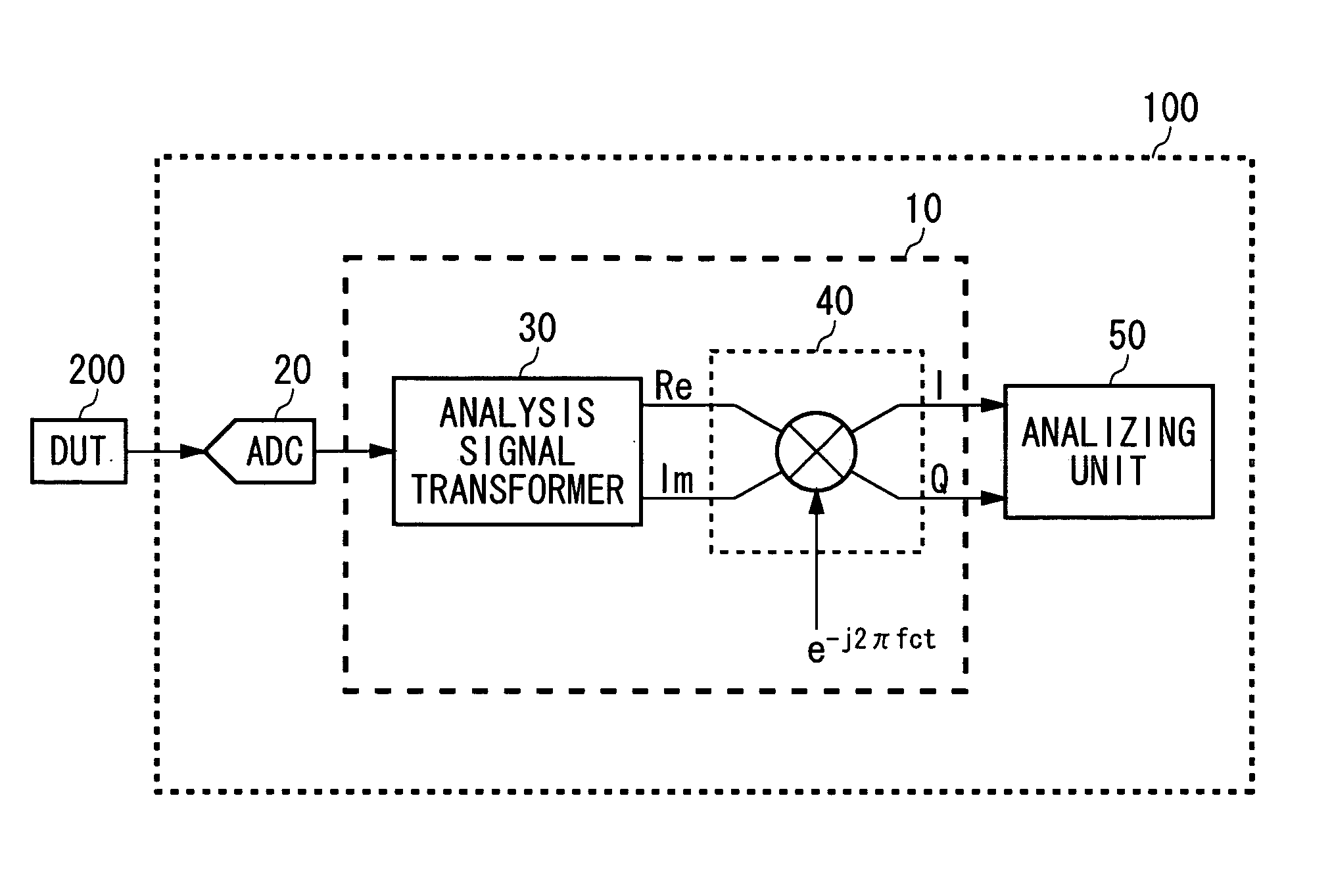

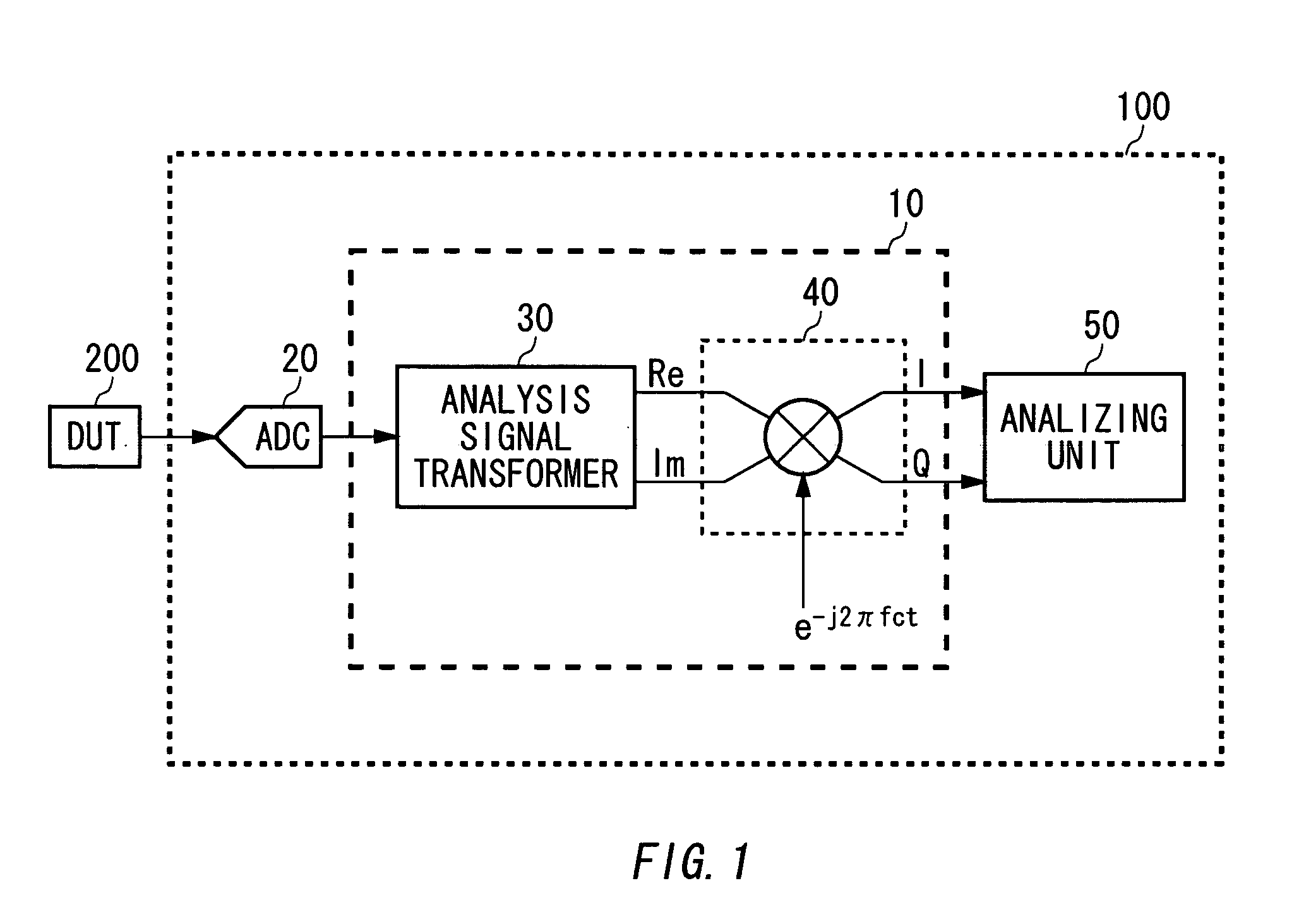

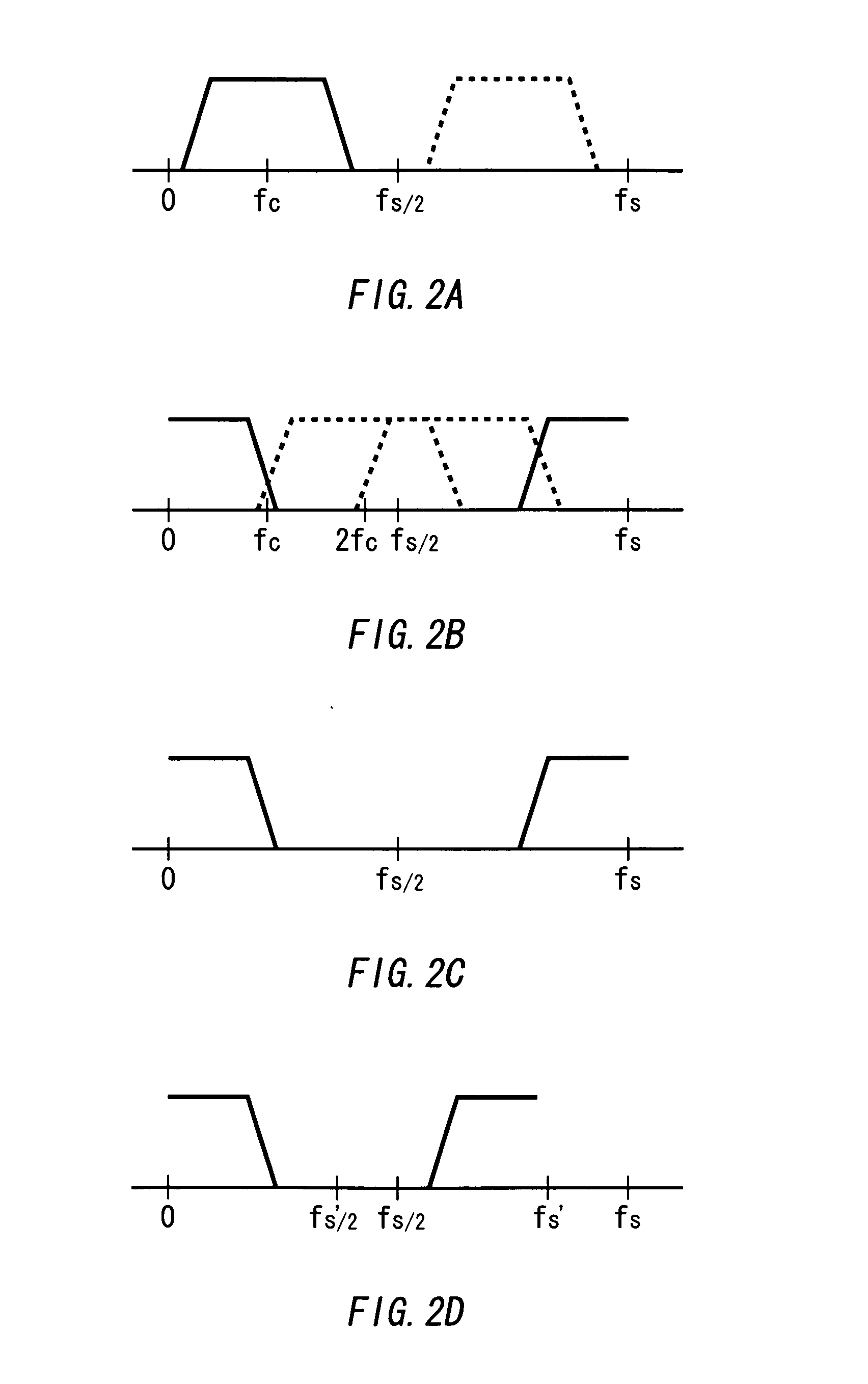

Transformer, transforming apparatus, transforming method and machine readable medium storing thereon program

InactiveUS20050141642A1Component can be removedAccurate valueModulated-carrier systemsDigital technique networkTransformerFrequency shift

A detector for detecting a signal to be measured, which is made to discrete with a predetermined discrete frequency, is provided, wherein the detector includes an analysis signal transformer for eliminating aliasing components of the signal to be measured, which are generated due to the discreteness, by transforming the signal to be measured into an analysis signal of which the discrete frequency is lower than that of the signal to be measured, and a base band signal generating unit for frequency-shifting the analysis signal and generating a complex base band signal of the signal to be measured.

Owner:ADVANTEST CORP

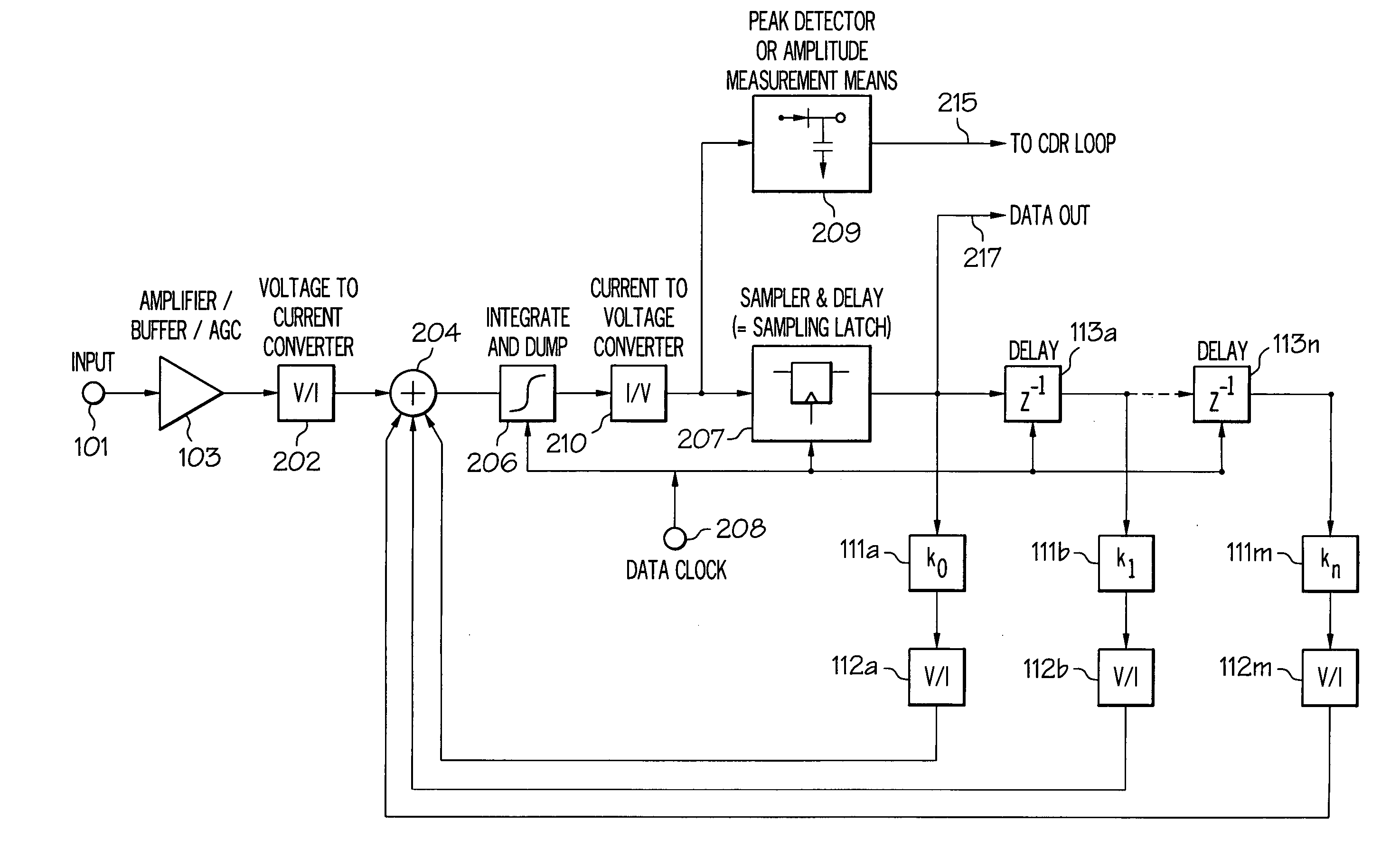

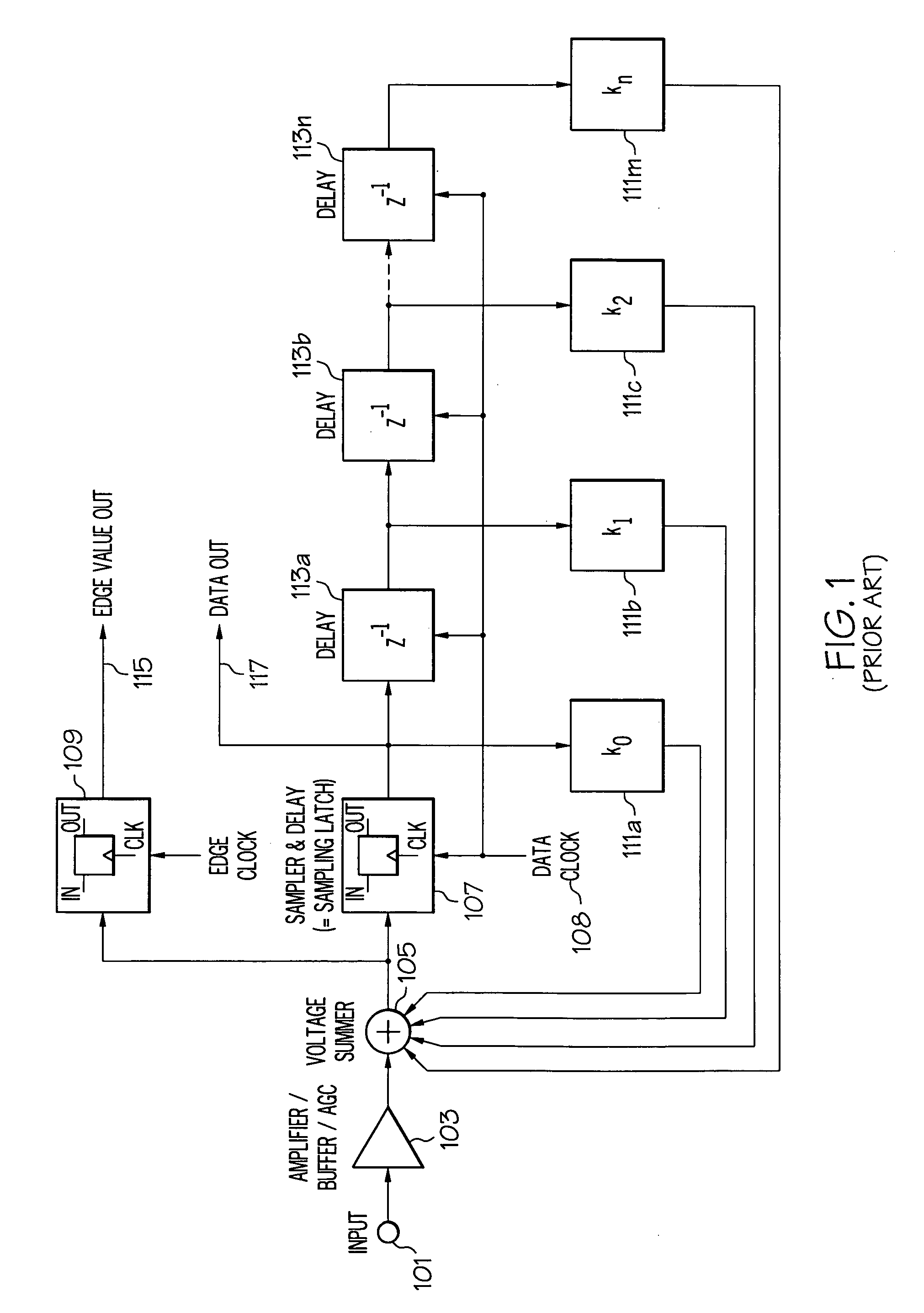

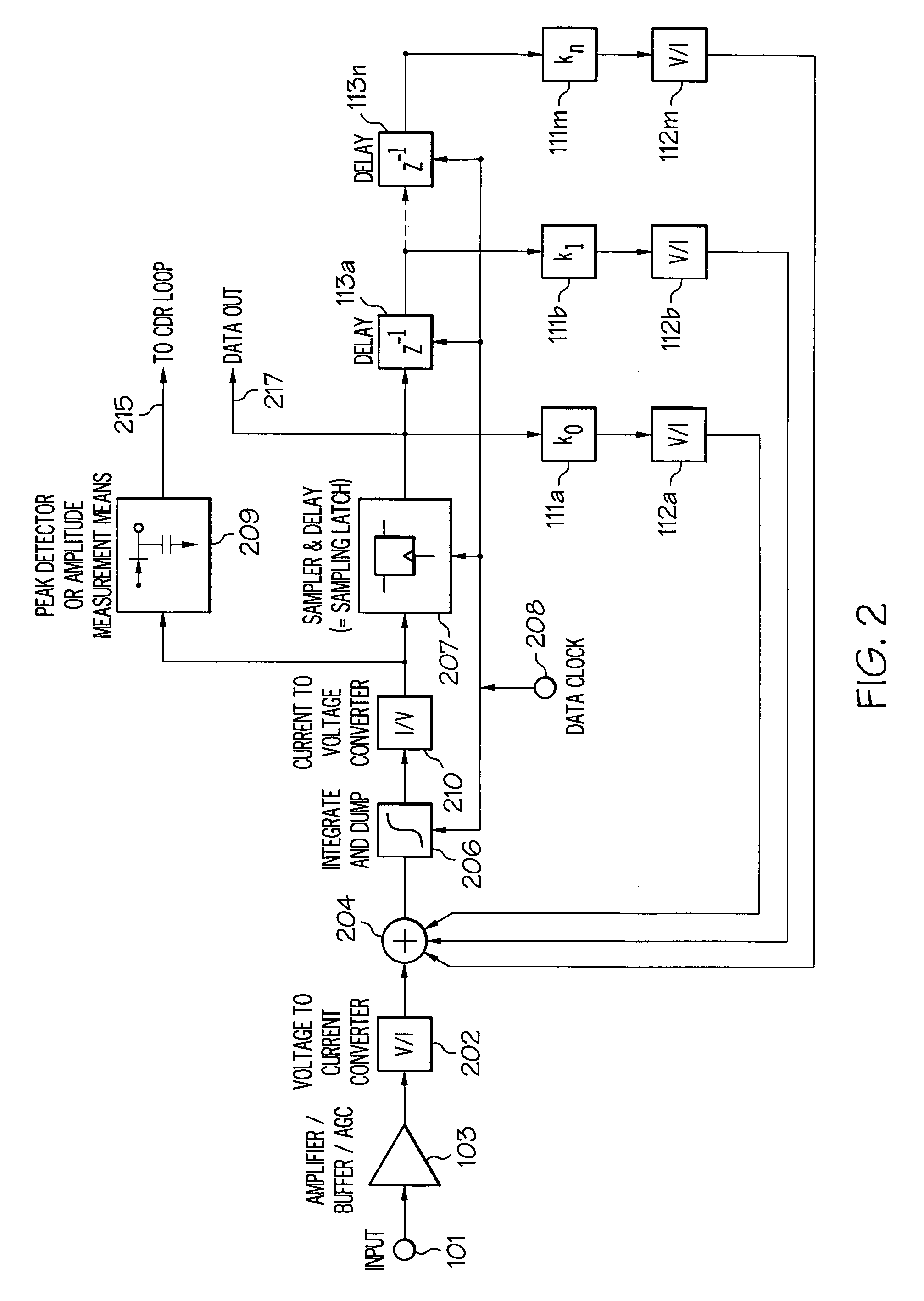

One-sample-per-bit decision feedback equalizer (DFE) clock and data recovery

InactiveUS20070242741A1Degradation of bit-error rateMaintains peak energyMultiple-port networksDelay line applicationsPhase detectorSingle sample

Disclosed are a receiver circuit, method and design architecture of a decision feedback equalizer (DFE) Clock-And-Data Recovery (CDR) architecture that utilizes / produces one sample-per-bit in the receiver and reduces bit-error-rate (BER). An integrating receiver is combined with a decision feedback equalizer along with the appropriate (CDR) loop phase detector to maintain a single sample per bit requirement. The incoming voltage is converted to a current and connected to a current summing node. Weighted currents determined by the values of previously detected bits and their respective feedback coefficients are also connected to this node. Additionally, the summed currents is integrated and converted to a voltage. A sampler is utilized to make a bit decision based on the resulting voltage. After sampling, the integrator is reset before analysis of the next bit. The necessary amplification is achieved by maximizing the sensitivity of the latch, using integration in front of the data latch.

Owner:GLOBALFOUNDRIES INC

Three-phase phase-locked loop method suitable for photovoltaic connected grid low voltage ride-through

InactiveCN103105535AEliminate the effects ofPhase accurateVoltage-current phase angleVoltage amplitudePhase difference

The invention discloses a three-phase phase-locked loop method suitable for photovoltaic connected grid low voltage ride-through, relates to the field of solar energy generating and power supplying, in particular to a three-phase phase-locked loop with the function of low voltage ride-through. The problems that affectation of zero wander is considered in existing phase-locked technology and affection on voltage detection due to measured voltage displacement is not considered in an existing detection method are solved. Firstly, voltage v of a power grid is input to a second order orthogonal signal generator and two sinusoidal signal (v' and qv') with a phase difference of 90 degrees are output. Secondly, the signal v' and the signal qv' are calculated to obtain a line voltage amplitude (VRMS) and the phase voltage amplitude (VRMS) is converted into a phase voltage amplitude VP. Thirdly, the signal v' and the signal qv' are input into the phase-locked loop and a line voltage phase angle theta 1 is locked and detected. The line voltage phase angle theta 1 is converted into a phase voltage phase angle theta p. Fourthly, based on the phase voltage amplitude VP and the phase voltage phase angle theta p, a inverter current control strategy is used for grid connecting and photovoltaic connected grid low voltage ride-through is achieved. The three-phase phase-locked loop method suitable for photovoltaic connected grid low voltage ride-through is suitable for photovoltaic power stations.

Owner:HARBIN INST OF TECH

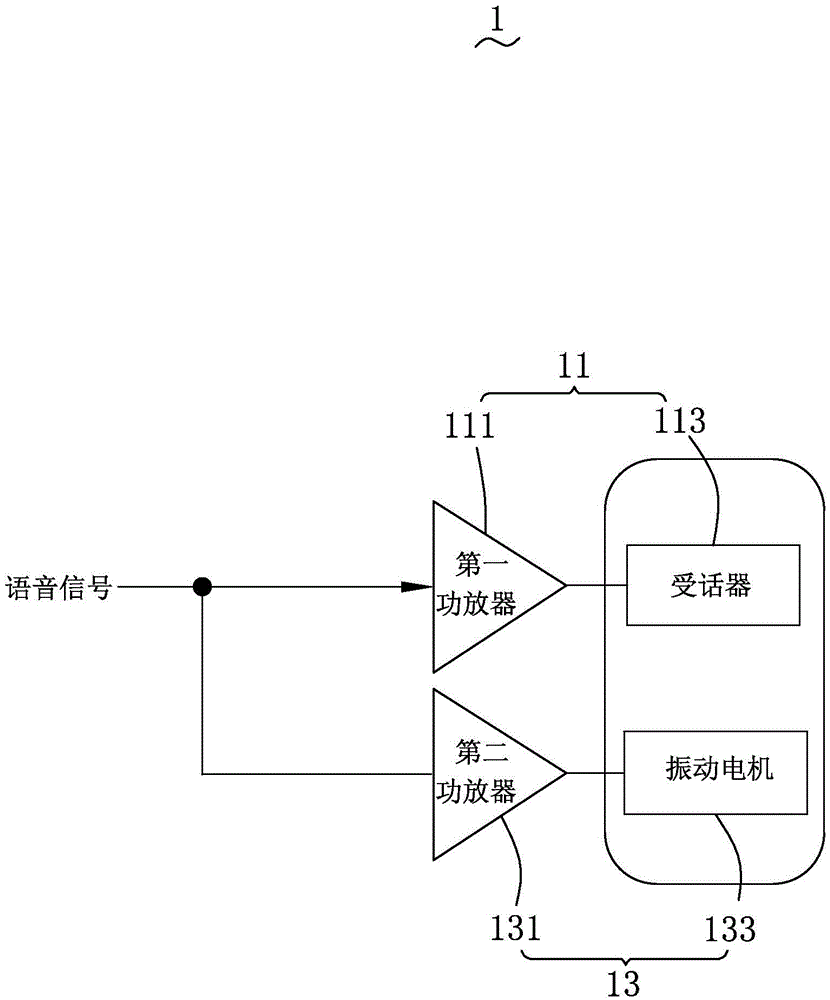

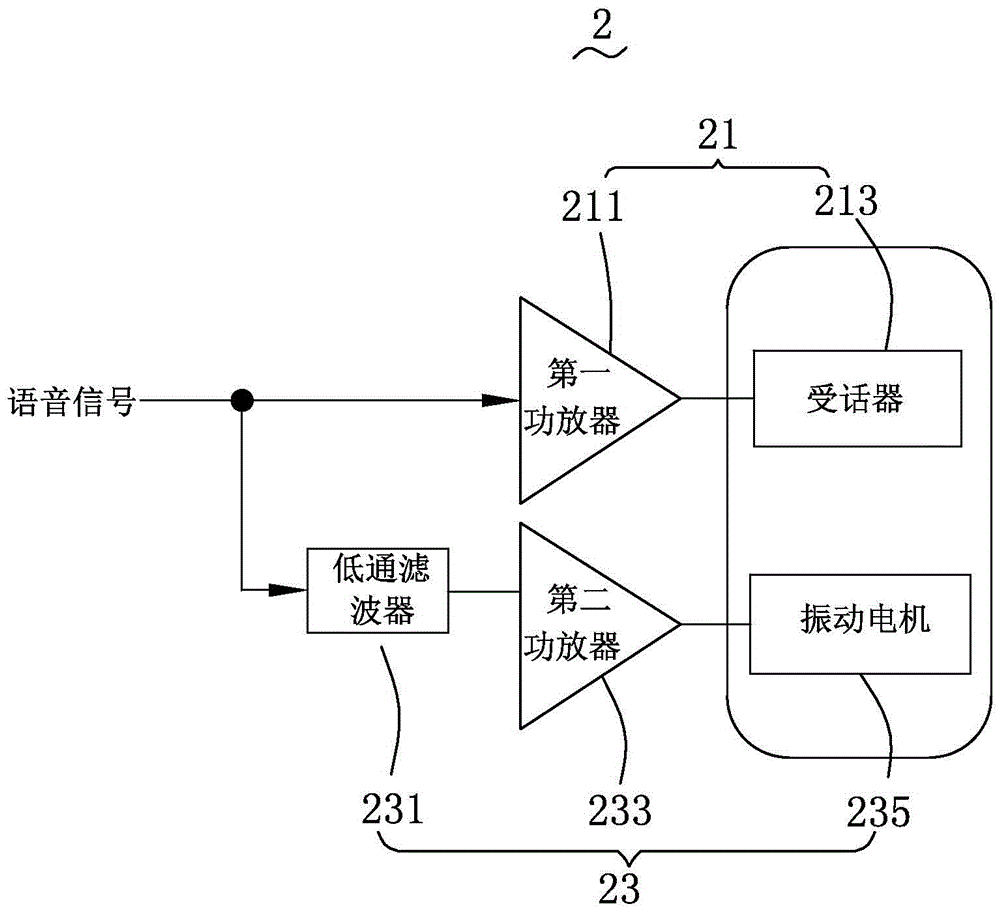

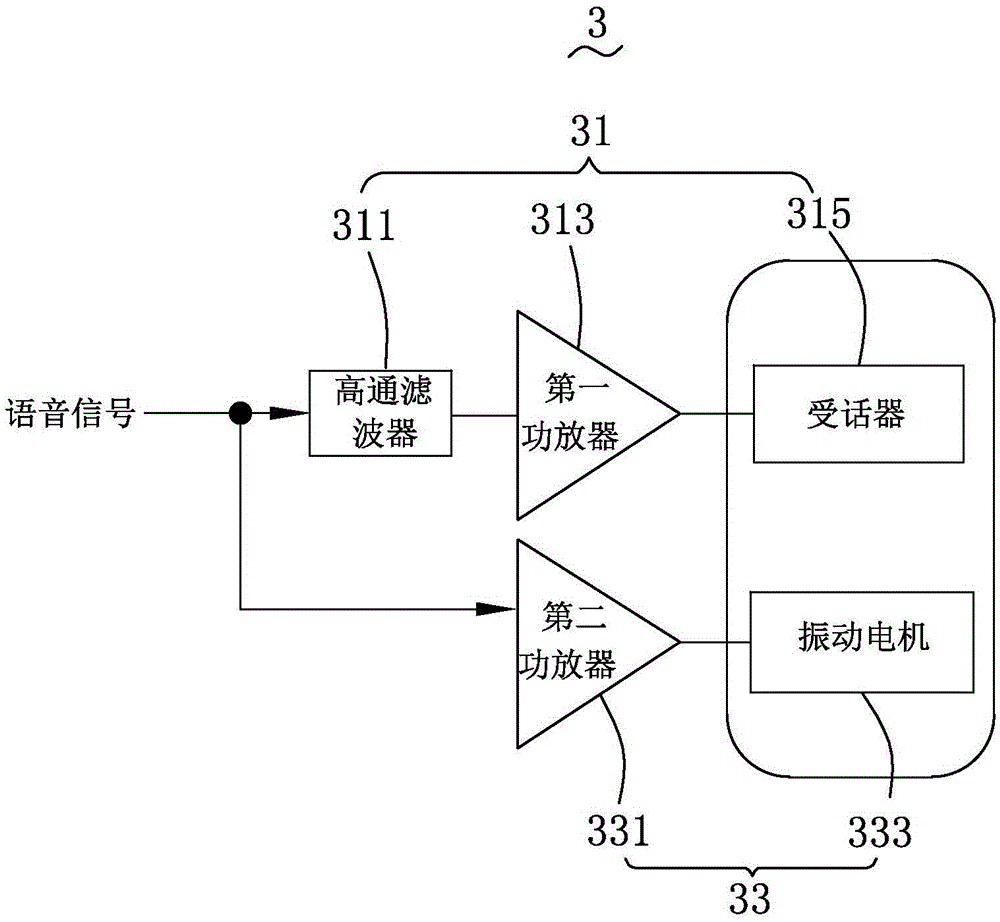

System and method for improving voice quality of mobile terminal in receiver mode

The invention provides a system and method for improving the voice quality of a mobile terminal in a receiver mode. The system for improving the voice quality of the mobile terminal in the receiver mode comprises a first signal channel and a second signal channel which are arranged in parallel; the first signal channel comprises a first power amplifier and a receiver which are electrically connected; the second signal channel comprises a second power amplifier and a vibration motor which are electrically connected; the receiver and the vibration motor simultaneously receive and play voice signals; the first power amplifier and the second power amplifier are respectively used for adjusting the gains of the voice signals output to the receiver and the vibration motor. According to the system and the method provided by the invention, when the receiver sounds, the vibration motor vibrates synchronously according to the voice signals and drives the mobile phone to vibrate and sound; the voice generated by the vibration of the vibration motor and the voice generated by the receiver are combined; the better voice quality is obtained; and the better low frequency, the better high frequency or the higher loudness is obtained.

Owner:AAC MICROTECH CHANGZHOU

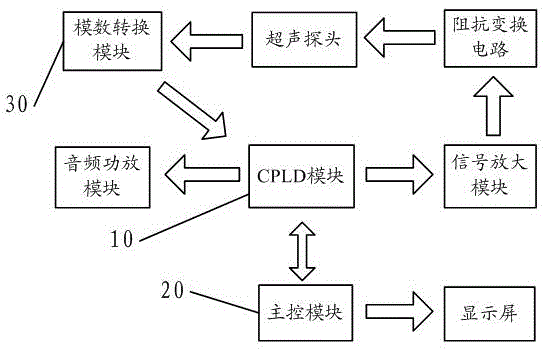

Ultrasonic-wave fetal heart monitor and digital demodulation method for echo signal of ultrasonic wave fetal heart monitor

ActiveCN105662464APhase accurateDoubling your heart rateOrgan movement/changes detectionHeart/pulse rate measurement devicesImpedance inverterDigital conversion

The invention discloses an ultrasonic-wave fetal heart monitor and a digital demodulation method for an echo signal of the ultrasonic wave fetal heart monitor. The digital demodulation method includes the steps that A, a main control module outputs a control order to control a CPLD module to output a pulse excitation signal; B, the pulse excitation signal is amplified through a signal amplification module, and is processed through an impedance inverter circuit to be transmitted to an ultrasonic probe to be excited; an ultrasonic echo is received through the ultrasonic probe and converted into the echo signal; C, the echo signal is subjected to analog-digital conversion through an analog-digital conversion module to generate the digital echo signal, the digital echo signal is transmitted to the CPLD module to be subjected to digital demodulation to generate an I signal and a Q signal, and the I signal and the Q signal is fed back to the main control module; D, the main control module receives the I signal and the Q signal to output the control order again to the CPLD module, and transmits the I signal and the Q signal to a display screen to be displayed. A more-real I / Q signal envelope and a more-real frequency-shift signal envelope can be obtained, and the problem of the double heart rate is solved; tissue movement at the specific depth can be further monitored.

Owner:SHENZHEN UNIV

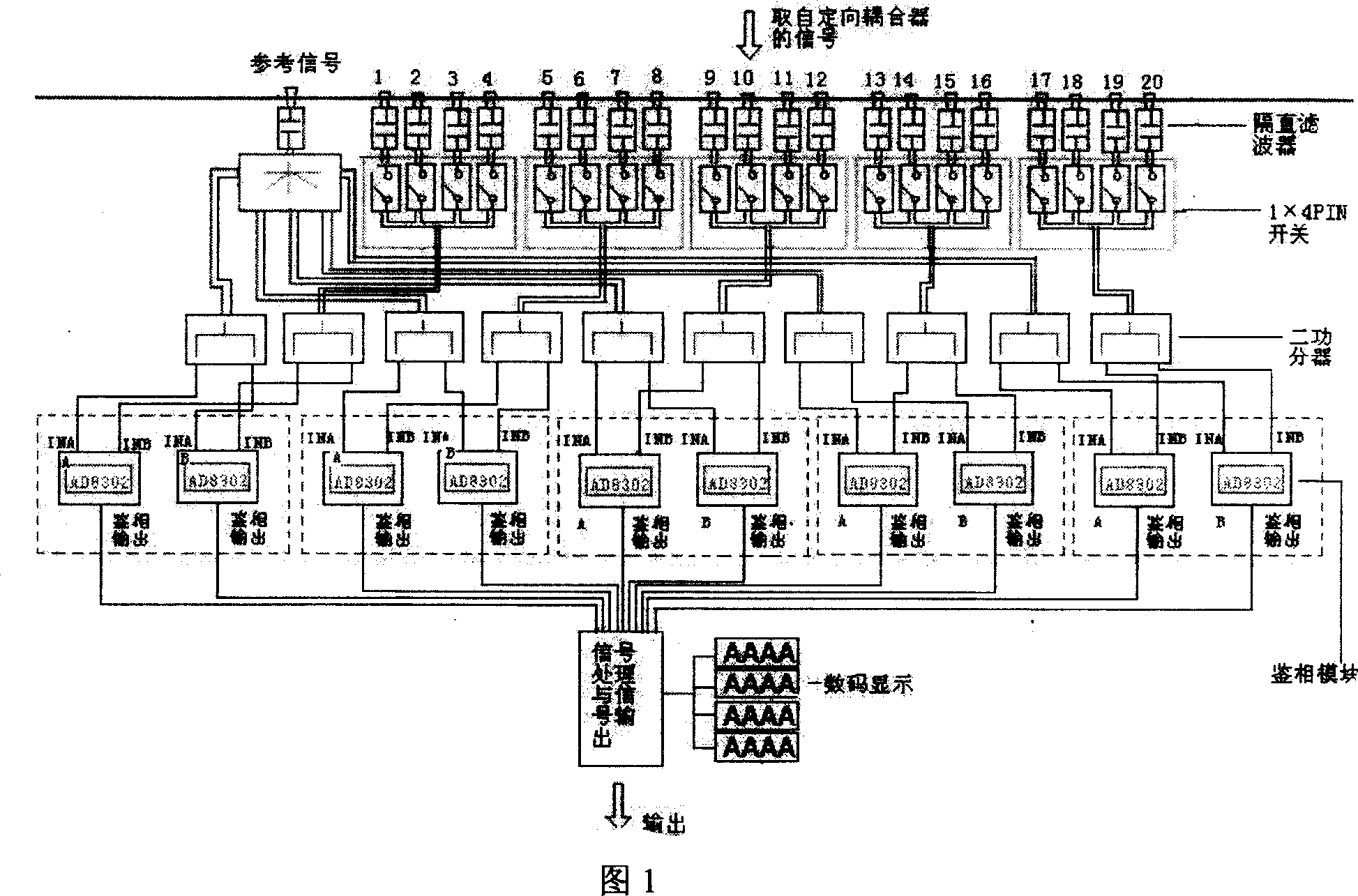

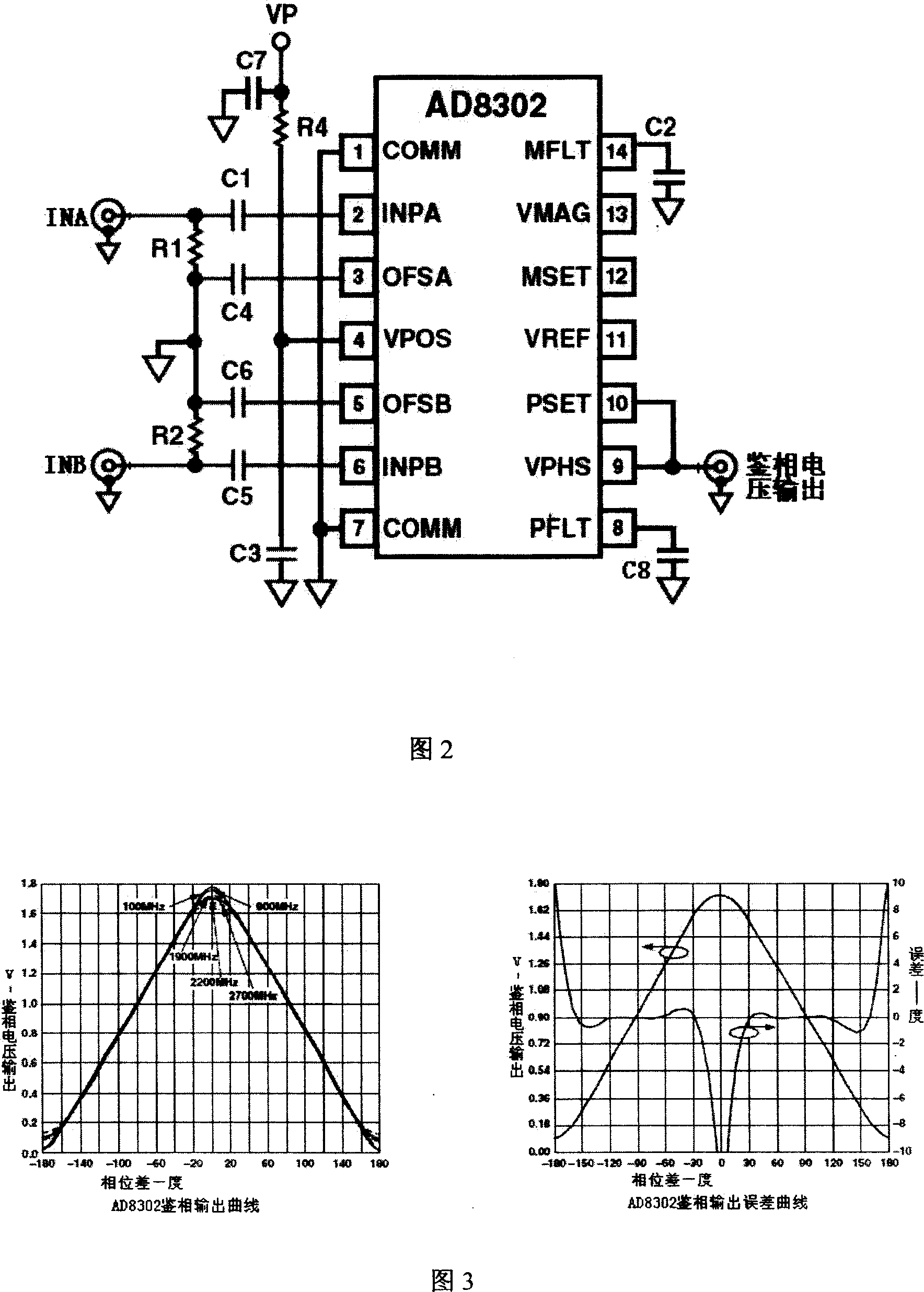

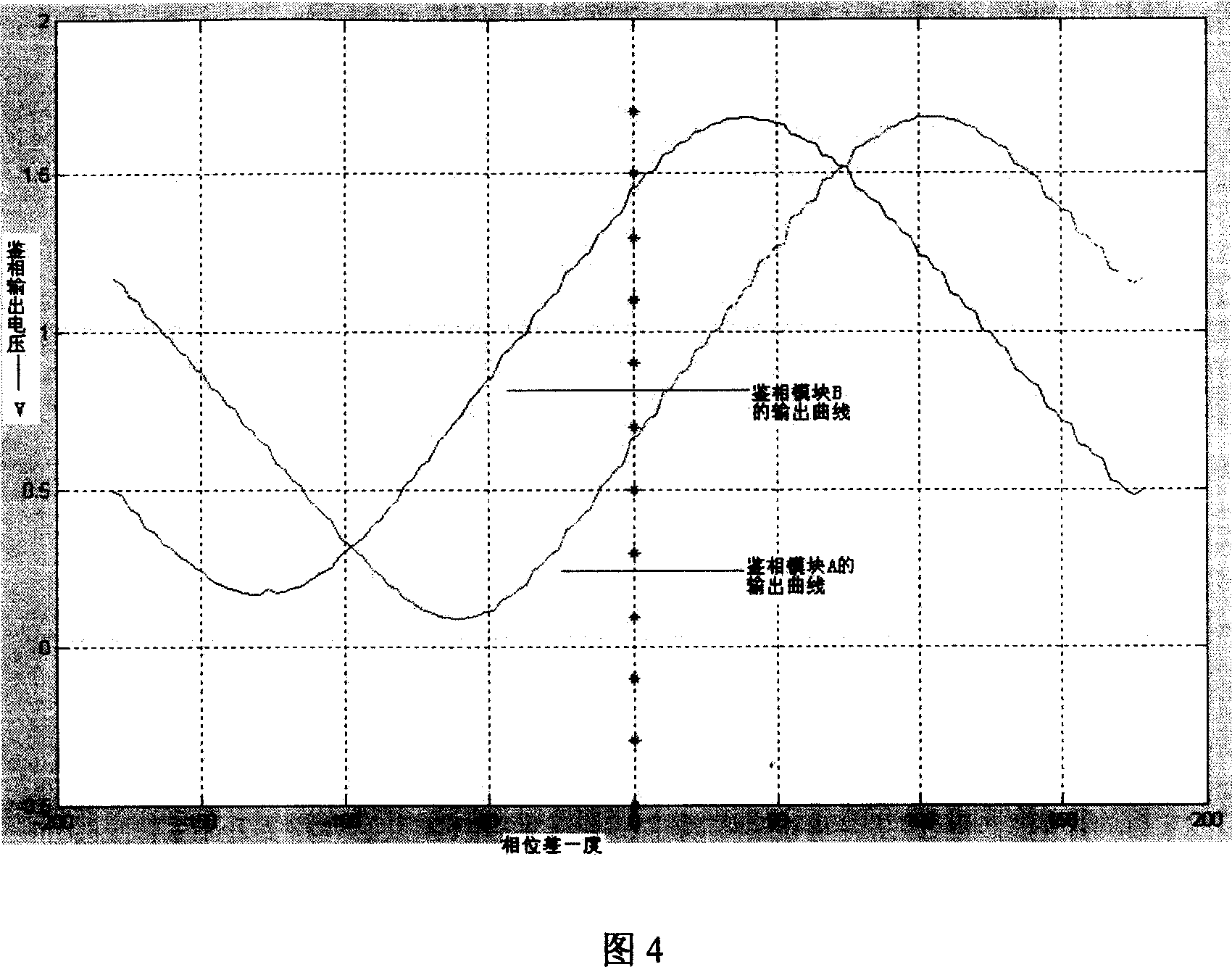

Apparatus for measuring entrance phase position of Tokamak low-noise-wave antenna array and phase-appraising method

InactiveCN1936606AAvoid losing lockAvoid the disadvantage of not being able to measure phasePulse automatic controlRadiation/particle handlingLow noiseKlystron

The invention discloses a phase-measuring device and identification method to entrance Tokamak low clutter antenna phase. That is to connect a dual directional coupler respectively at the root of every klystron output waveguide transmission line and near the antenna. Each dual directional coupler microwave signal is separated into two parts through filter and two straight power splitters respectively access Module A, B input. Phase two modules used to work, A module will phase output phase voltage curves of the same phase of the two phase corresponding phase combined output phase voltage module B identify a phase value. The invention measures and phases out amount of regulation quickly and accurately when Tokamak system sends the 2.45 GHz microwave signal to antenna phase entrance, provides accurate feedback phase of the phase control, provide a reliable technical support for studying microwave plasma coupling efficiency.

Owner:INST OF PLASMA PHYSICS CHINESE ACAD OF SCI

Image display apparatus and method of adjusting clock phase

InactiveUS20100201874A1Automatically adjusting phasePhase accuratePulse automatic controlCathode-ray tube indicatorsDigital videoClock phase

An image display apparatus includes a controller for dividing at least a portion of an image displayed based on a digital video signal, into a plurality of image areas defined by display lines, and establishing different delays for the divided image areas, a clock adjuster generating a clock in synchronism with the dot clock, delaying a phase of the clock according to the delays established by the controller, for the respective divided image areas, and outputting the delayed clock as the reproduced dot clock, and a delay evaluating unit converting differential data between adjacent signal levels into absolute values and accumulatively adding the absolute values based on the reproduced dot clock output from the clock adjuster, with respect to the display lines which define the divided image areas, thereby producing accumulated sums. The controller judges the delay established for the divided area with the maximum accumulated sum, as optimum.

Owner:NEC DISPLAY SOLUTIONS LTD

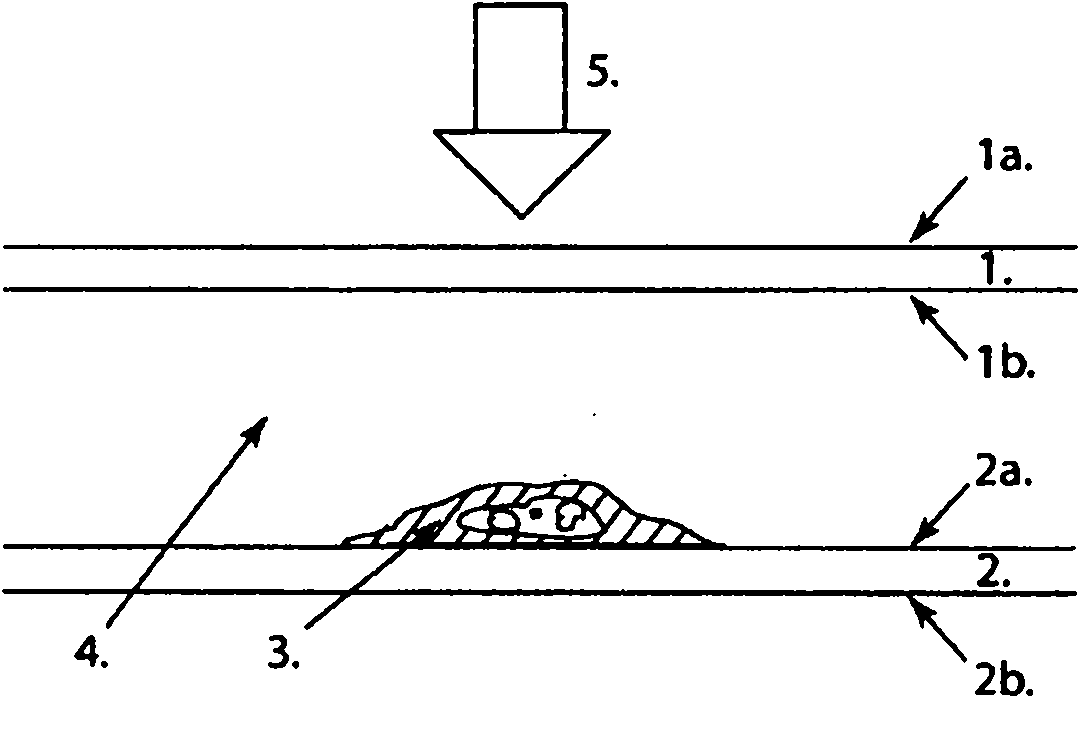

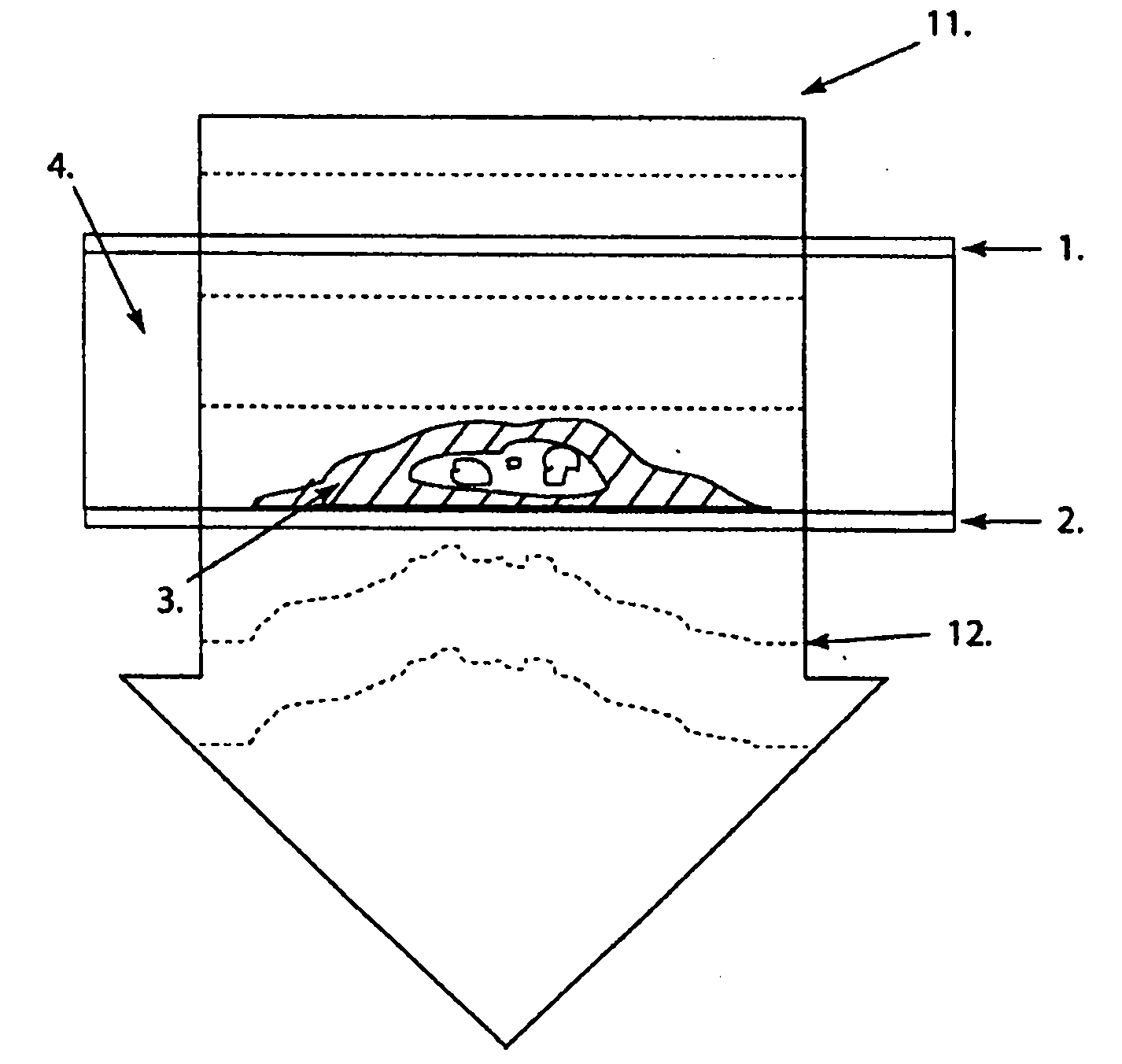

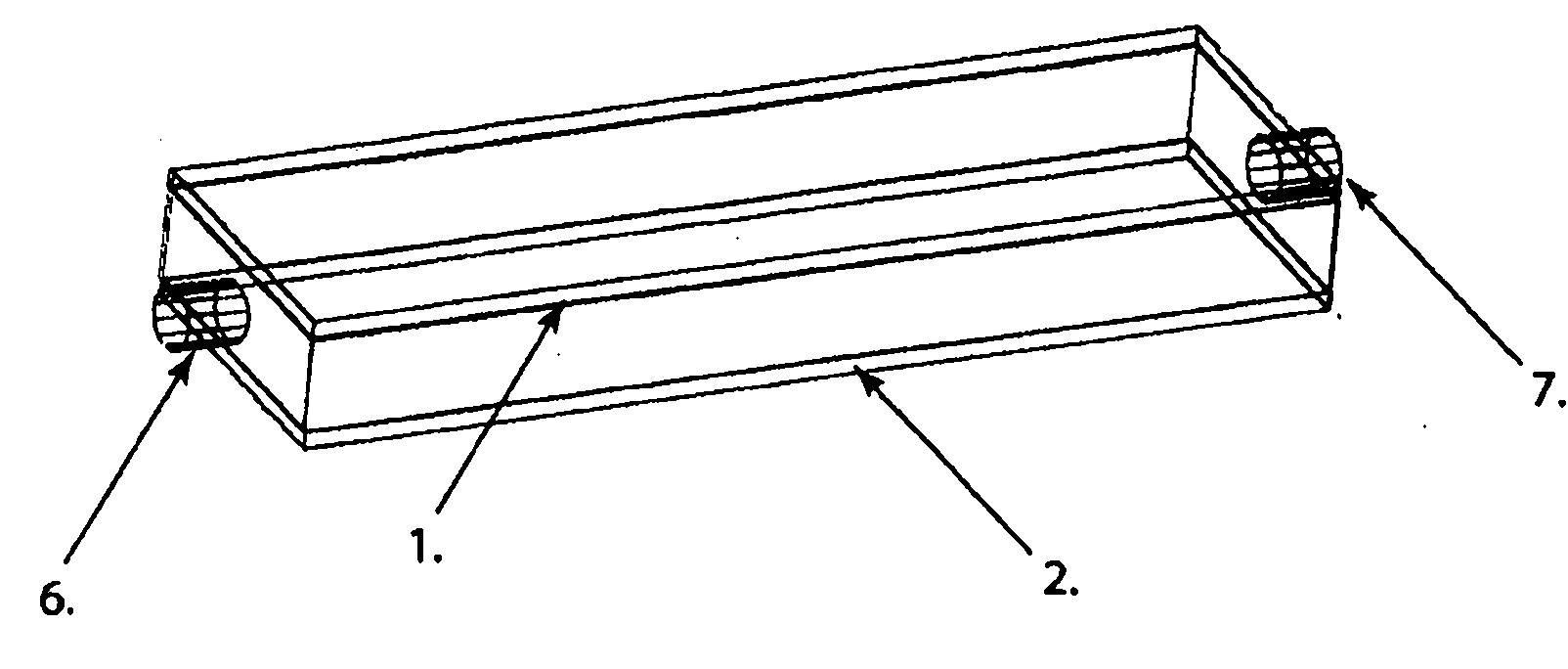

Analysis of transparent biological objects

InactiveCN102067046APhase accurateReduce accidental disturbance rateWork measurementLaboratory glasswaresDigital holographic microscopyBiological objects

The present invention relates to an observation vessel for digital holo-graphic microscopy of at least one transparent biological object, an observation vessel lid for digital holographic microscopy of at least one transparent biological object as well as a method for analyzing a sample comprising at least one transparent biological object and at least one medium by means of digital holographic microscopy.

Owner:PHASE HOLOGRAPHIC IMAGING PHI

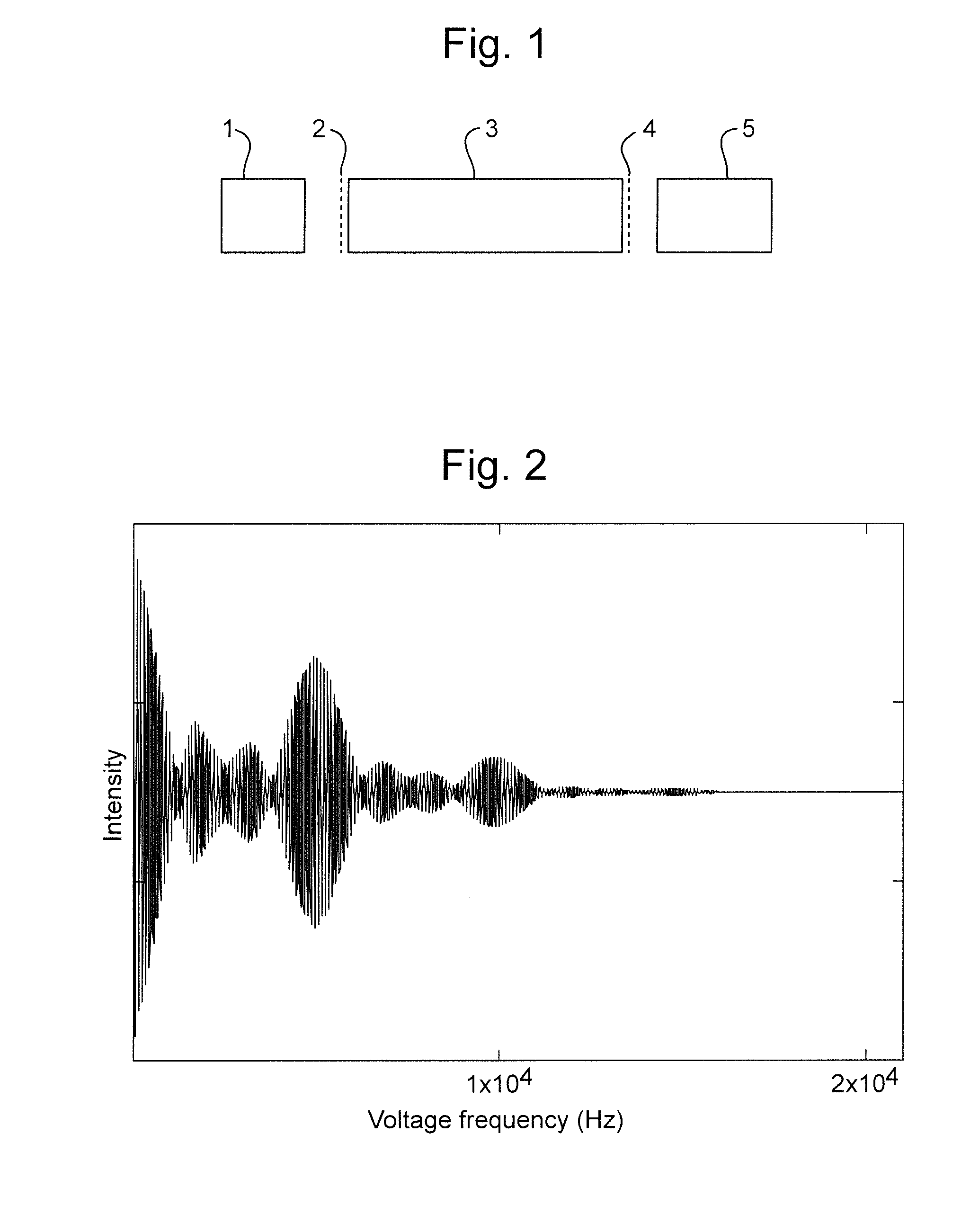

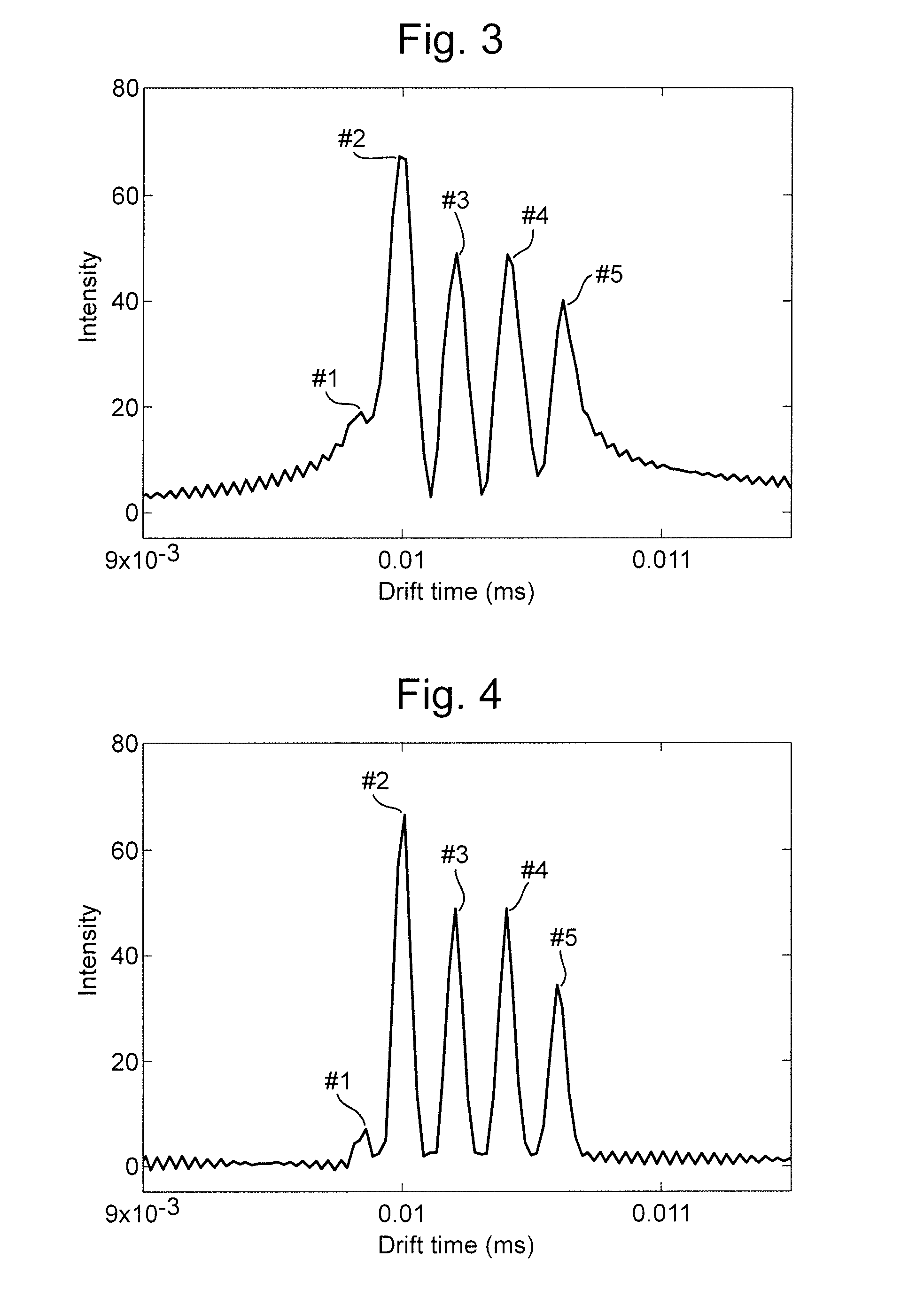

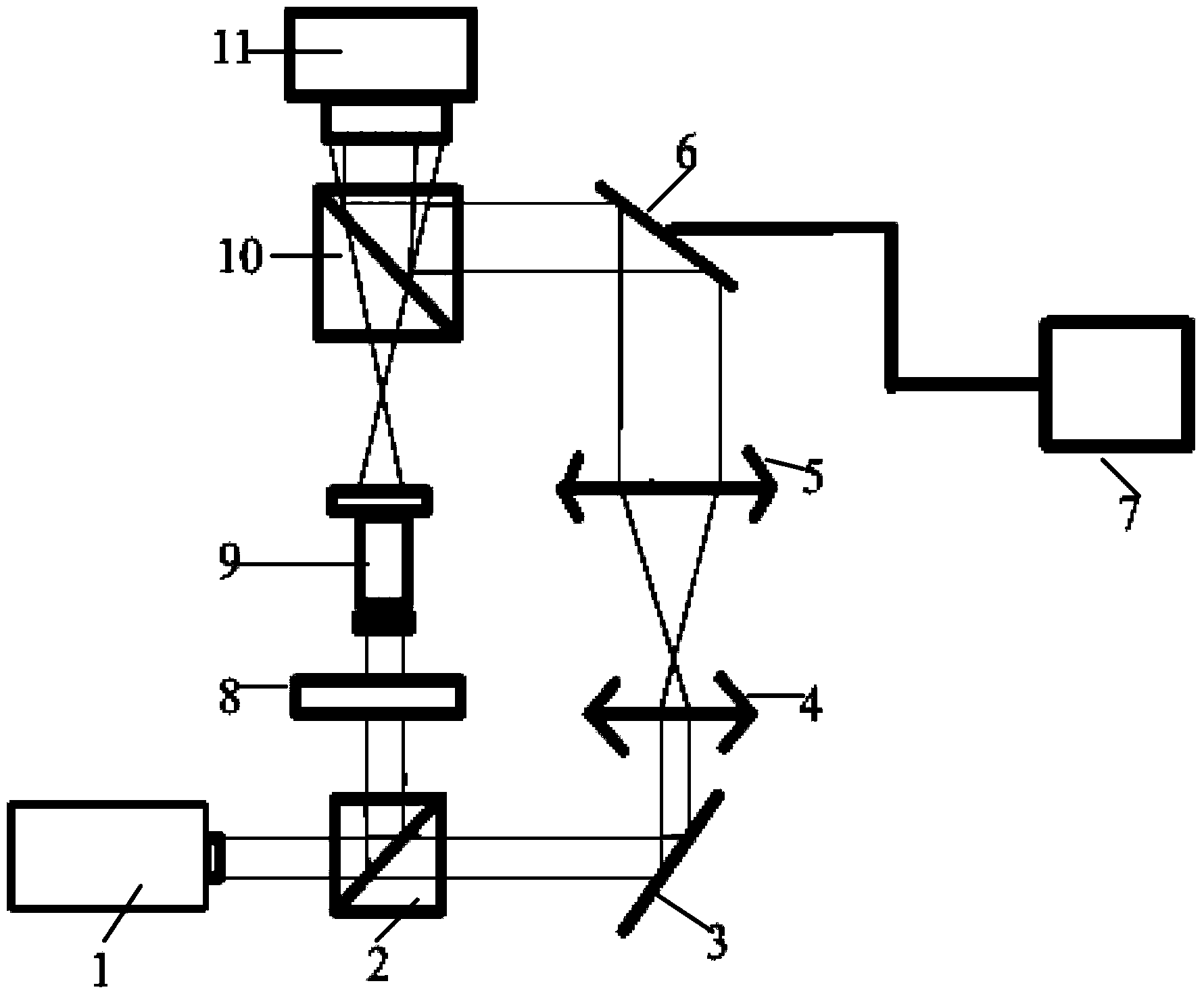

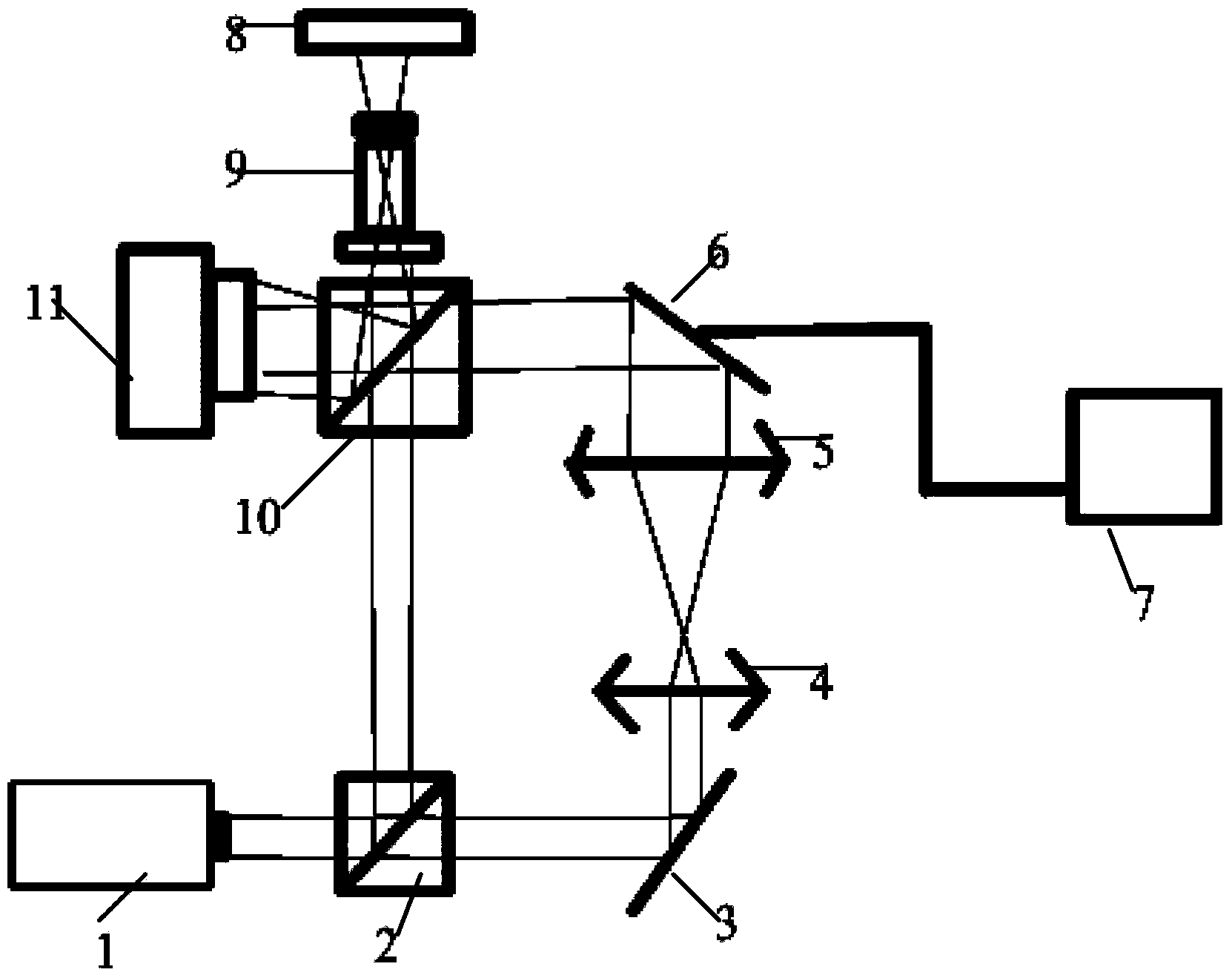

Absorption Mode FT-IMS

ActiveUS20160284530A1Improve resolutionHigh resolutionTime-of-flight spectrometersMaterial analysis by electric/magnetic meansFourier transformIon-mobility spectrometry

Owner:MICROMASS UK LTD

Phase-shifting image digital holographic microscope system and microscopy method thereof

InactiveCN103411690AReduce operational precision requirementsNo need to adjust rebuild parametersOptical measurementsMicroscopesDigital holographic microscopyLight beam

The invention discloses a phase-shifting image digital holographic microscope system and a microscopy method thereof. The microscope system comprises a laser device, a beam dividing unit, a lighting beam transmission unit, a reference beam transmission unit, a beam combining nit and an imaging unit. The reference beam transmission unit comprises a phase-shifting device used for leading in phase shifts in reference beams. According to the phase-shifting image digital holographic microscope system and the microscopy method thereof, a phase-shifting image microscopy holographic technique is adopted, a holographic picture of an image plane is directly recorded, and phase compensation can be carried out through software to obtain precise phase information of an object.

Owner:SUZHOU UNIV

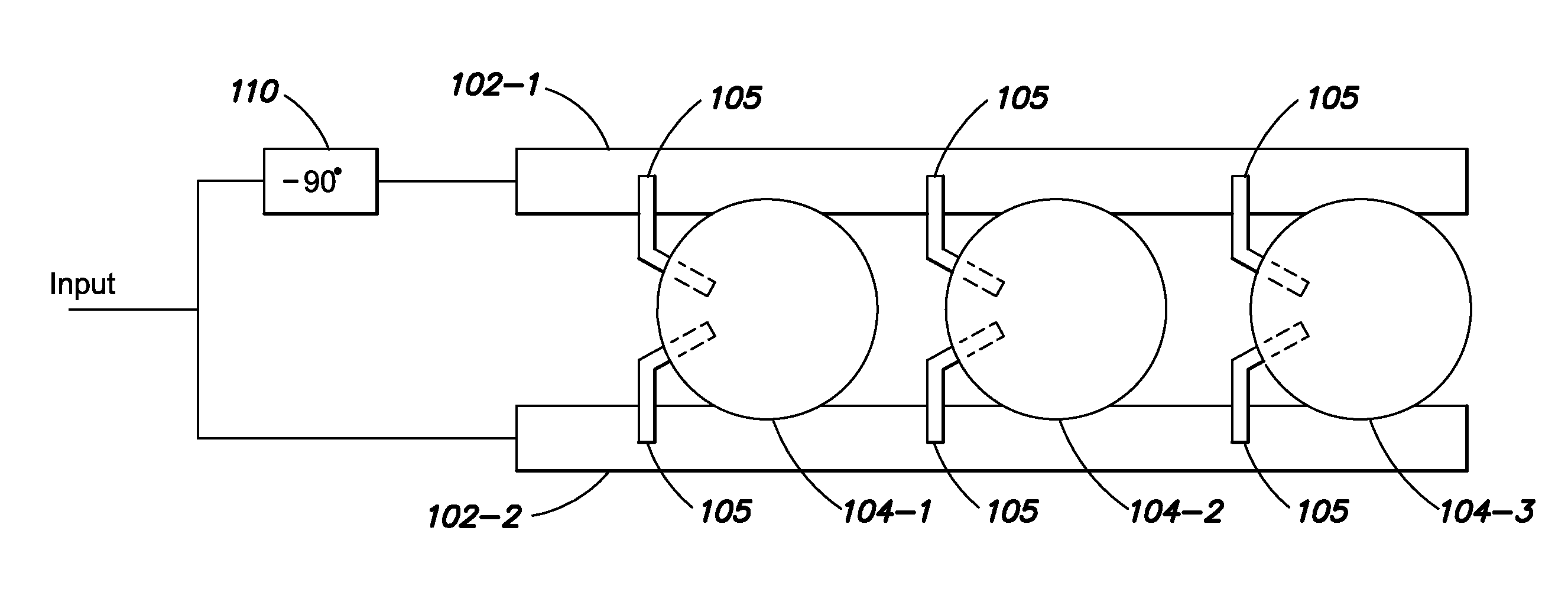

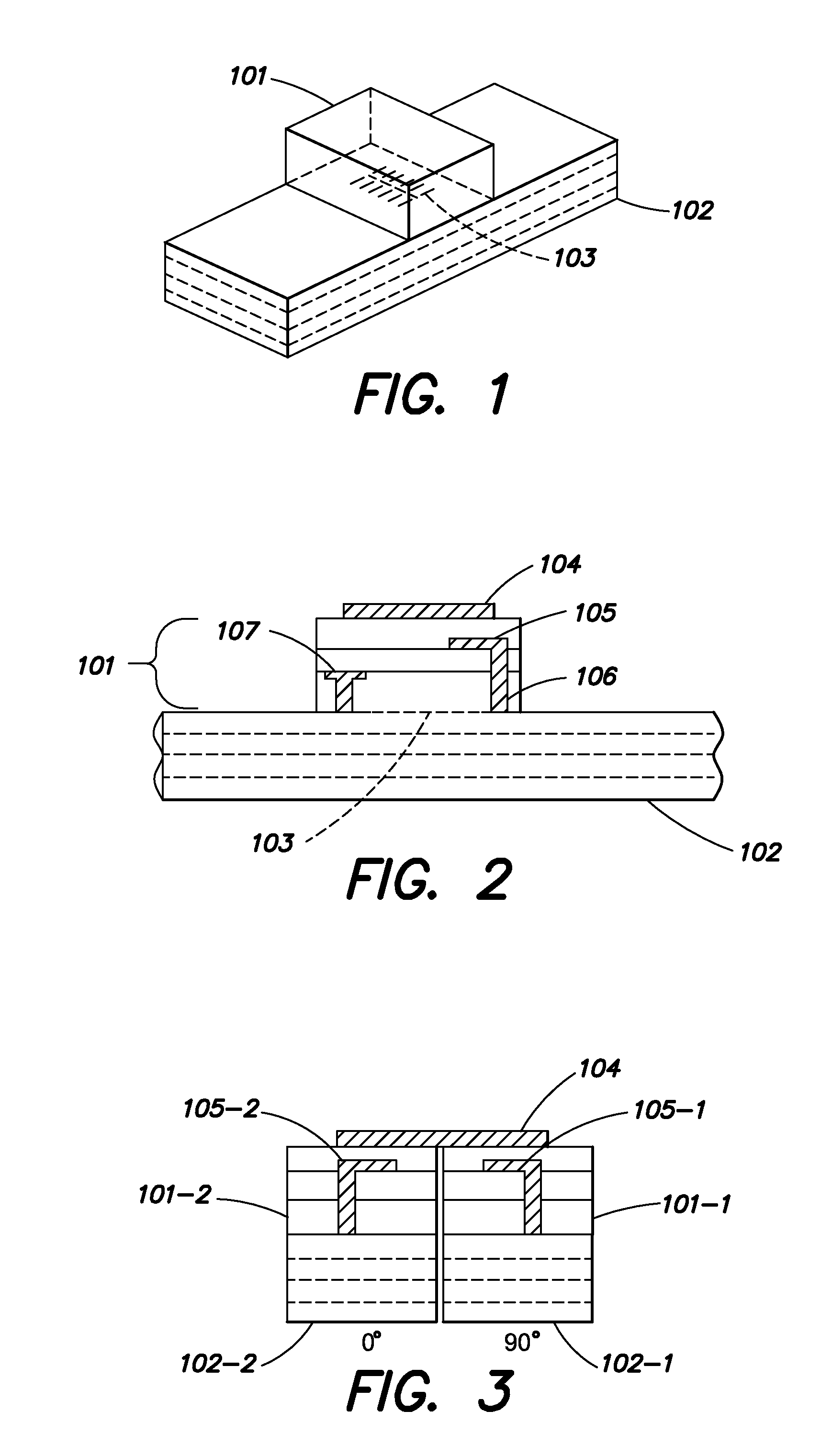

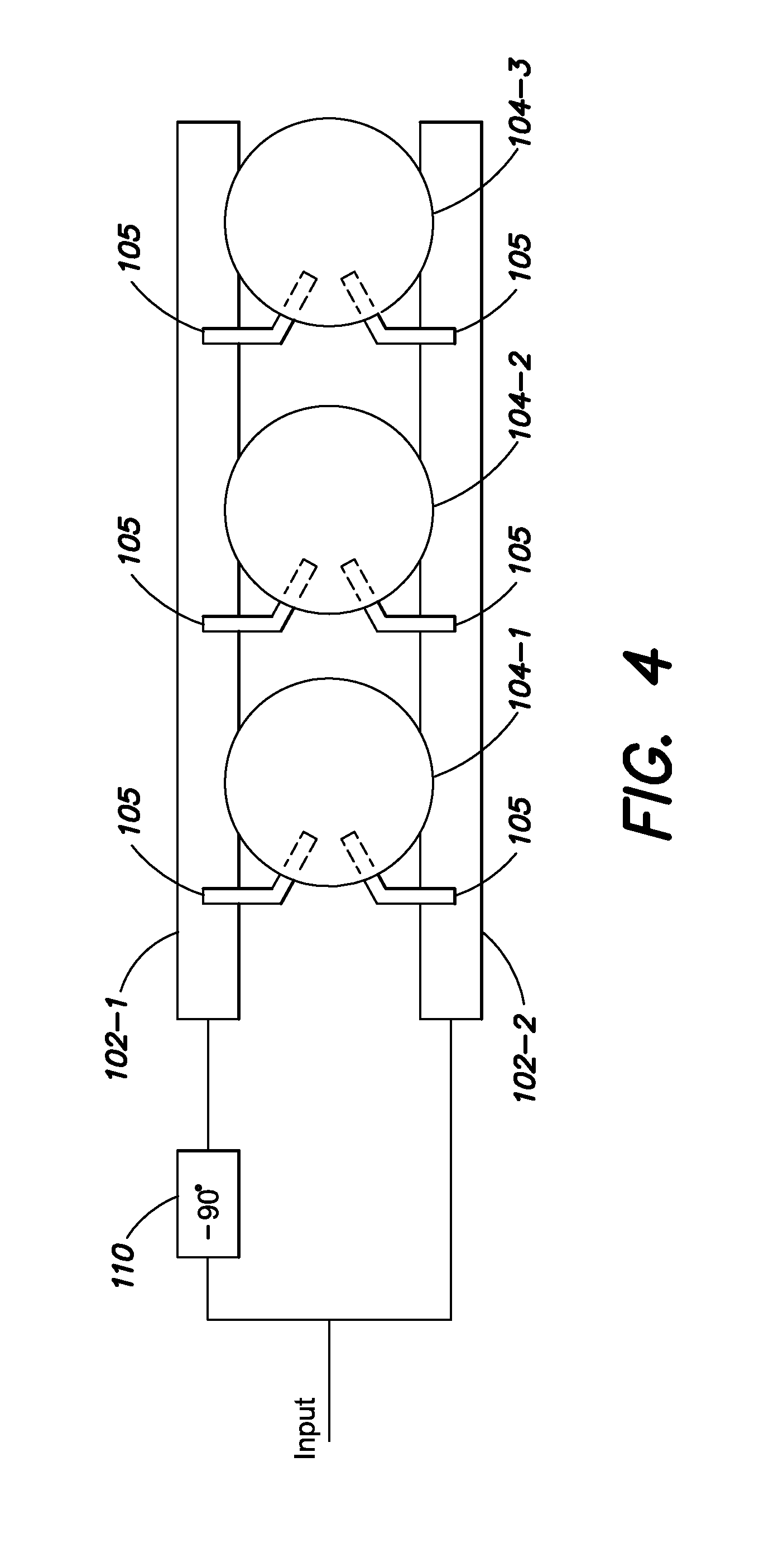

Travelling wave antenna feed structures

InactiveUS9166301B2Phase accurateLower ratioNon-resonant long antennasIndividually energised antenna arraysTraveling-wave antennaRadiating element

Techniques for implementing series-fed antenna arrays with a variable dielectric waveguide. In one implementation, coupling elements with optional controlled phase shifters are placed adjacent each radiating element of the array. To avoid frequency sensitivity of the resulting array, one or more waveguides have a variable propagation constant. The variable waveguide may use certain materials exhibiting this phenomenon, or may have configurable gaps between layers. Plated-through holes and pins can control the gaps; and / or a 2-D circular or a rectangular travelling wave array of scattering elements can be used as well.

Owner:ANTENUM INC

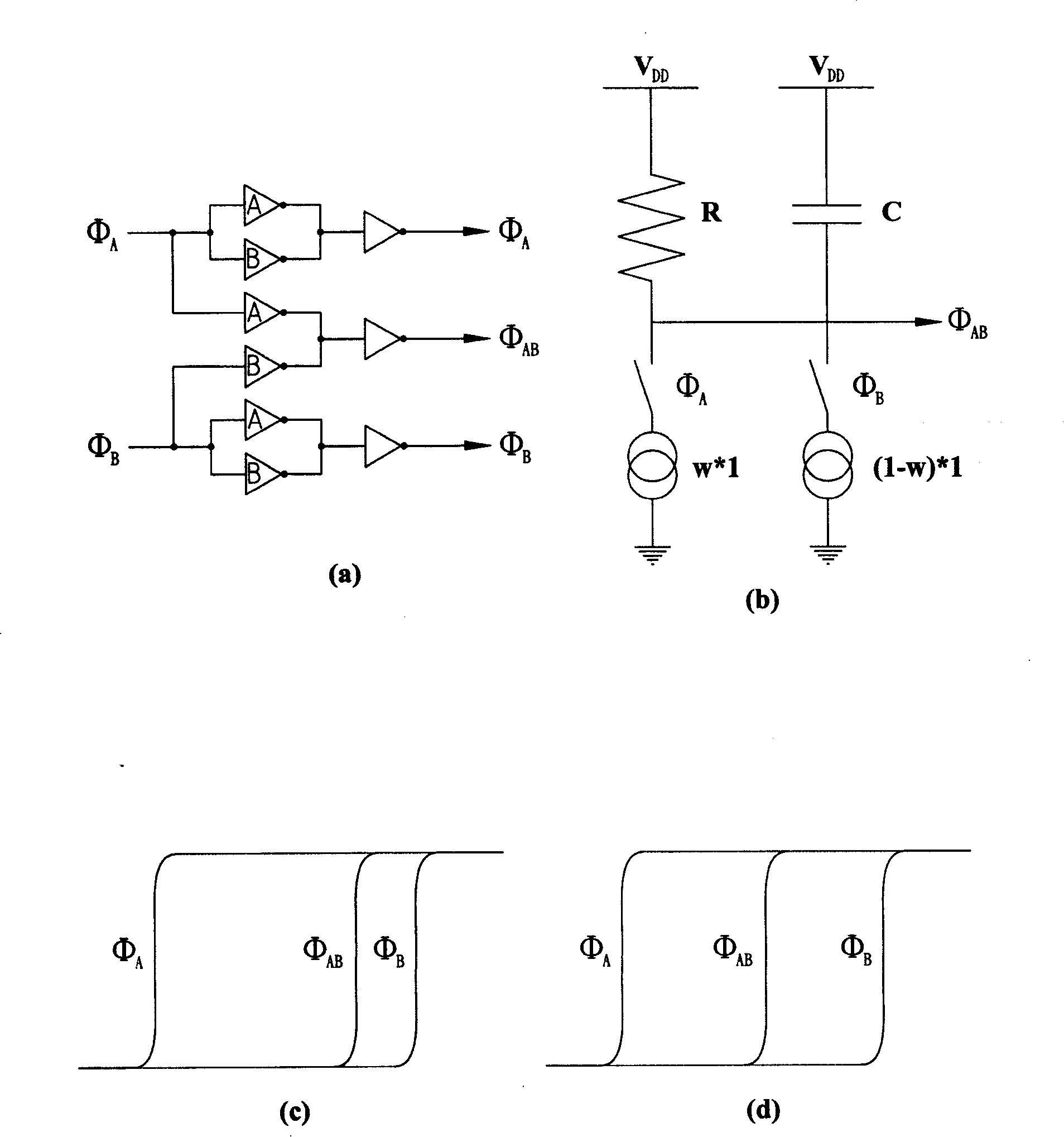

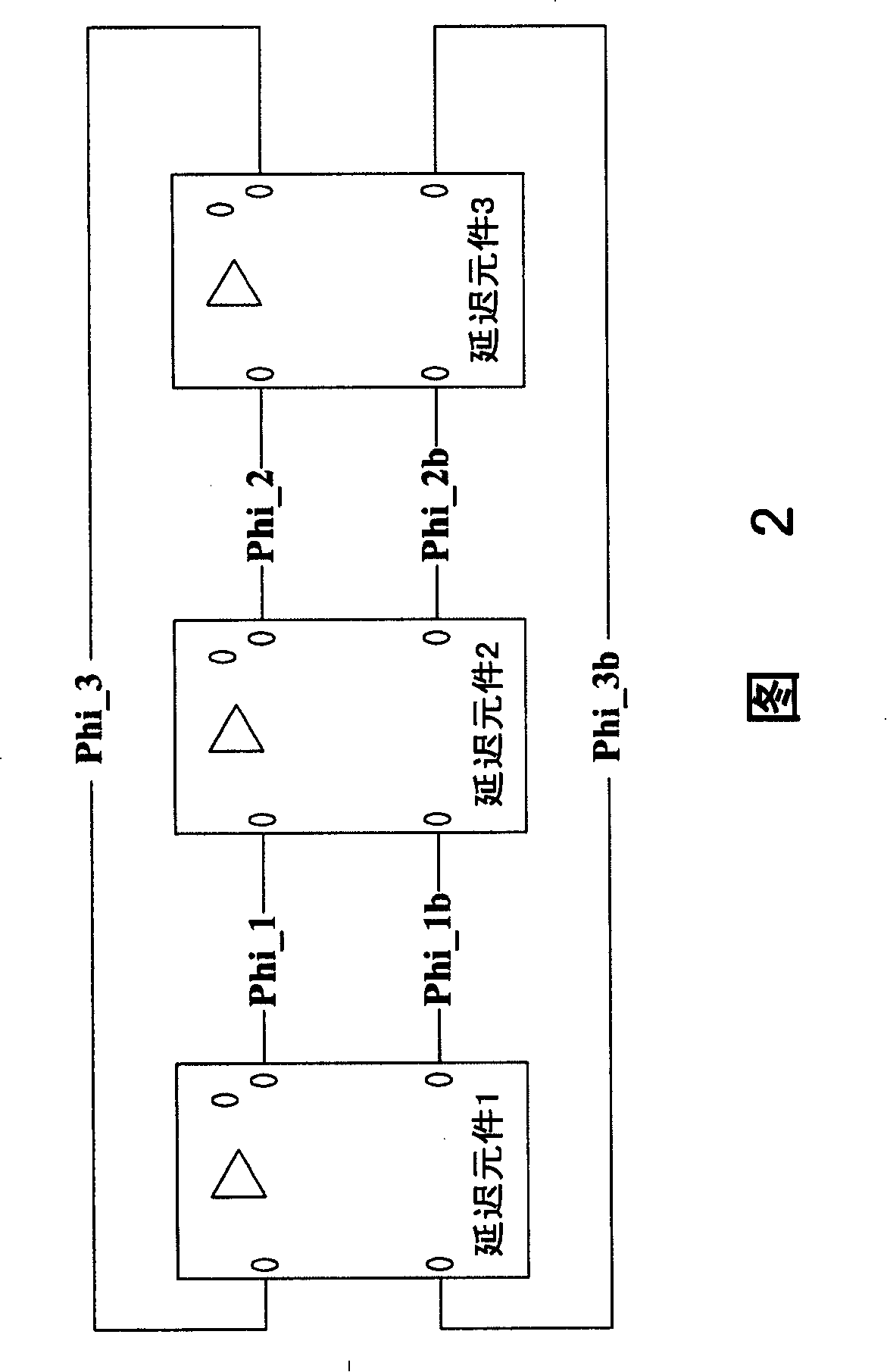

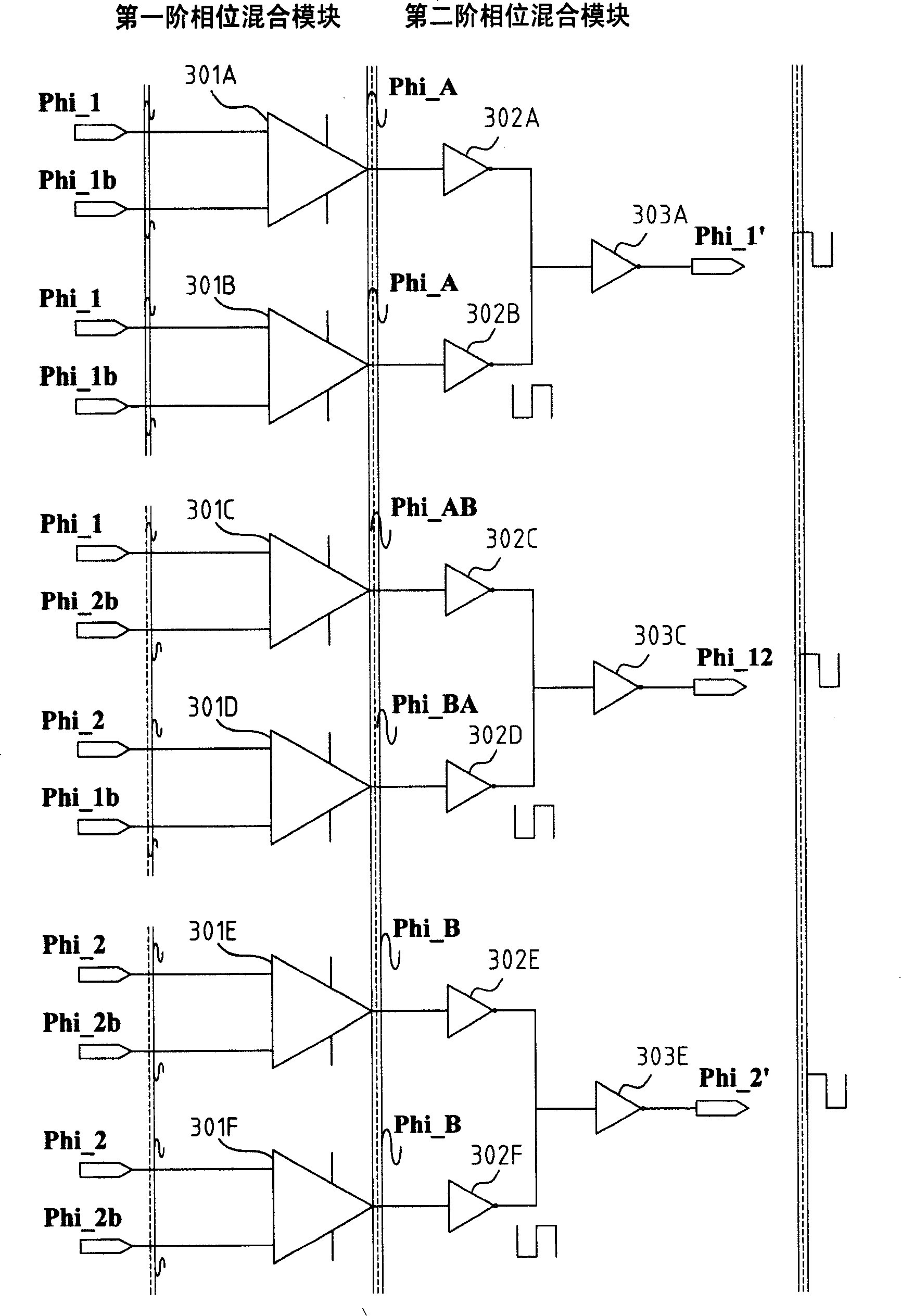

Device and method for generating multi-phase clock pulse signal based on ring oscillator

InactiveCN101242169AAvoid instabilityPhase accuratePulse automatic controlPulse generation by logic circuitsPhase mixingEngineering

A device for generating multi-phase clock pulse signal by a ring oscillator and a method thereof are provided. The device comprises: a first level phase mixing module comprising a plurality of differential operation amplifier phase mixing circuits, each of which receives two input signals and one output signal, wherein: the phase of the output signal is interpolated between the two input signals; a second level phase mixing module comprising a plurality of inverter phase mixing circuits, each of which receives two signals output by the fist phase mixing module as the input signal and outputs a clock pulse signal, wherein: the phase thereof is interpolated between two signals output by the first level phase mixing module. The method of the invention comprises the following steps of: using a ring oscillator to supply at least two non-complete vibrating signals; using the differential operation amplifier phase mixing circuit to mix the phase of the two non-complete vibrating signals generated by the ring oscillator; and using the inverter phase mixing circuit to generate the multi-phase pulse signal with interpolation phase.

Owner:MOAI ELECTRONICS

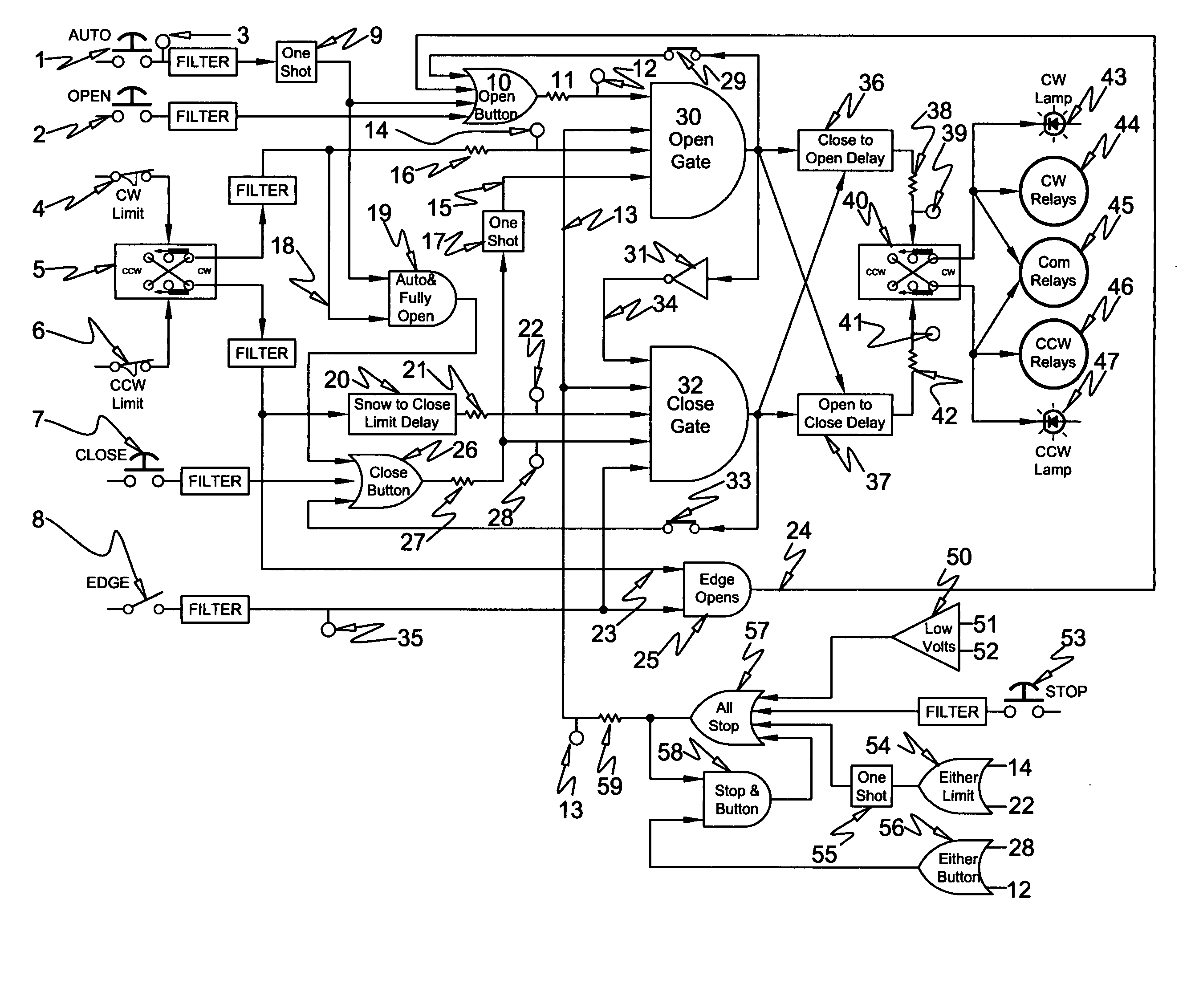

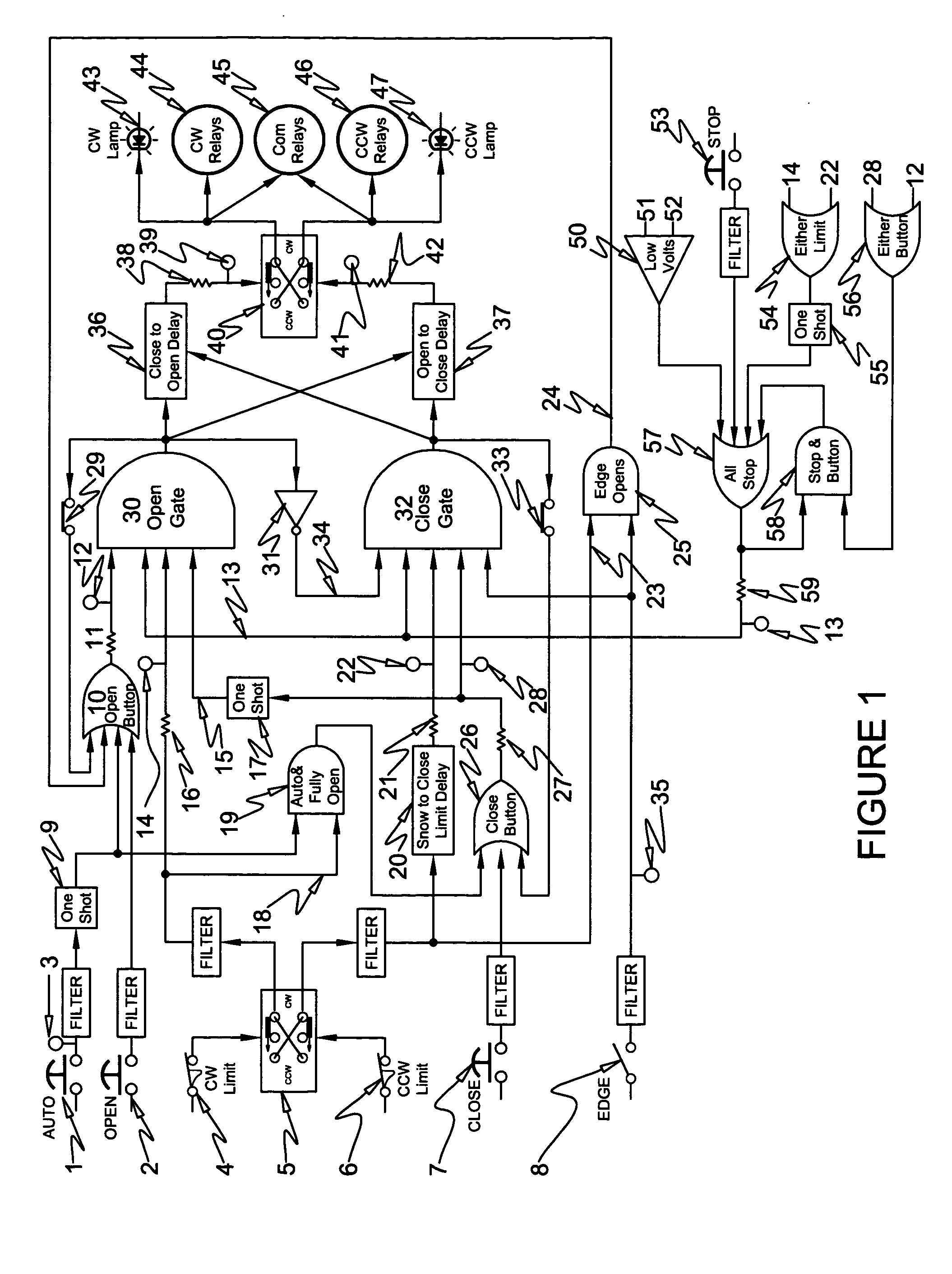

Electronic industrial motor operator control system

InactiveUS20050174080A1Improve reliabilityImprove accuracyDC motor speed/torque controlEmergency protective circuit arrangementsLow voltageEngineering

This invention discloses an electronic control system for an Industrial Motor Operator that uses standard steady state logic to improve reliability in rough service wet and dirty environments. It includes means of providing electronic snow limit to close limit sensing removing the need for two switches and radically improving its accuracy. A low voltage switch reverses the high voltage motor wires and at the same time reverses the open limit, close limit, and snow limit sensors mechanical positions. It discloses a system using lamps to indicate that the power wiring is connecting to three-phase motors in the correct sequence or that single-phase motors have their windings correctly phased.

Owner:MECHANICAL INGENUITY CORP

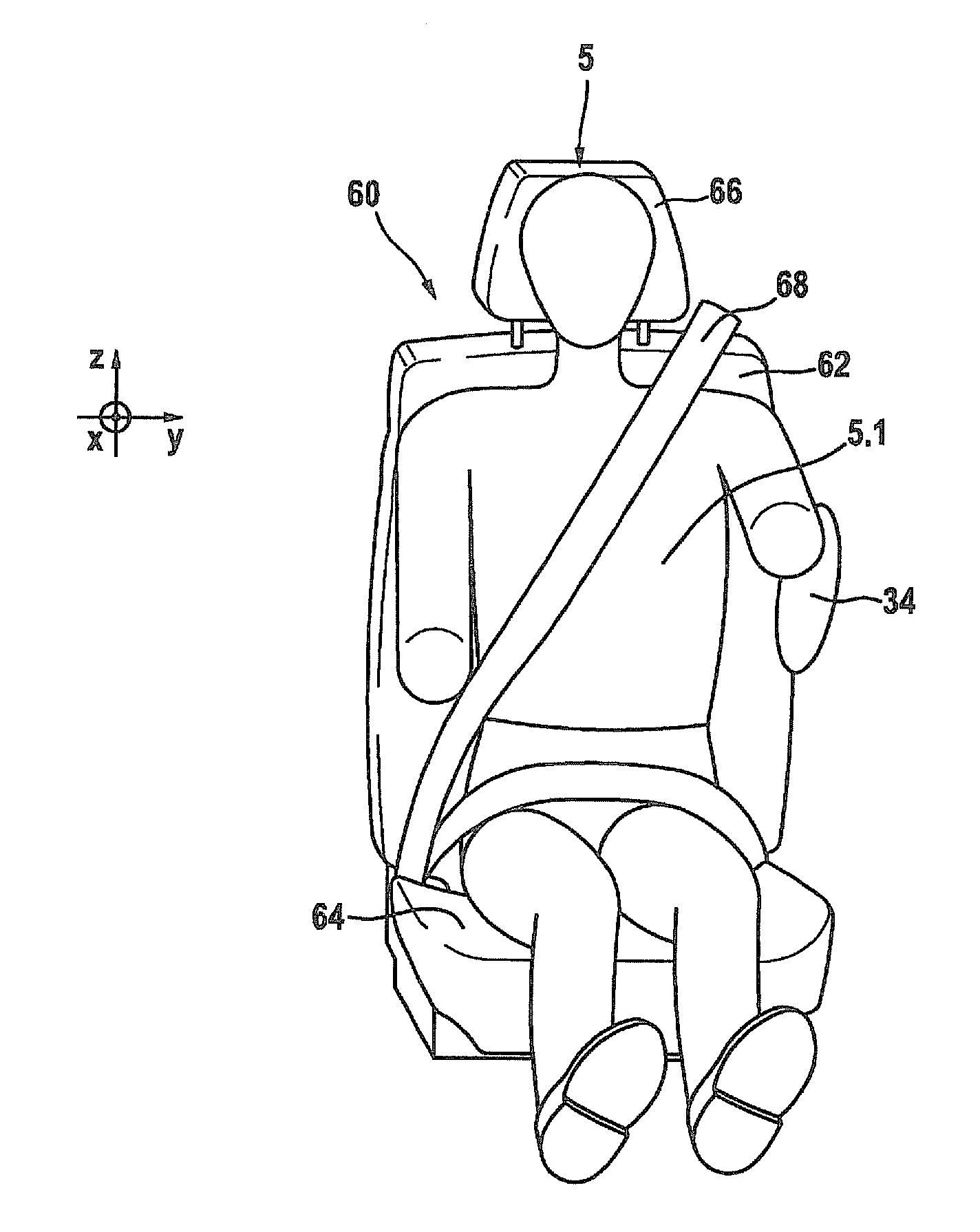

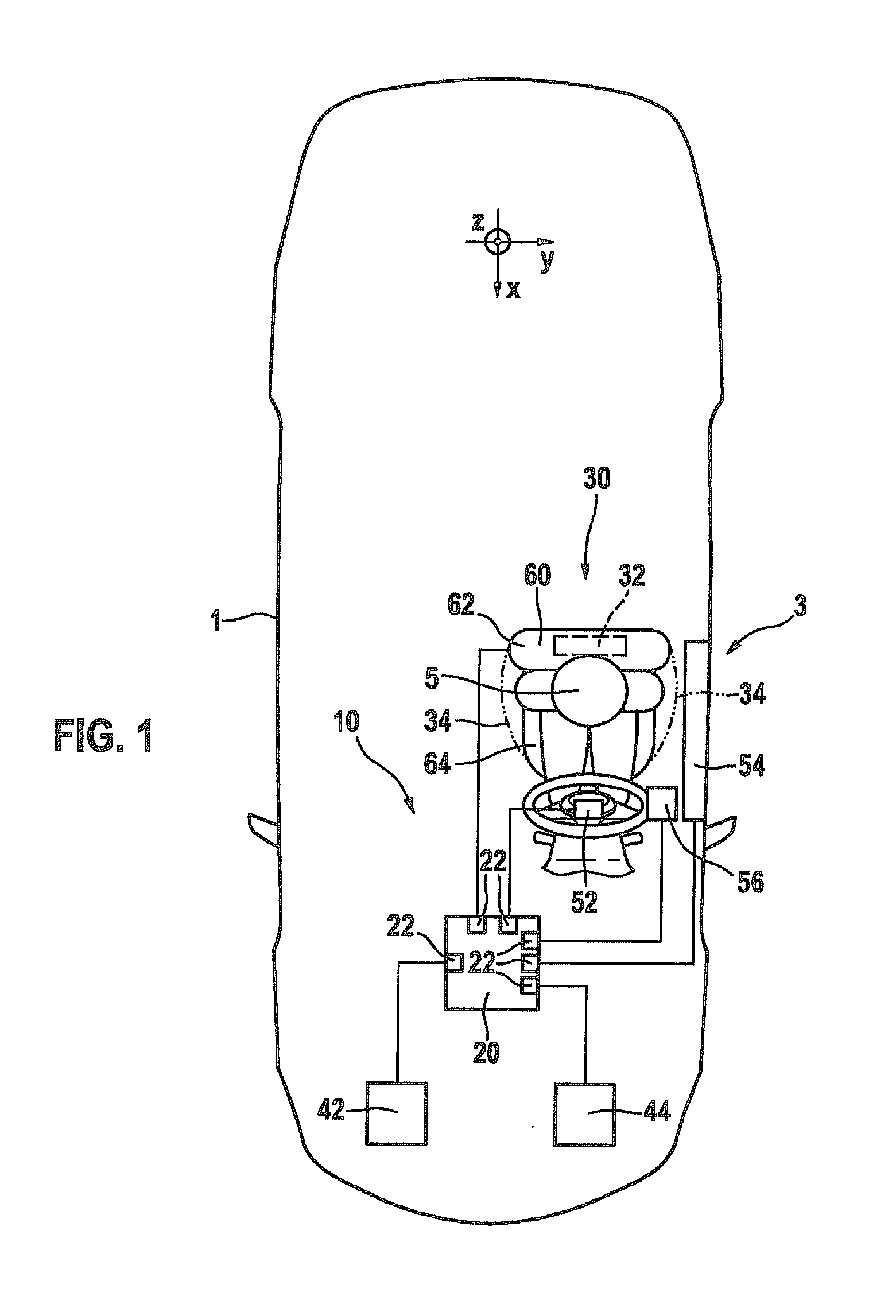

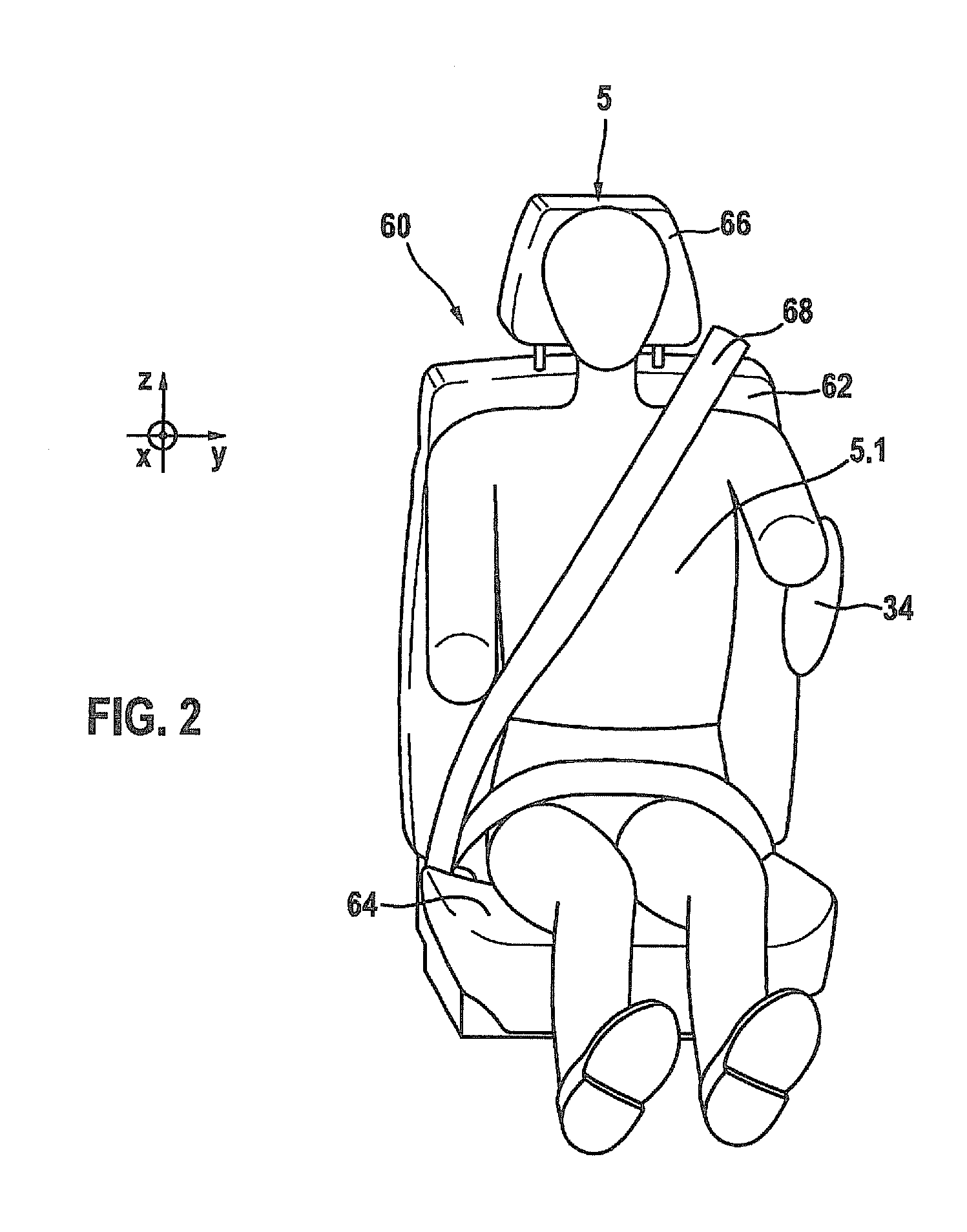

Method and device for protecting and restraining a passenger and an evaluation and control unit for a protection and restraint device

ActiveUS20130026802A1Short time spanIncrease living spaceVehicle seatsDigital data processing detailsMechanical engineeringComputer program

A method for protecting and restraining a passenger on a passenger seat of a vehicle in case of an accident, with the aid of at least one restraint element of a protection and restraint device, an evaluation and control unit for a protection and restraint device for carrying out the method, a protection and restraint device for protecting a passenger having such an evaluation and control unit, as well as a corresponding computer program and computer program product for carrying out the method are described. A positioning applied force is generated as a function of an ascertained current driving situation, the applied force accelerating the passenger away from a vehicle side structure in the direction of the middle of the vehicle if a predefined precrash situation is detected.

Owner:ROBERT BOSCH GMBH

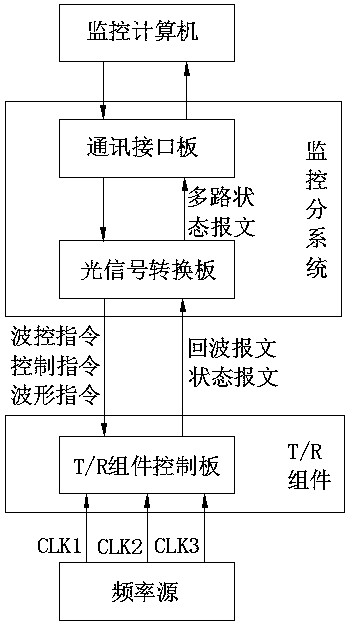

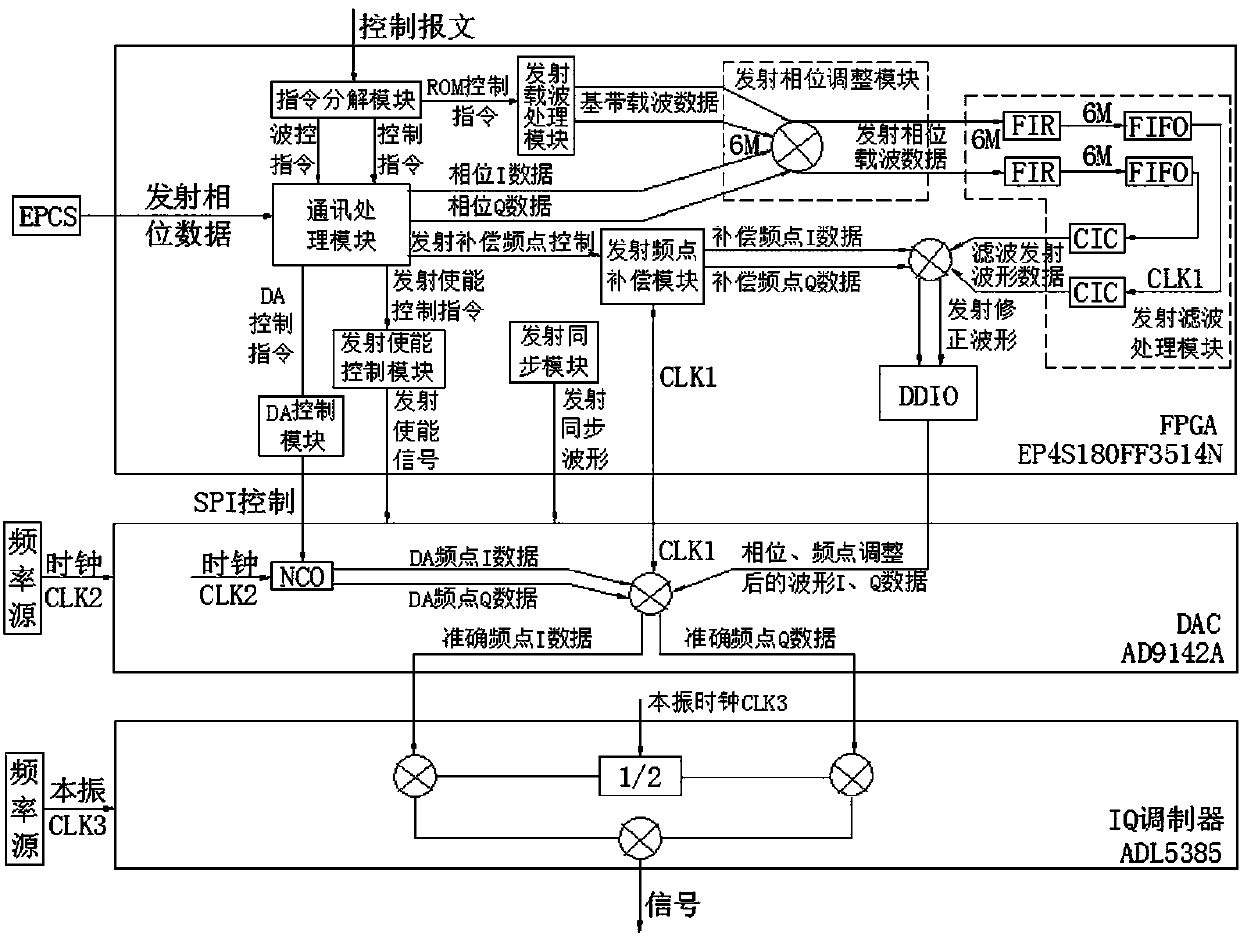

DAC-based radar digital T/R component transmission waveform generation method

ActiveCN110646784ABroaden the bandwidthGuaranteed accuracyRadio wave reradiation/reflectionPhase switchingRadar frequency

The invention relates to a DAC-based radar digital T / R component transmission waveform generation method, and belongs to the technical field of phased array radar digital wave generation. The DAC-based radar digital T / R component transmission waveform generation method comprises six steps, and a baseband carrier waveform is added on the basis of a digital waveform that is directly generated by adigital-to-analog converter DAC to effectively widens the bandwidth of a digital signal; an additional frequency point generated by NCO in a field-programmable gate array FPGA + a stable frequency point in the vicinity of a required frequency point and generated by the digital-to-analog converter DAC are imported to ensure the accuracy of all frequency points in a radar transmission bandwidth, andmeanwhile, the radar frequency point switching rate is improved; the operation and implementation are simple and convenient, and a digital T / R component can generate transmission waveforms with accurate frequency points, high frequency point and phase switching speed, diverse waveforms, stable phase and large bandwidth. The problems that the digital signal bandwidth of the transmission waveform is relatively wide, a part of frequency points in the transmission bandwidth is not accurate, and that the frequency conversion speed is low caused by the own characteristic defects of the digital-to-analog converter DAC are solved.

Owner:JINGZHOU NANHU MACHINERY CO LTD

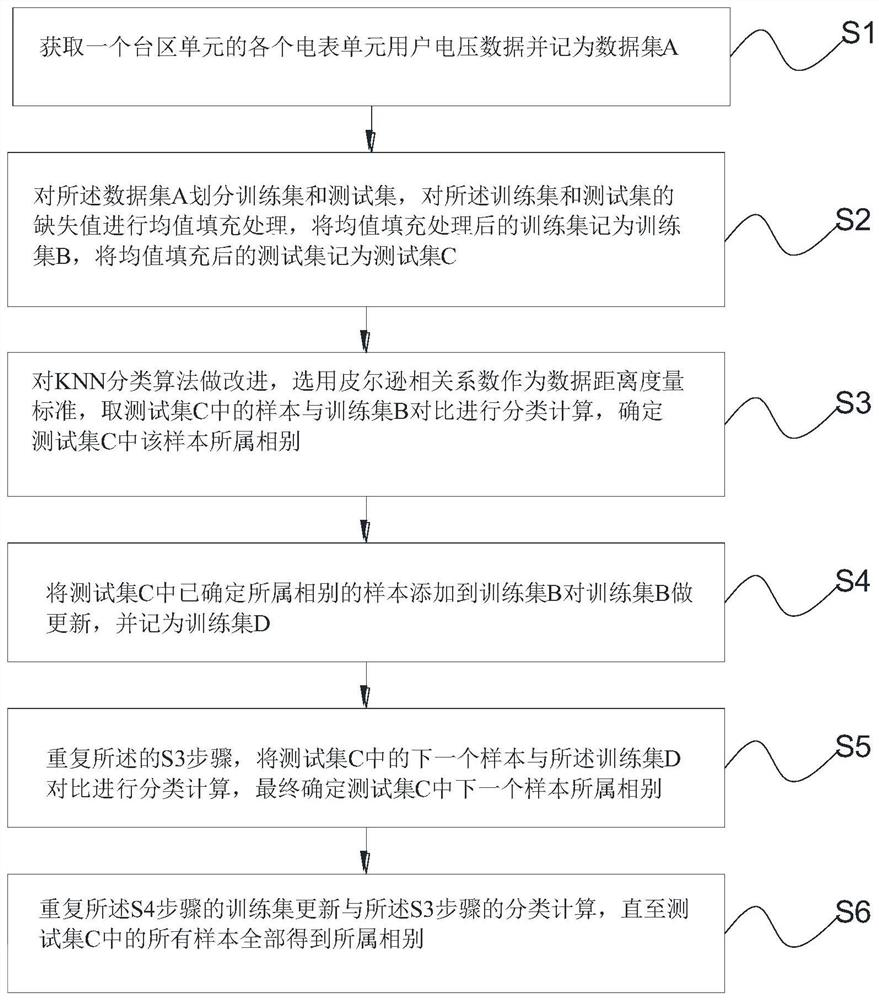

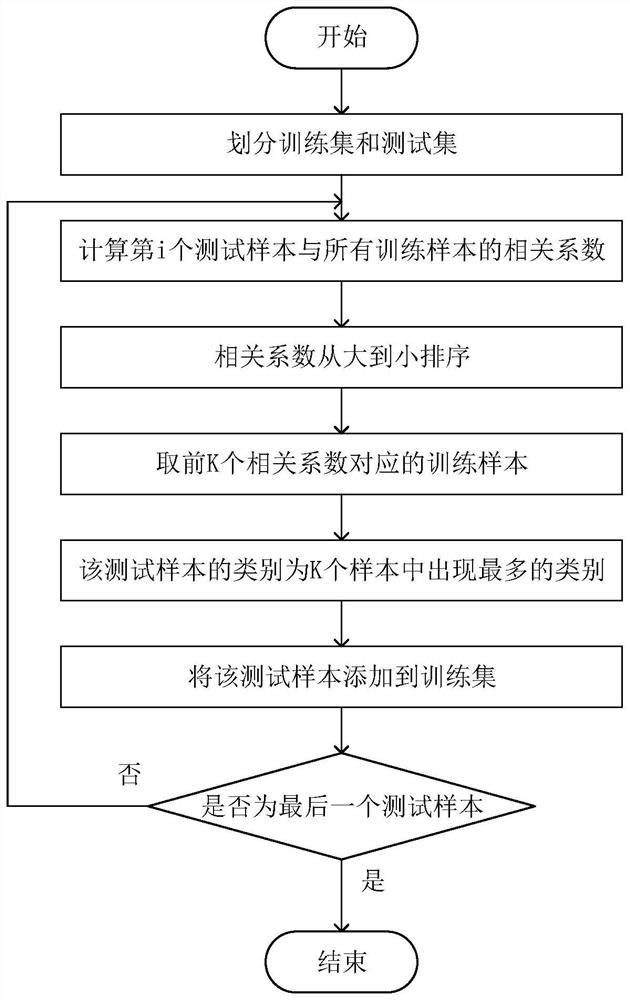

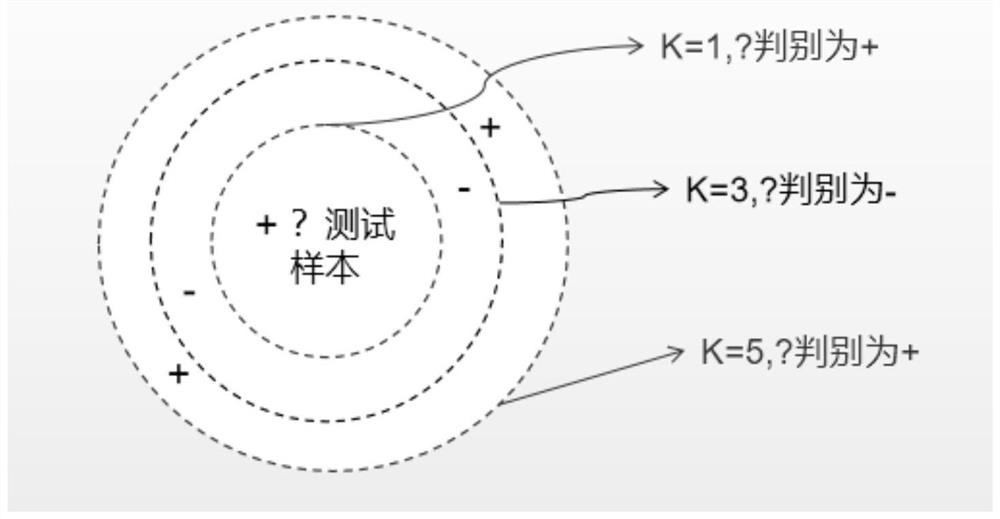

Distribution network electrical topology identification method and system based on edge calculation improved KNN

PendingCN112288015ARelieve pressureReduce computing and storage pressureCharacter and pattern recognitionTopology identificationData set

The invention discloses a distribution network electrical topology identification method and system based on an edge calculation improved KNN, and relates to the technical field of topology identification in the field of distribution networks, and the method comprises the steps: S1, obtaining user voltage data, and recording the user voltage data as a data set A; S2, dividing the data set A into atraining set and a test set, performing mean value filling processing, and recording the data set A as a training set B and a test set C; s3, improving a KNN classification algorithm, taking a samplein the test set C to calculate with the training set B, and determining a phase to which the sample in the test set C belongs; S4, adding tested samples in the test set C into the training set B forupdating, and recording the samples as a training set D; s5, repeating the step S3, calculating the next sample in the test set C and the training set D, and determining the phase to which the next sample in the test set C belongs; and S6, repeating the training set updating in the step S4 and the classification calculation in the step S3 to obtain all phases to which the test set C belongs, thereby overcoming the problems of low topology identification efficiency and overlarge data processing pressure of the acquisition master station in the prior art.

Owner:STATE GRID SICHUAN ELECTRIC POWER CORP ELECTRIC POWER RES INST