Frequency discriminator, PAM4 clock data frequency locking method, recovery method and circuit

A clock data recovery, frequency locking technology, applied in the direction of electrical components, automatic power control, etc., can solve the problem of unable to lock the frequency, the output gain of the frequency discriminator is reduced, and the frequency is falsely locked.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

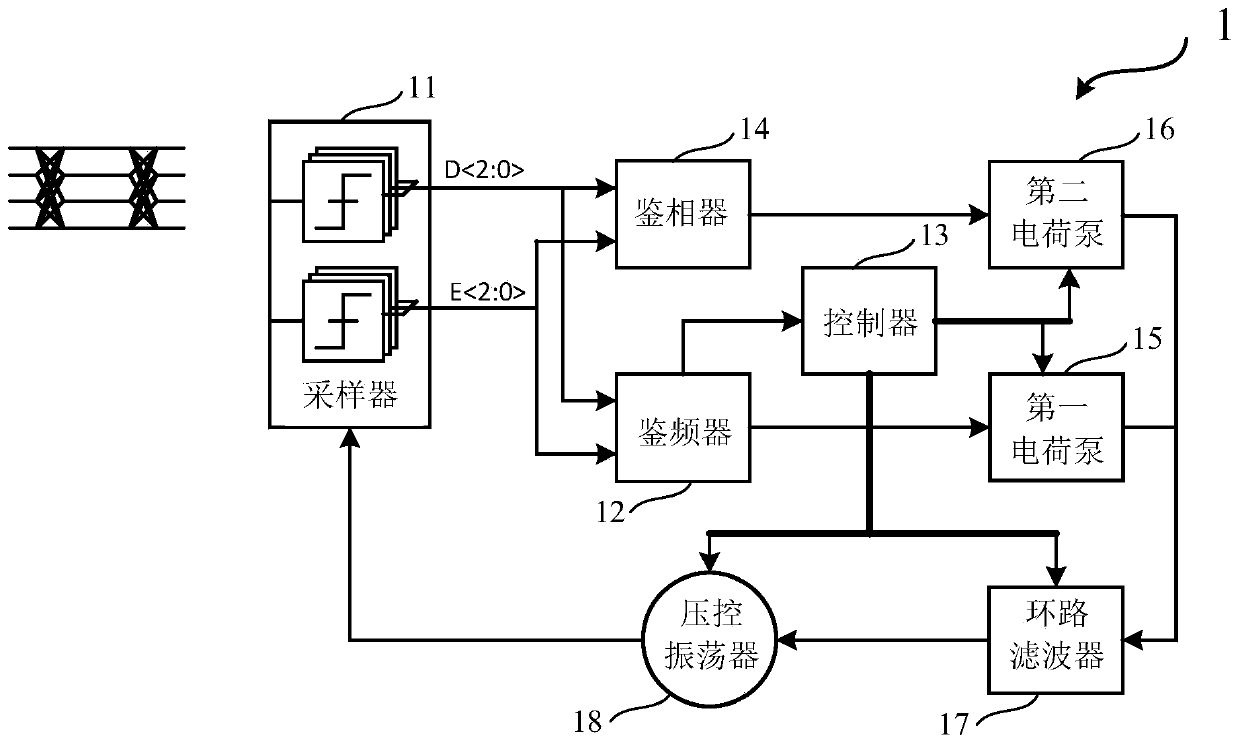

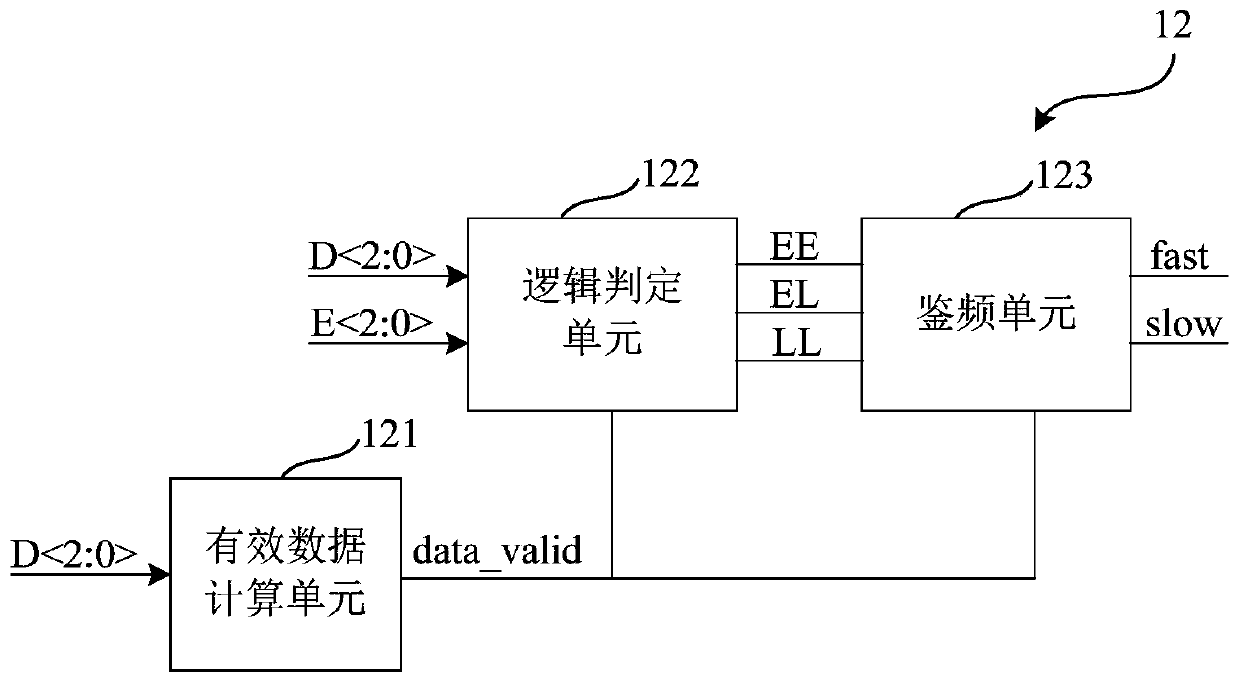

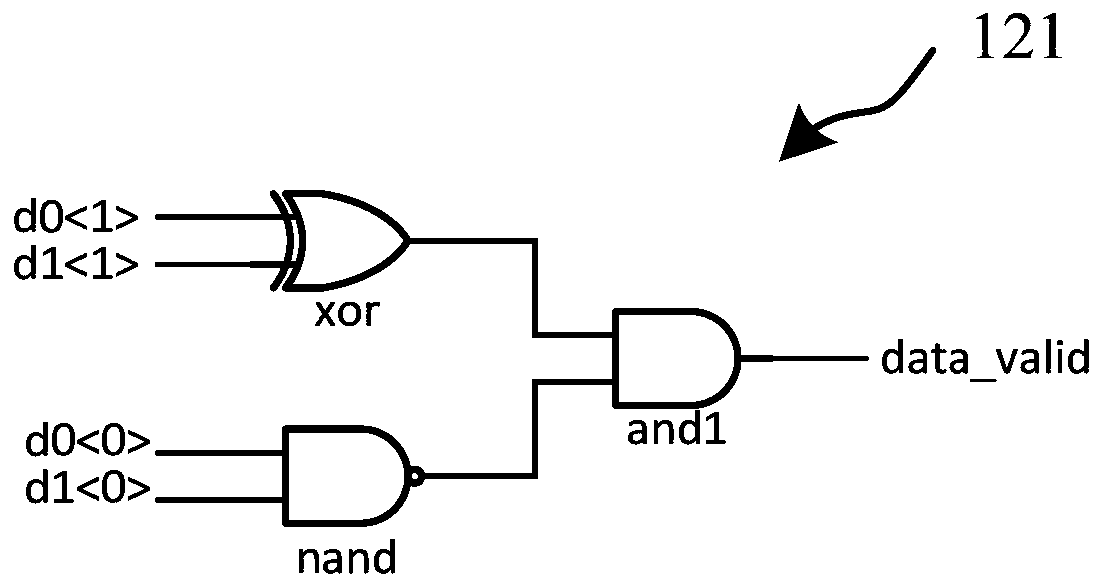

[0099] Such as Figure 1 to Figure 5 As shown, the present embodiment provides a PAM4 clock data recovery circuit 1, and the PAM4 clock data recovery circuit 1 includes:

[0100] Sampler 11 , frequency discriminator 12 , controller 13 , phase detector 14 , first charge pump 15 , second charge pump 16 , loop filter 17 and voltage controlled oscillator 18 .

[0101] Such as figure 1 As shown, the sampler 11 receives the input signal, the data sampling clock CK1 and the edge sampling clock CK2, and based on the first sampling CK1 and the edge sampling clock CK2, the data of the fourth-order pulse amplitude modulation signal PAM4 and the The edge is sampled to obtain the sampling data D and the sampling edge E.

[0102] Specifically, the sampler 11 includes a plurality of sampling units for sampling the input signal data and edges based on different reference values. In this embodiment, the input signal is a fourth-order pulse amplitude modulation signal PAM4. Since the fourth-...

Embodiment 2

[0128] Such as Figure 2 to Figure 19 As shown, the present embodiment provides a PAM4 clock data recovery method. In this embodiment, the PAM4 clock data recovery method is implemented based on the PAM4 clock data recovery circuit 1. In practical applications, the PAM4 clock data recovery The method can be implemented based on any hardware circuit or software code that can realize the method, and details will not be repeated here. The PAM4 clock data recovery method comprises:

[0129] 1) Open loop frequency approximation.

[0130] Specifically, in the start-up phase, the frequency difference between the sampling clock and the fourth-order pulse amplitude modulation signal PAM4 is large, and the controller 13 configures the PAM4 clock data recovery circuit 1 in an open-loop frequency approximation mode, that is, the first A charge pump 15 , the second charge pump 16 and the loop filter 17 are all in an off state.

[0131] Specifically, the voltage-controlled oscillator 18 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More