Method for generating parity-check matrix

A parity check matrix and check node technology, applied in the field of low-density parity check code rearrangement, can solve the problem of not taking into account the short loop effect, affecting the correctness of check node calculation results, etc., to reduce dependencies Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] Certain terms are used in the specification and subsequent claims to refer to particular components. Those of ordinary skill in the art will appreciate that manufacturers may refer to the same component by different terms. This specification and subsequent patent applications do not use the difference in name as a way to distinguish components, but use the difference in function of components as a criterion for distinguishing. "Includes" and "comprising" mentioned throughout the specification and subsequent claims are open-ended terms, so they should be interpreted as "including but not limited to". In addition, the term "coupled" includes any direct and indirect electrical connection means. Indirect means of electrical connection includes connection through other means.

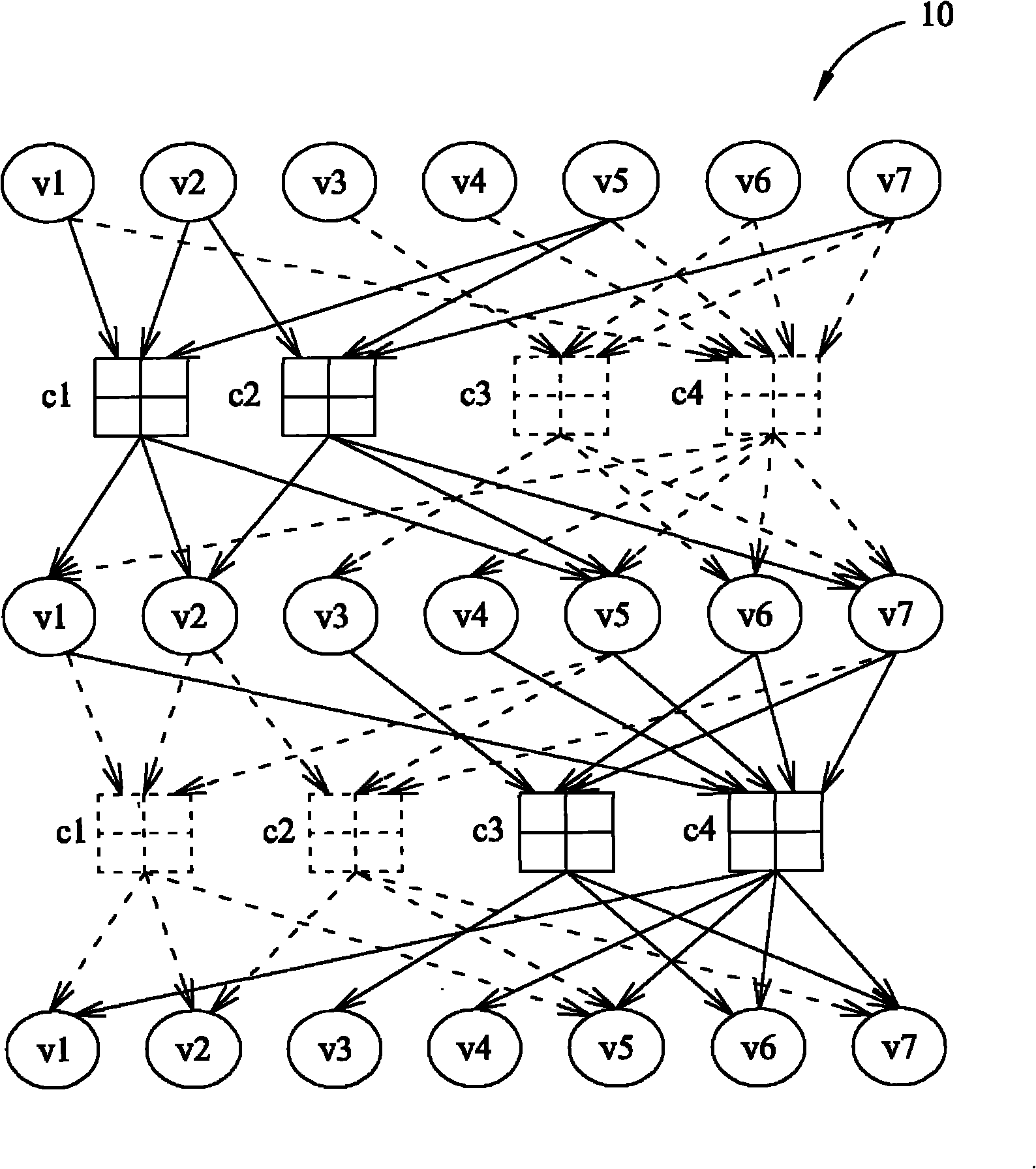

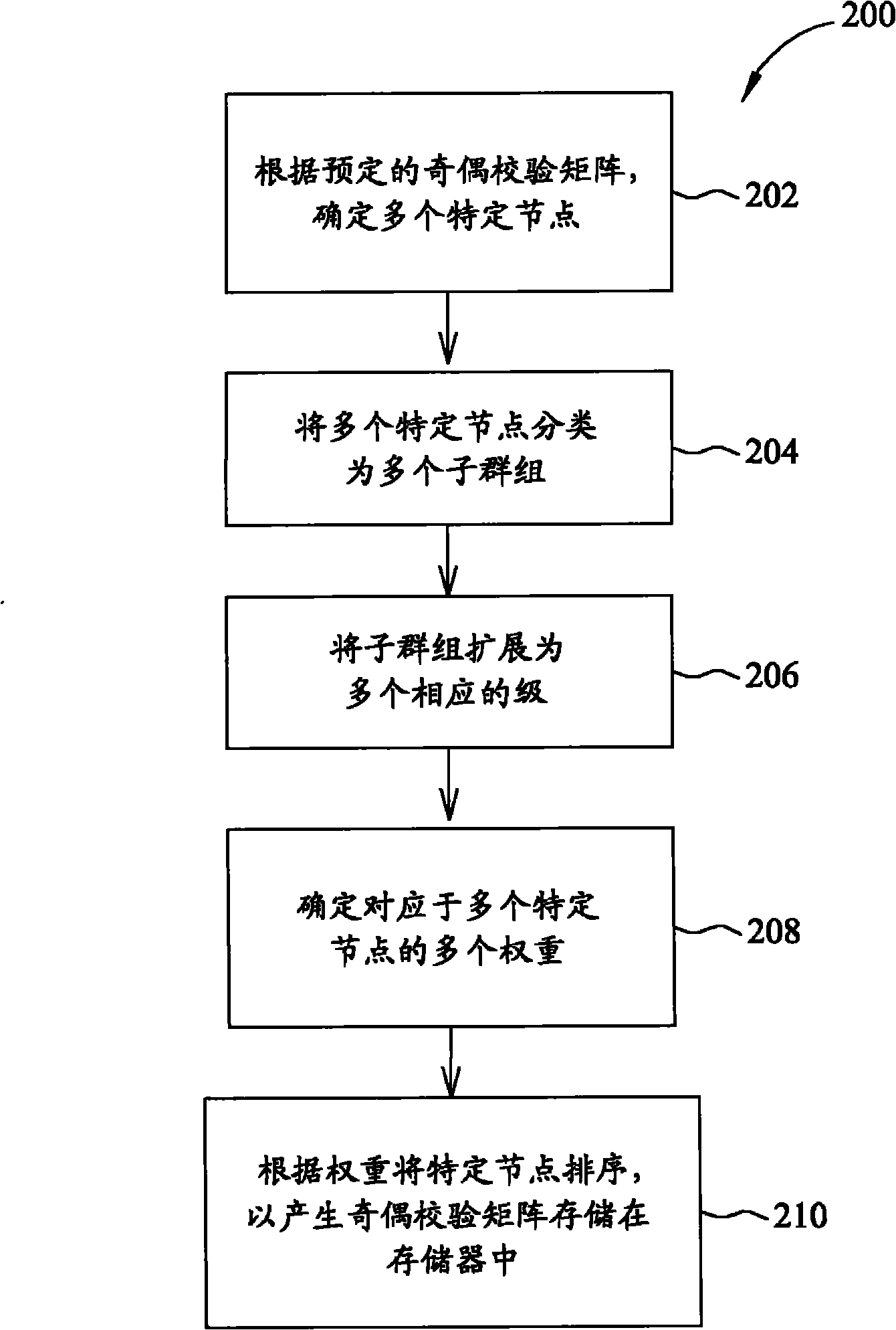

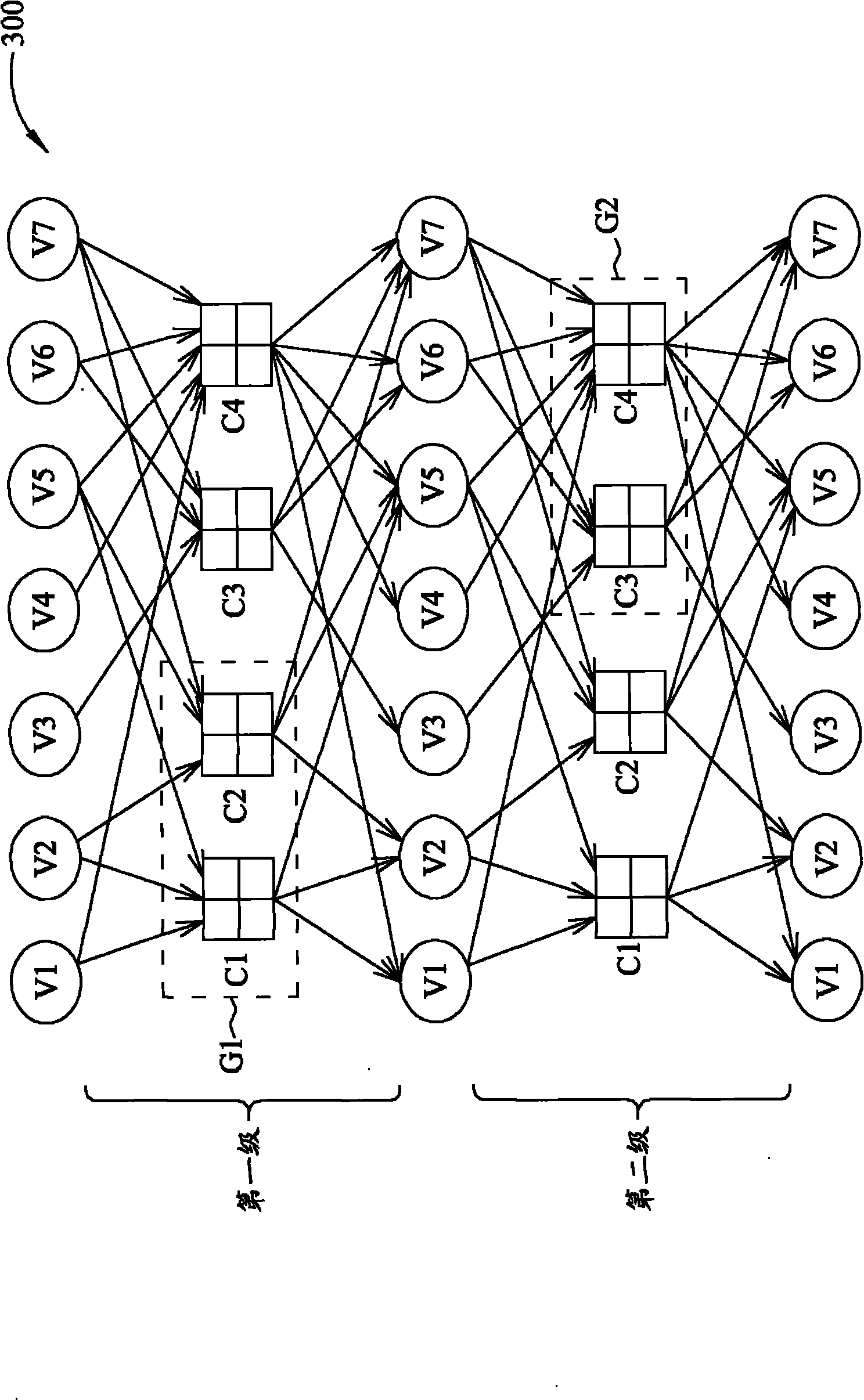

[0015] see figure 2 and image 3 . figure 2 is a flowchart of a method 200 for generating a parity check matrix H' to decode a plurality of underdetermined nodes V1, V2, V3, V4, V5, V6, V7 acco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com