Device for realizing fixed forwarding delay of V.24 interface multiplexer

A fixed forwarding and multiplexer technology, applied in multiplexing communication, time-division multiplexing systems, electrical components, etc. Delay compensation error and realize the effect of clock synchronization in the network

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described below in conjunction with the accompanying drawings.

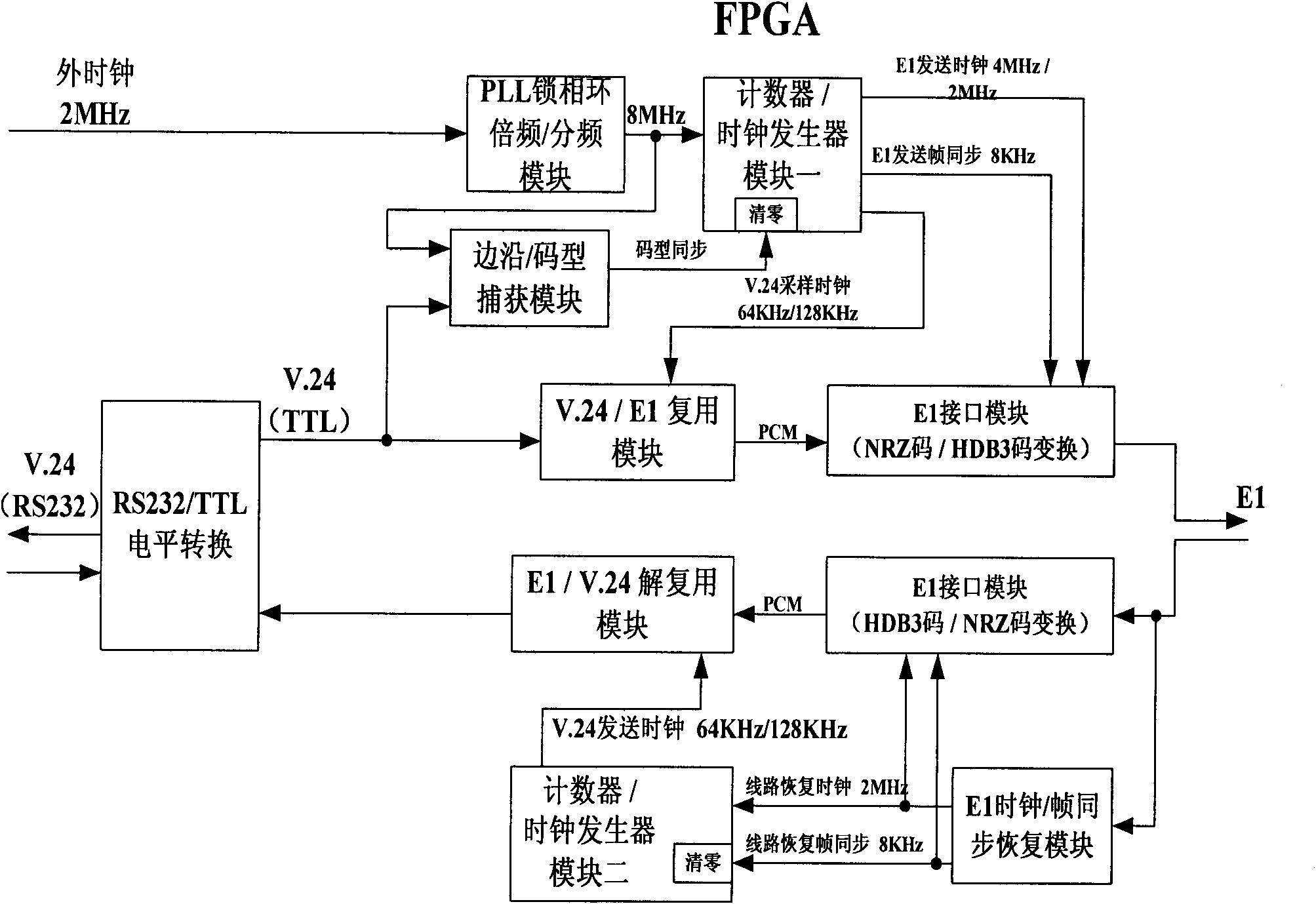

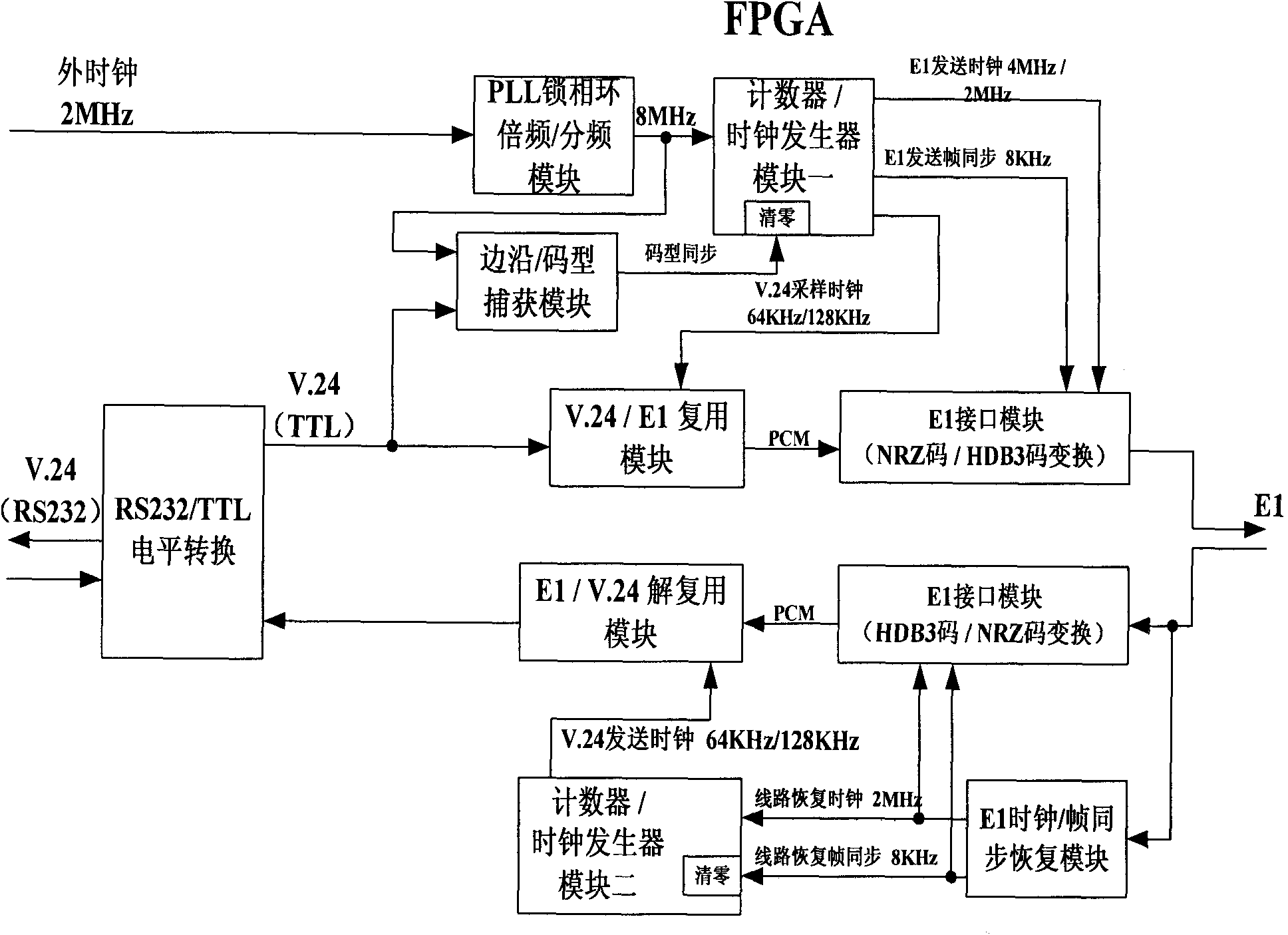

[0031] The structure diagram of the present invention is as figure 1 As shown, using programmable gate array (FPGA) technology, FPGA includes the following modules: PLL phase-locked loop frequency multiplication / division module, edge / pattern capture module, counter / clock generator module 1, V.24 / E1 complex Use module, E1 interface module——NRZ code / HDB3 code conversion, E1 interface module——HDB3 code / NRZ code conversion, E1 clock / frame synchronization recovery module, E1 / V.24 demultiplexing module and counter / clock generator Module Two.

[0032] (1) The function of the PLL phase-locked loop frequency multiplication / frequency division module is to obtain a standard 2MHz clock (2048000Hz ± 50ppm) from the outside, and multiply the frequency to 8MHz inside the module, and output it to the clock generator to generate an internal clock. Output to the edge / pattern capture m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More