Parallel digital signal processor

A digital signal and processor technology, applied in the direction of electrical digital data processing, digital data processing components, concurrent instruction execution, etc., can solve the problems of limited computing power, insufficient parallelism, low price, etc., to meet the needs of data throughput, Effect of Peak Computing Performance Improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described below in conjunction with accompanying drawing.

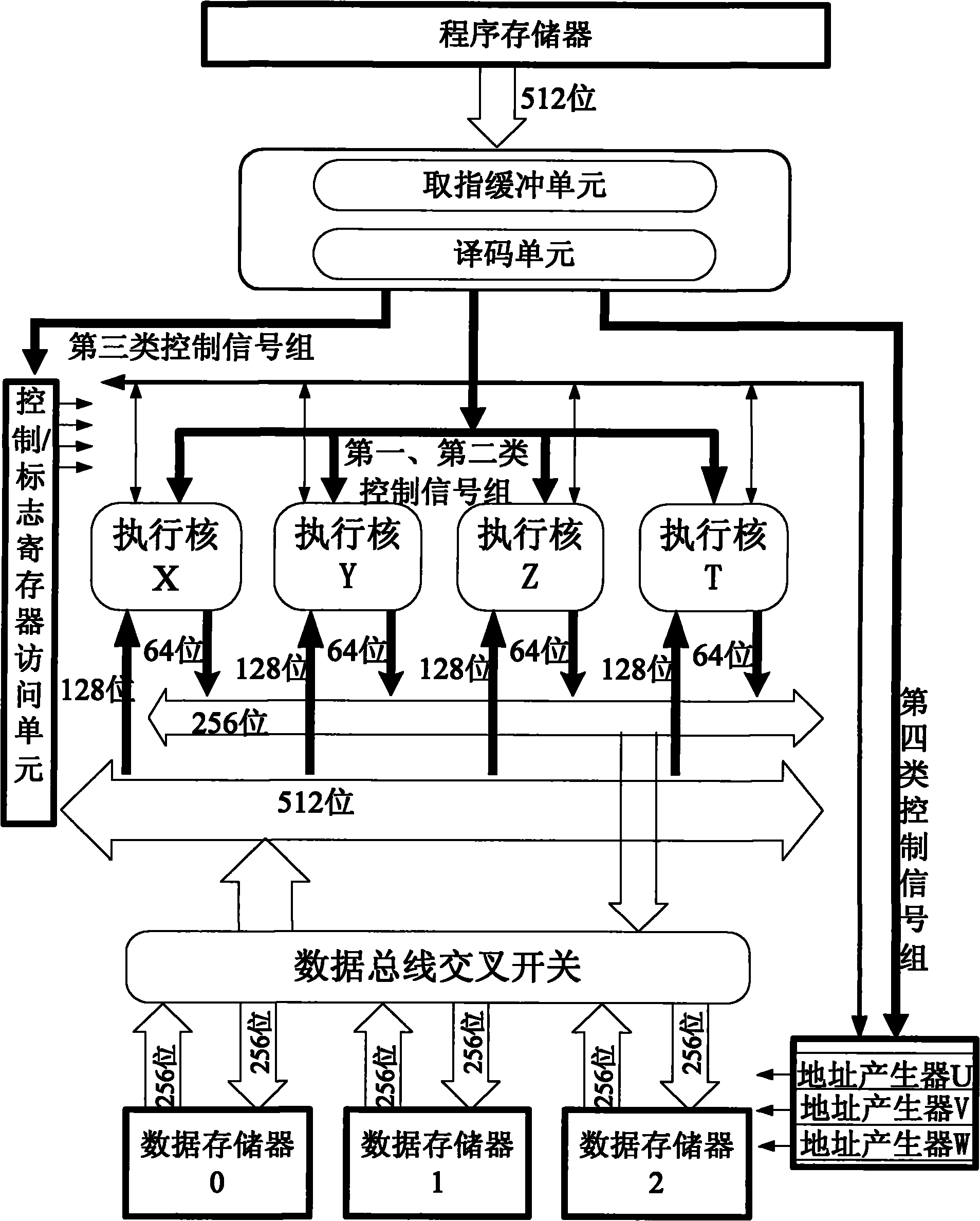

[0039] Such as figure 1 As shown, a parallel digital signal processor adopts a single instruction stream multiple data stream (SIMD) structure, including:

[0040] - Program memory, which is a single-port memory with a width of 16 words, each word is 32 bits wide and 8192 deep, and is used to store application programs;

[0041] - The instruction fetch buffer unit is used to maintain the program counter and provide an address to the program memory, cache instructions from the program memory, splice the instructions into a parallel execution (xīng) row (hāng) and send it to the decoding unit;

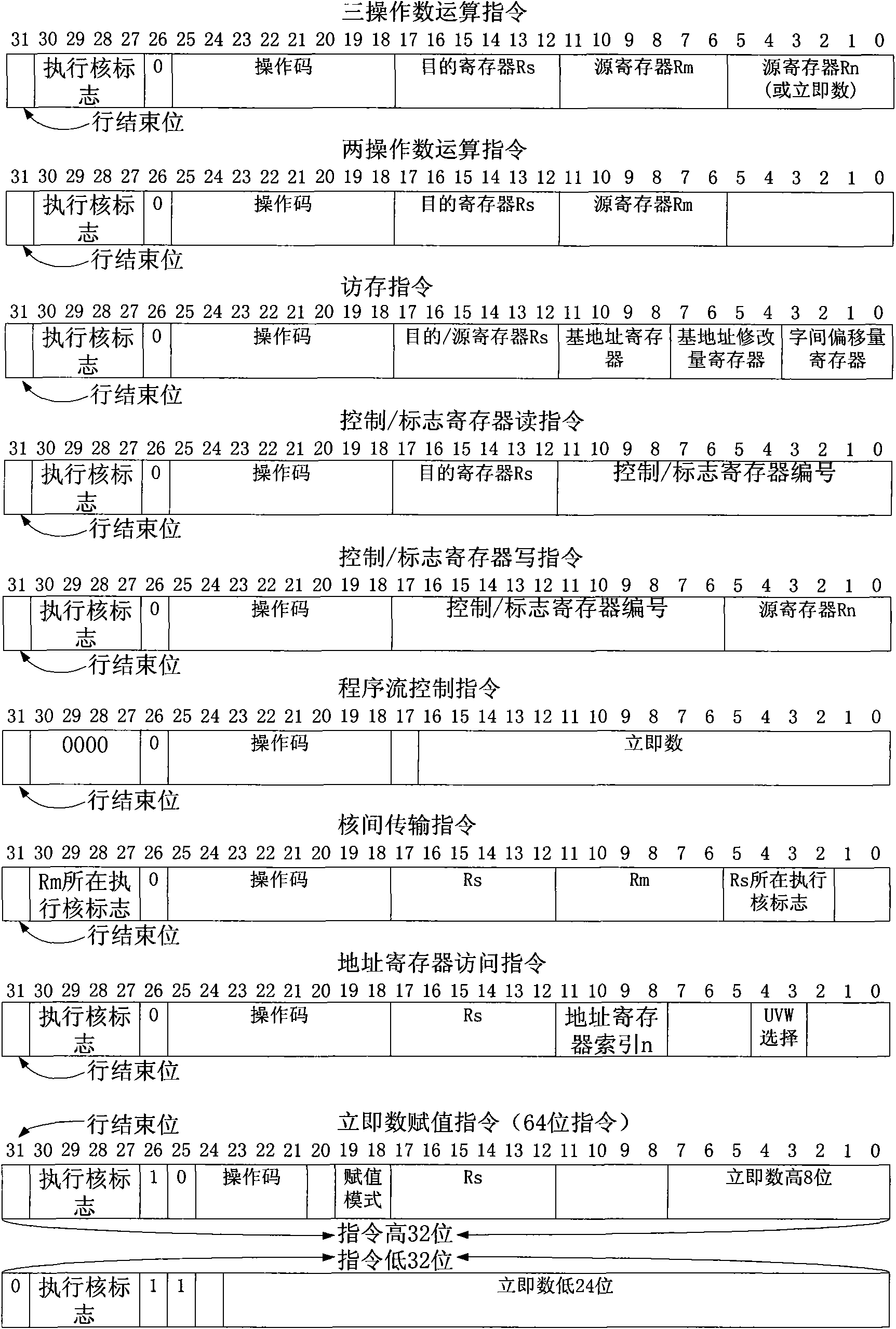

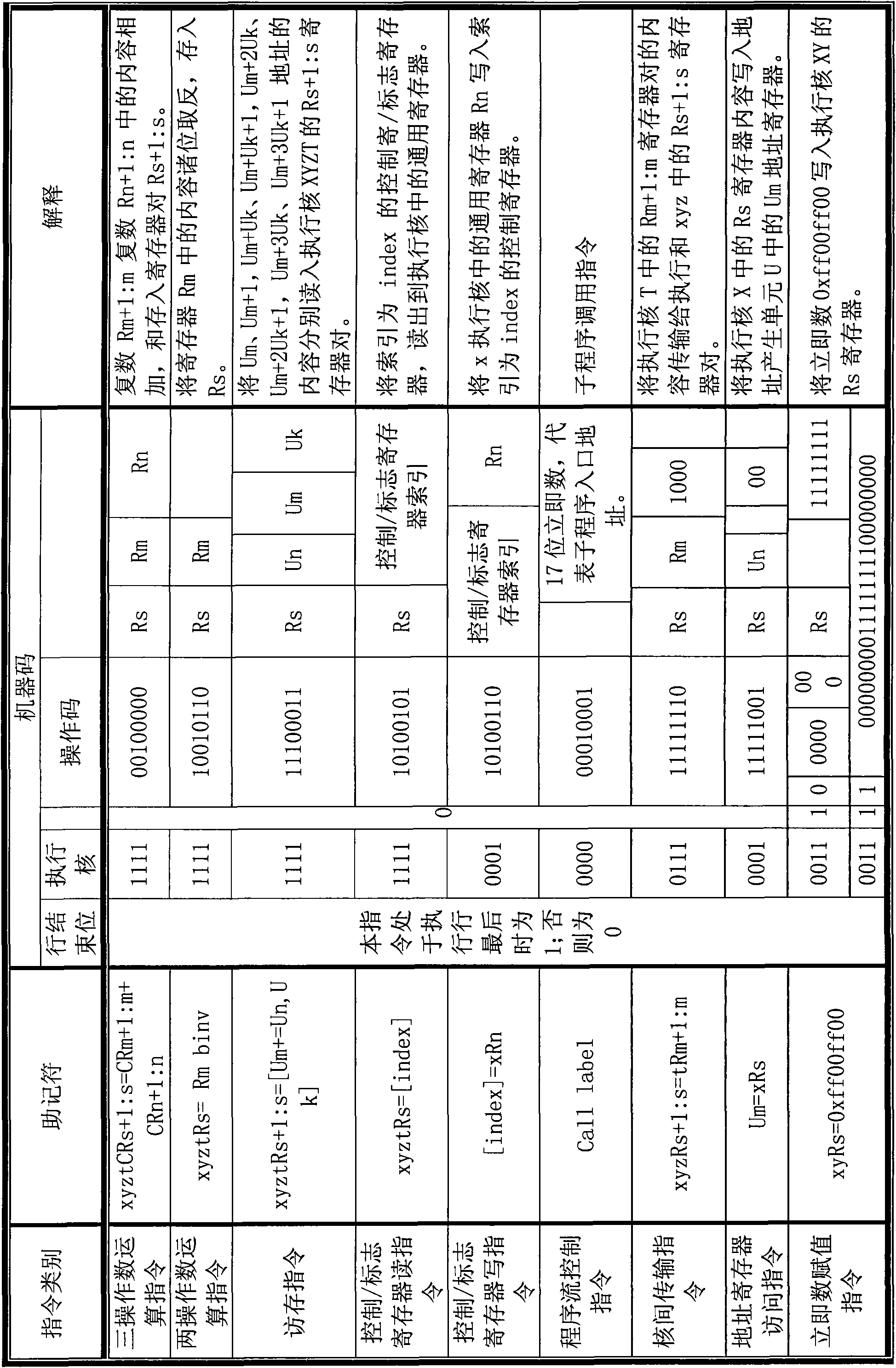

[0042] - a decoding unit, used to decode each instruction in the execution line, according to the machine code arrangement form, the instructions are divided into nine categories, namely, three operand operation instructions, two operand operation instructions, and memory access inst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More