Semiconductor device and method for manufacturing the same

A device manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of metal plug short circuit, shrinkage, position dislocation, etc., to reduce the circuit area, less The effect of restriction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

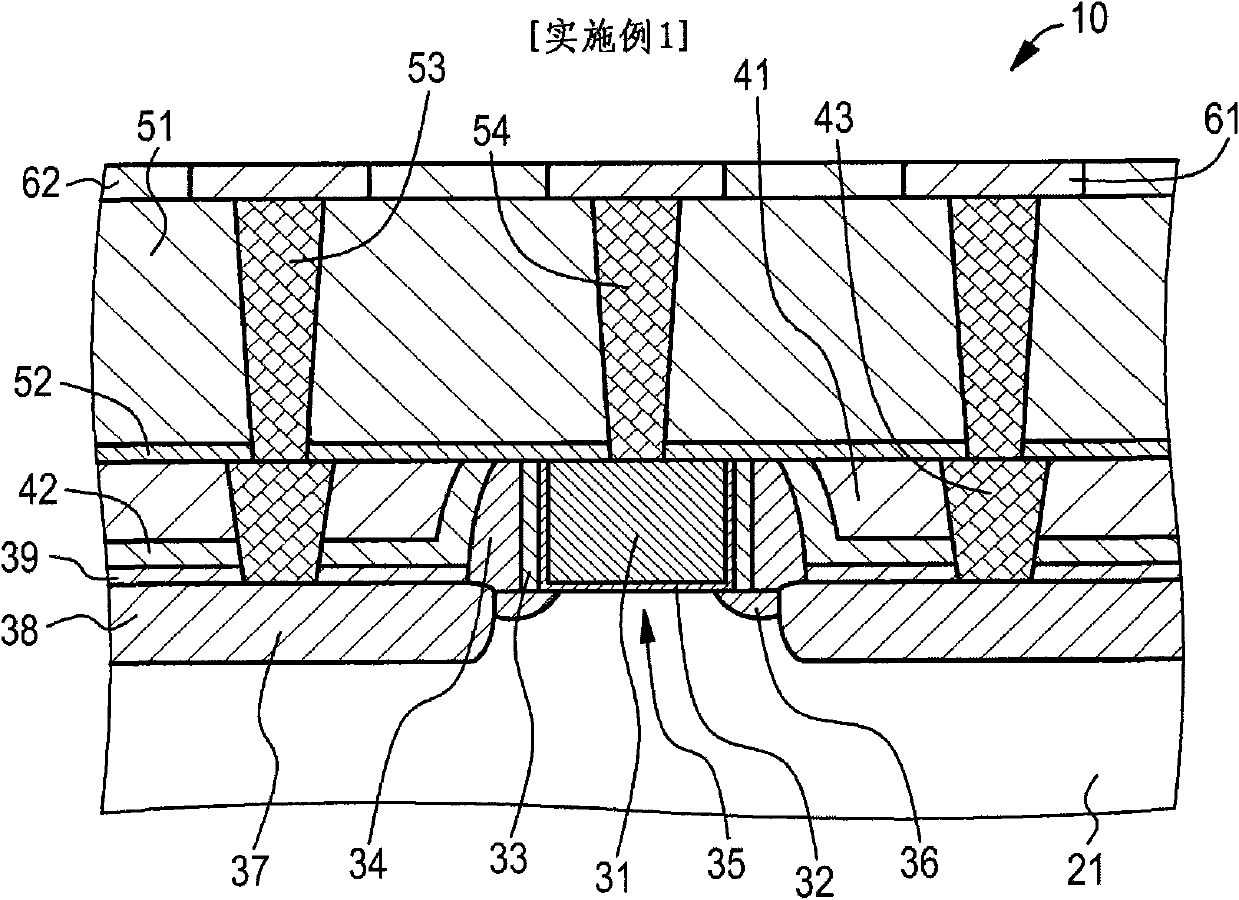

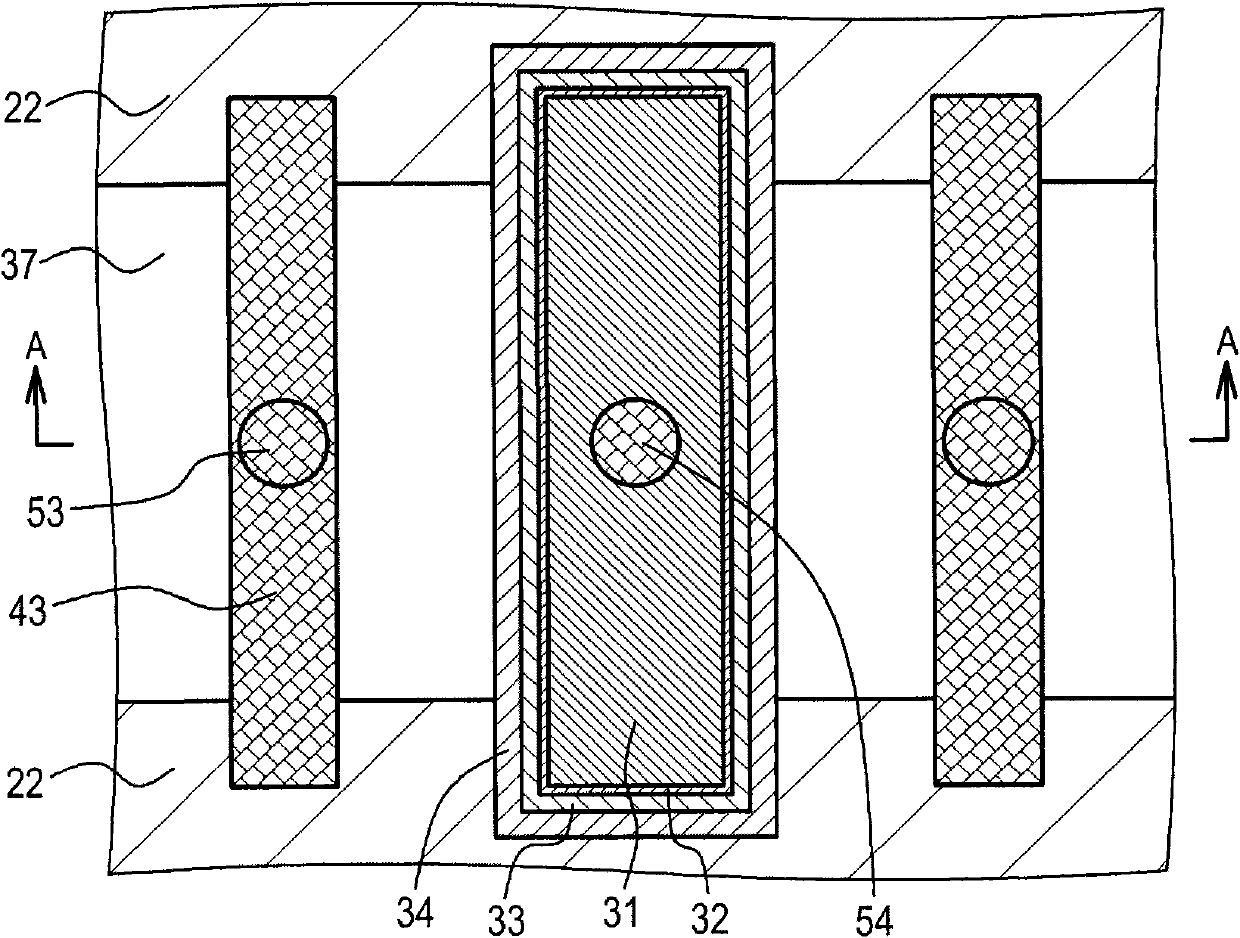

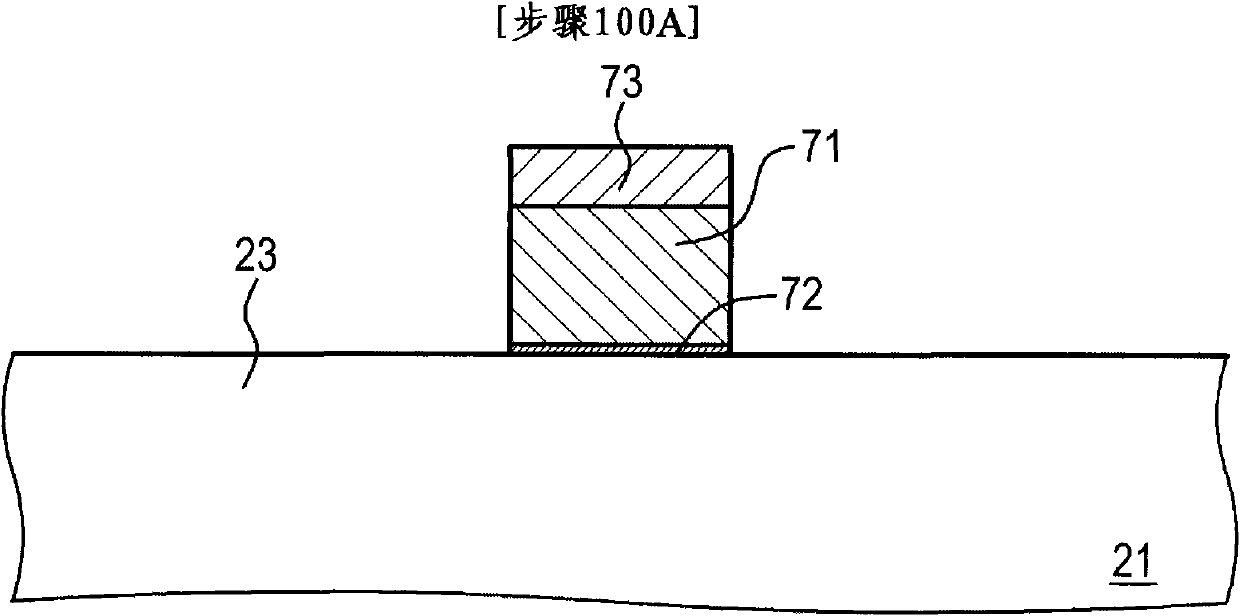

[0043] 2. Example 1 (semiconductor device and semiconductor device manufacturing method according to the first embodiment of the present invention)

Embodiment 2

[0044] 3. Embodiment 2 (modified example of embodiment 1)

Embodiment 3

[0045] 4. Example 3 (semiconductor device and semiconductor device manufacturing method according to the second embodiment of the present invention)

[0046] 5. Embodiment 4 (modified example of embodiment 3, and others)

[0047] 1. General description of semiconductor device and semiconductor device manufacturing method of the present invention

[0048] The semiconductor device or semiconductor device manufacturing method of the first embodiment of the present invention may be suitable for an n-channel semiconductor device or for providing an n-channel semiconductor device in which the first contact portion has tensile stress. Alternatively, the semiconductor device or the manufacturing method of the semiconductor device according to the first embodiment of the present invention may be suitable for a p-channel semiconductor device or for providing a p-channel semiconductor device in which the first contact portion with compressive stress.

[0049] In the semiconductor dev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More