Patents

Literature

32results about How to "No etch damage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

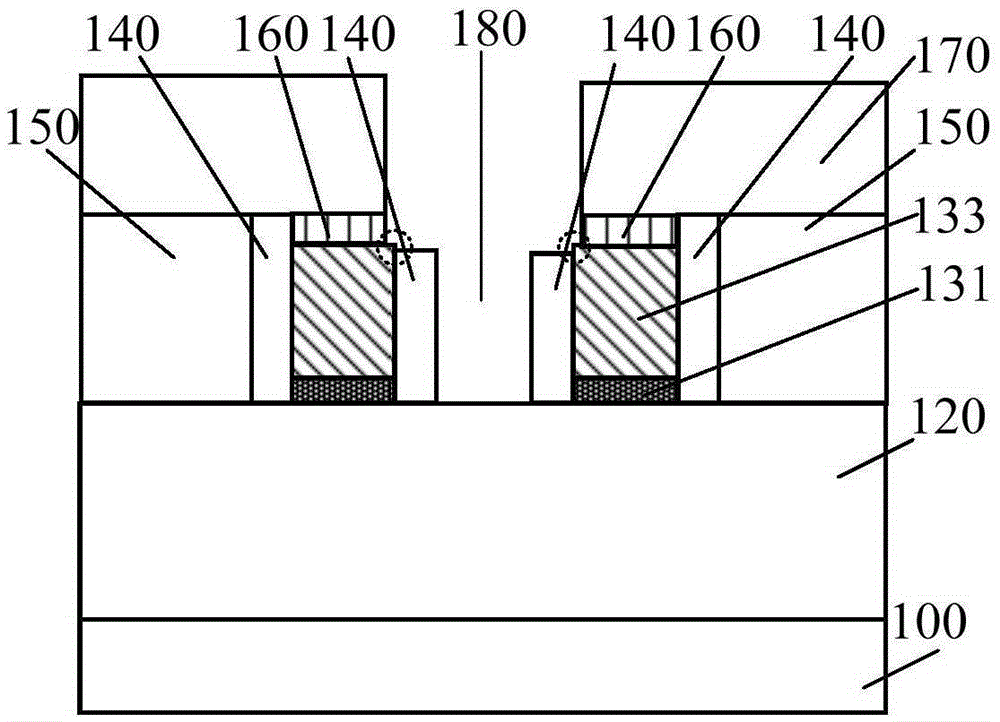

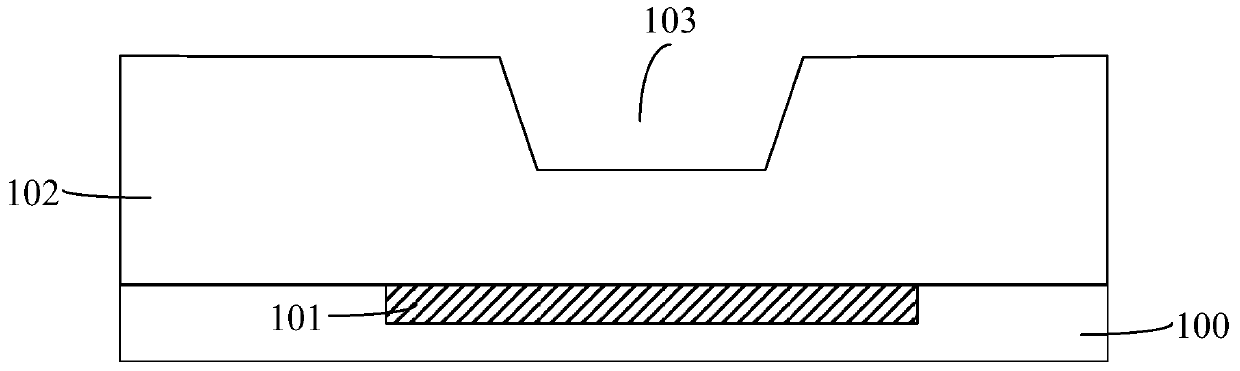

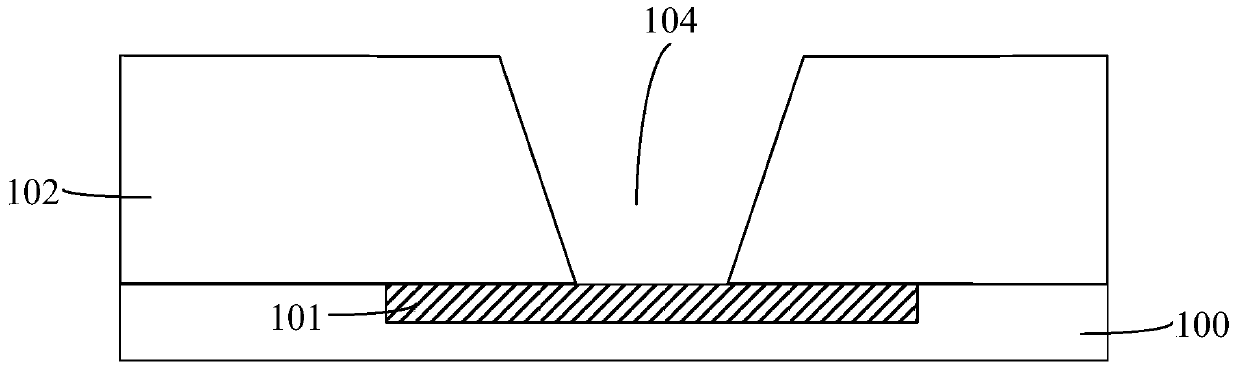

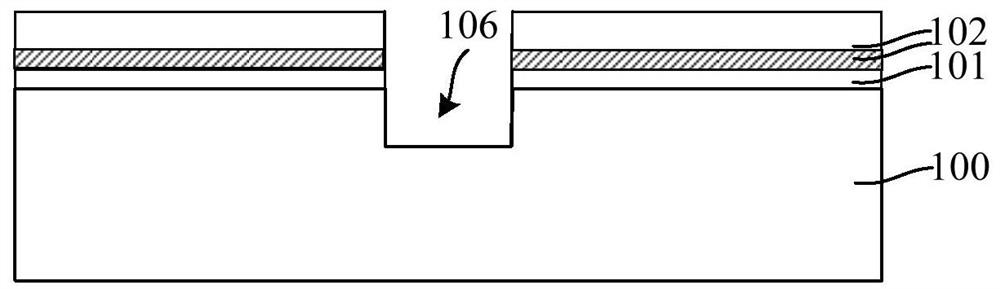

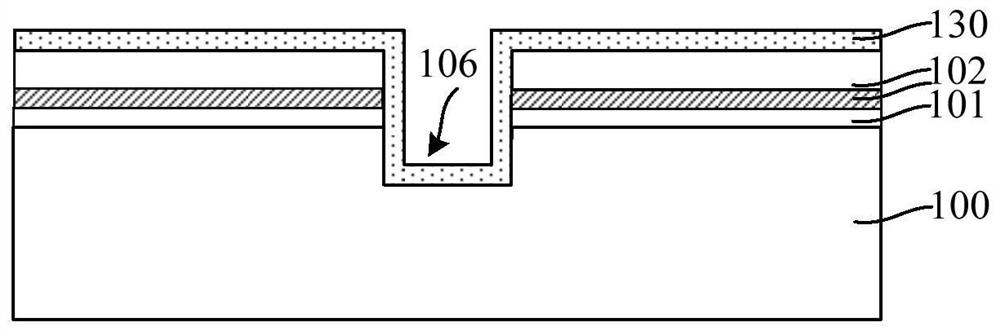

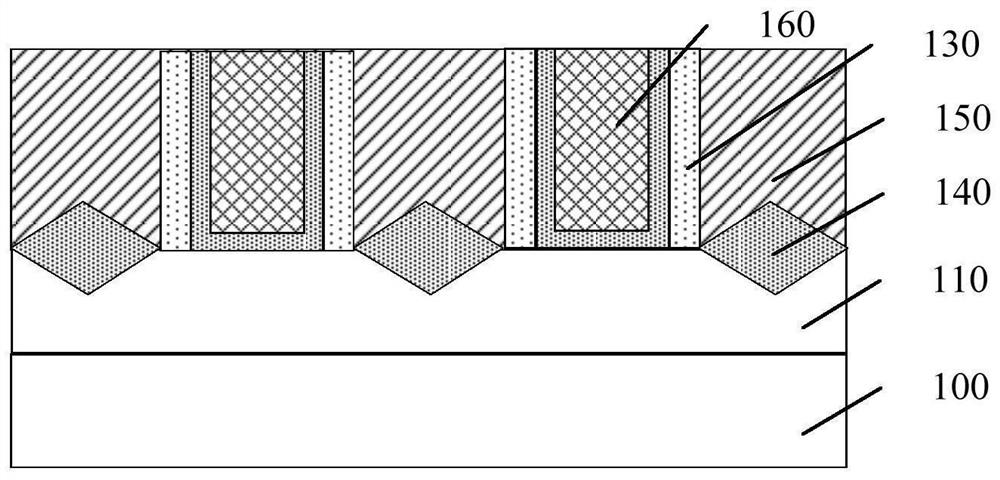

Shallow groove isolation construction manufacturing method

InactiveCN101459115ANo lossImprove adhesionSemiconductor/solid-state device manufacturingEngineeringSilicon oxide

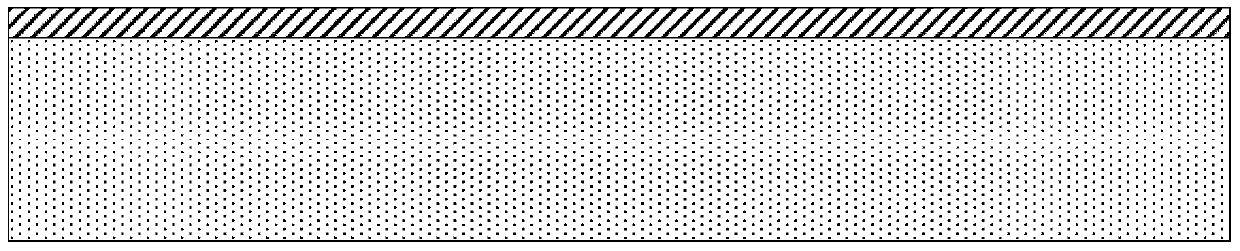

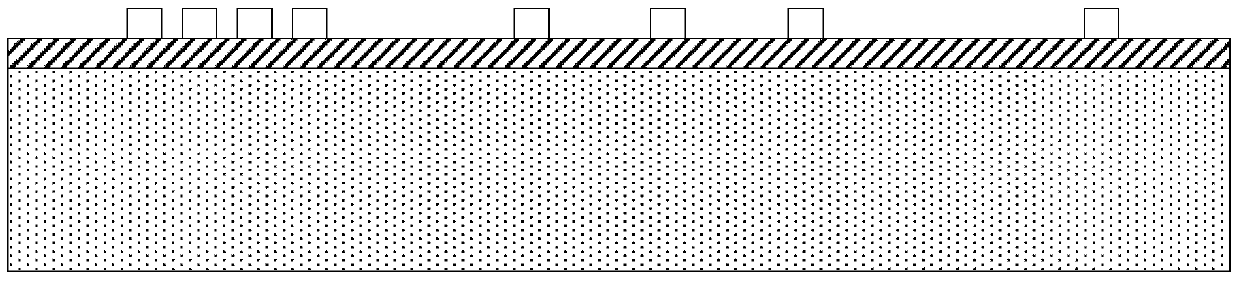

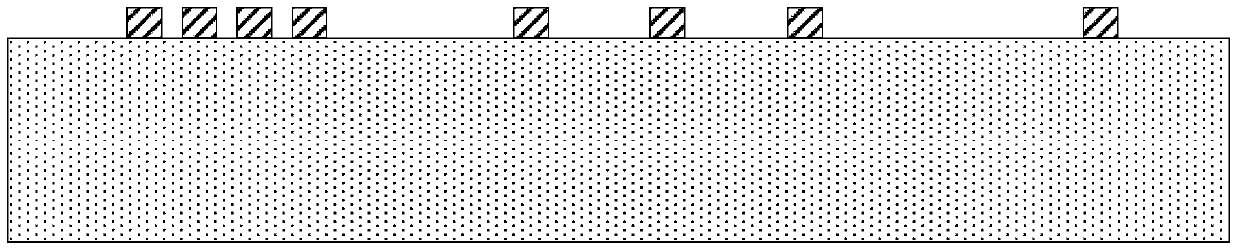

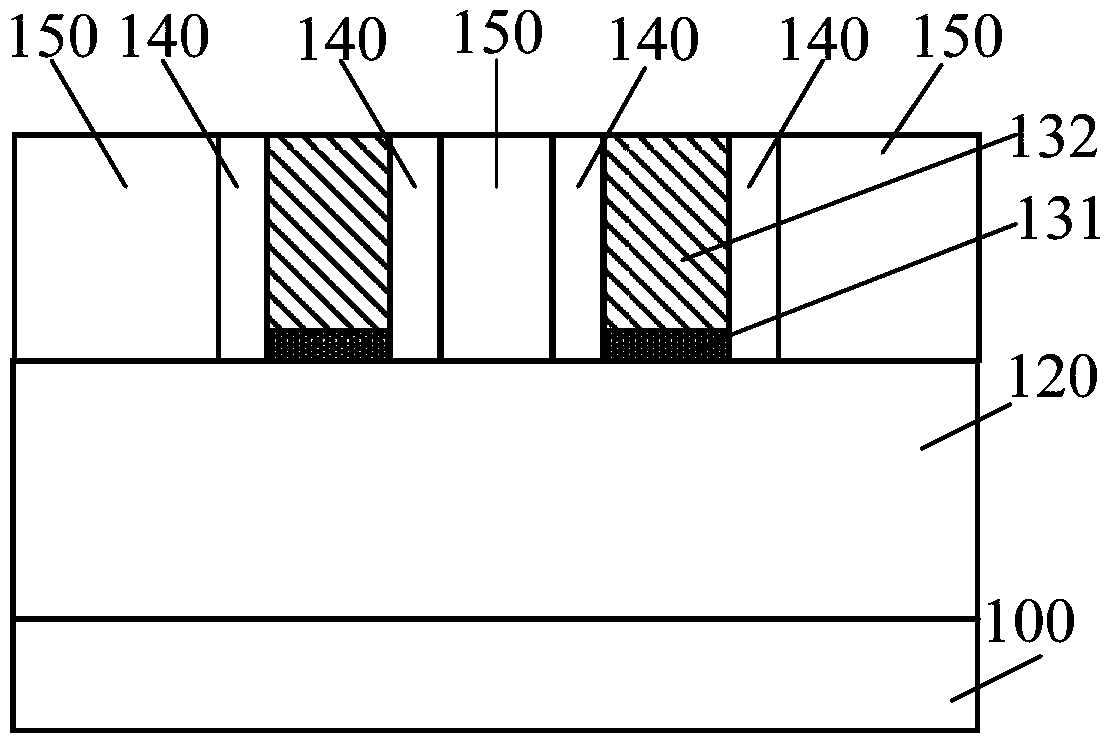

A manufacturing method of a shallow trench isolation structure comprises steps of sequentially forming a first dielectric layer and a hard mask layer on a semiconductor substrate, arranging an opening which penetrates through the hard mask layer and the first dielectric layer and forming a trench in the semiconductor substrate at the bottom of the opening, forming a silicon oxide layer on the inner wall of the trench, etching the hard mask layer on the lateral wall of the opening and keeping the line width of the opening in the hard mask layer to be larger than that of the top portion of the trench, filling a second dielectric layer in the trench and the opening, and finally removing the hard mask layer and the first dielectric layer. The manufacturing method of a shallow trench isolation structure can not damage the lateral wall and the bottom of the trench when the hard mask layer is etched back.

Owner:SEMICON MFG INT (SHANGHAI) CORP

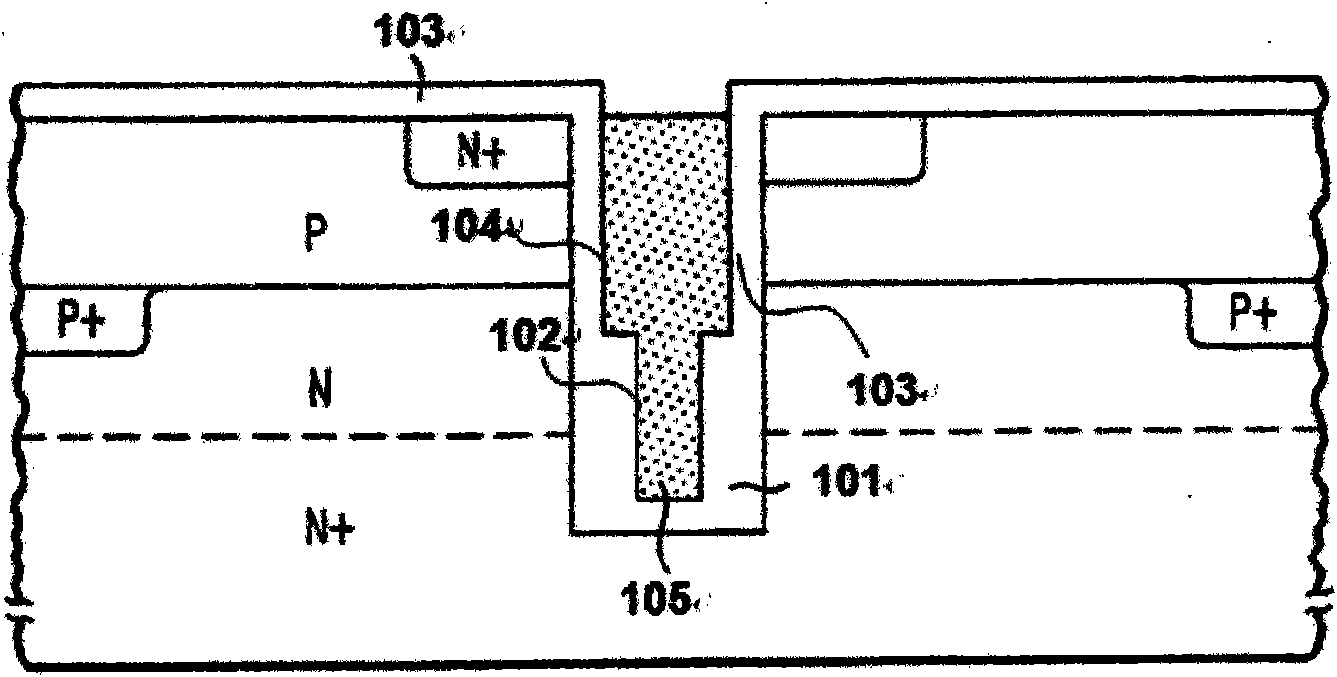

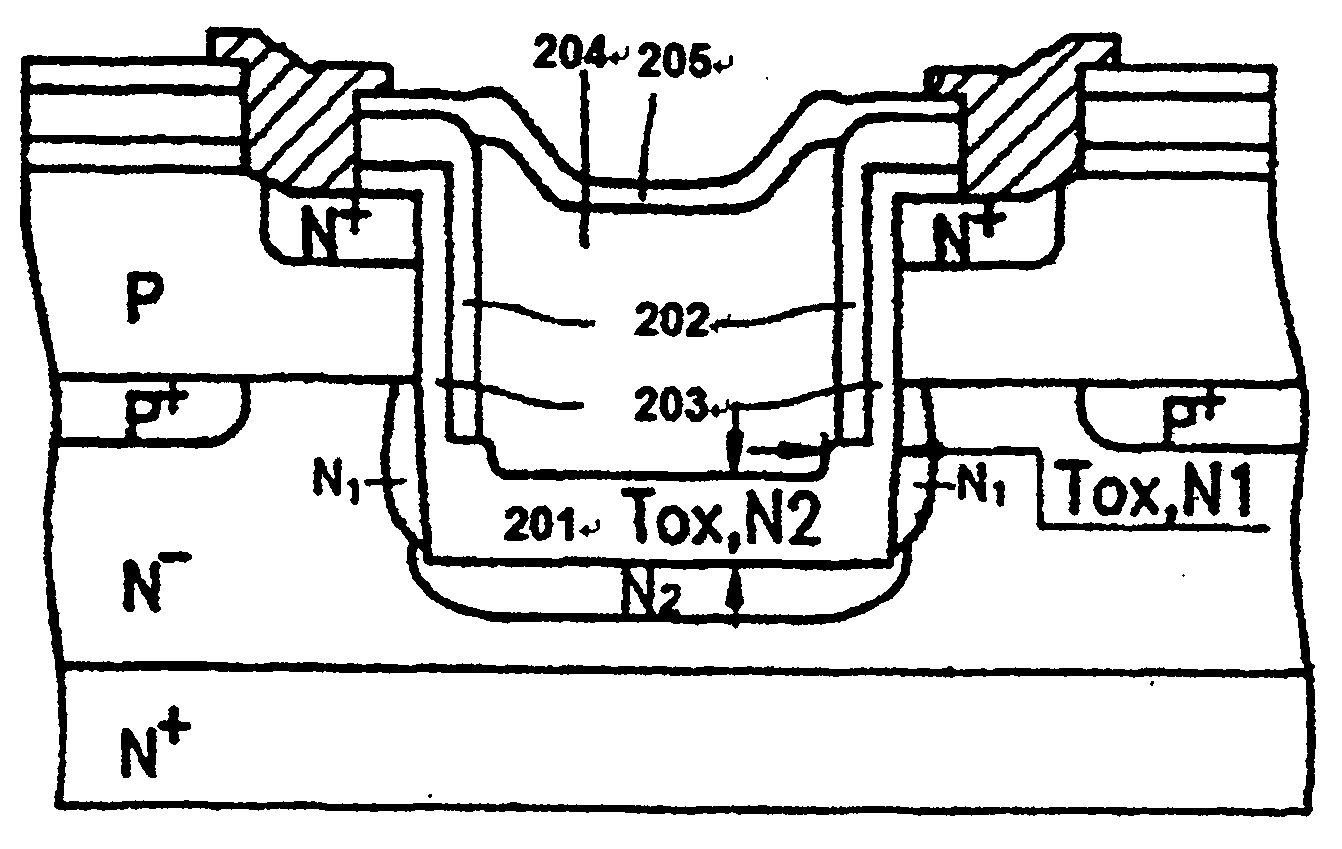

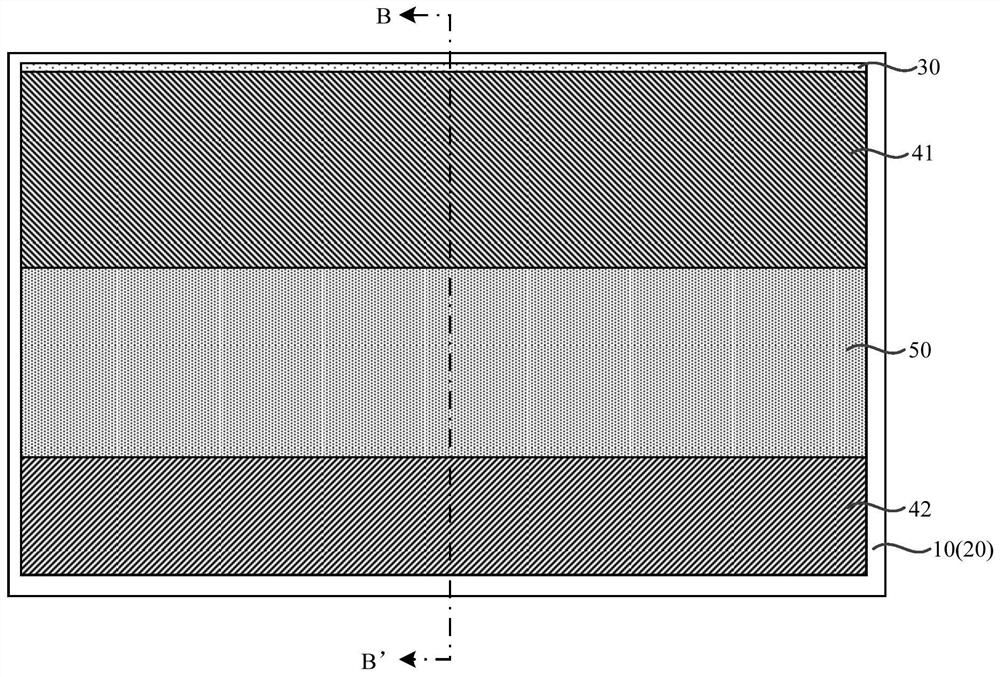

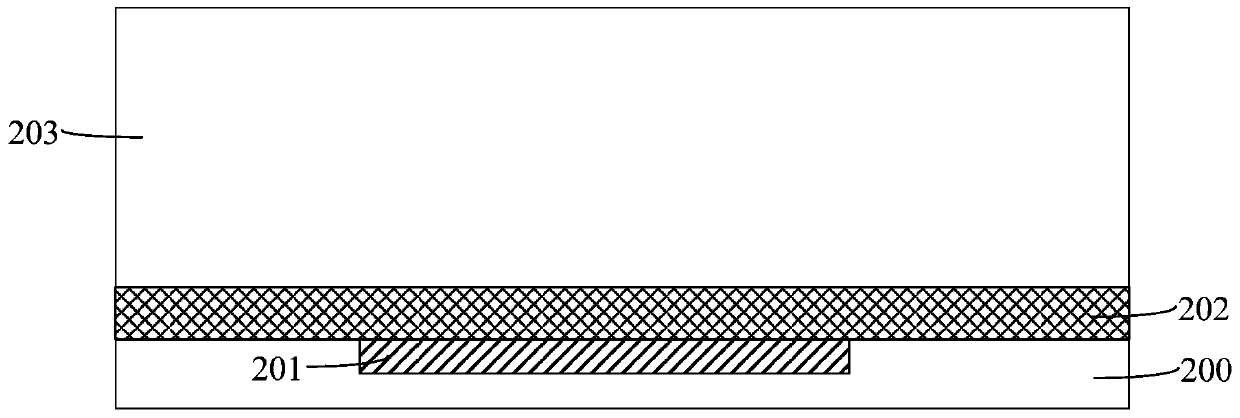

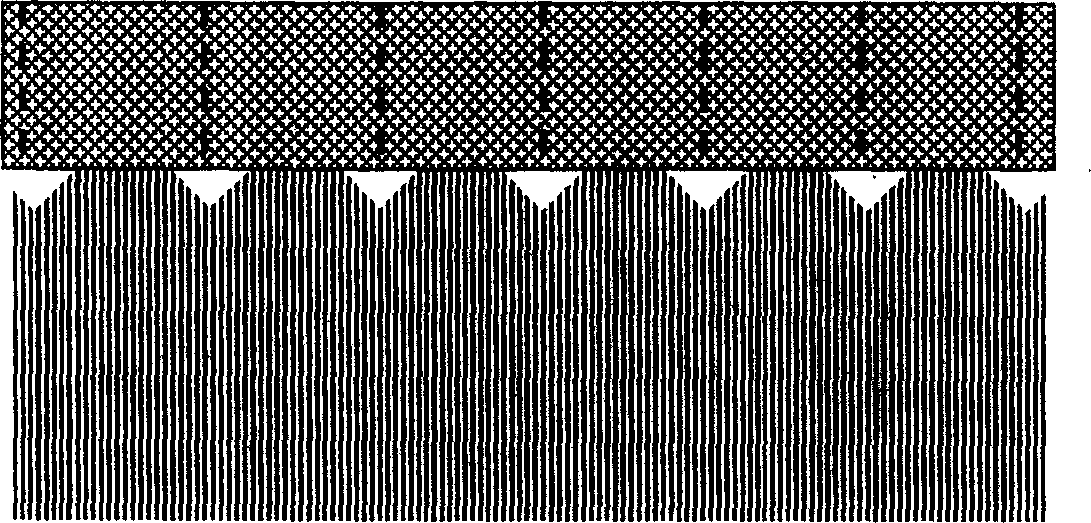

Trench structure for power device and manufacturing method thereof

InactiveCN102024848AQuality improvementImprove conductivitySemiconductor devicesSilicon oxideDry etching

The invention discloses a trench structure for a power device and a manufacturing method thereof. The trench structure has the characteristics that: a side wall is vertical and provided with a thin silicon oxide film or a side wall is provided with a slight slope (theta=80-90 degrees) and a thin silicon oxide film; the bottom is smooth and is provided with a thick silicon oxide film; doped polycrystals are filled without gaps; boundary defects are eliminated; and the surface of a wafer at a trench position does not have any step or has a small step. The manufacturing method for the trench structure comprises the following steps of: forming the trench through dry etching; removing surface defects of the trench by using an oxidation process; forming the side wall of the trench by using a silicon nitride film; and forming a silicon oxide film with a thick bottom and a thin side wall in the trench through selective oxidation, wet etching and reoxidation; filling a good-conductivity polysilicon film without gaps; and removing the excessive polysilicon film outside the trench through etching or a chemically mechanical polishing process to form the trench structure required by a trench type power device. The manufacturing method is simple and stable in process, and is easy to implement; and the manufactured device has the advantages of small area, good electrical characteristics and the like.

Owner:TIANJIN HUANXIN TECH DEV

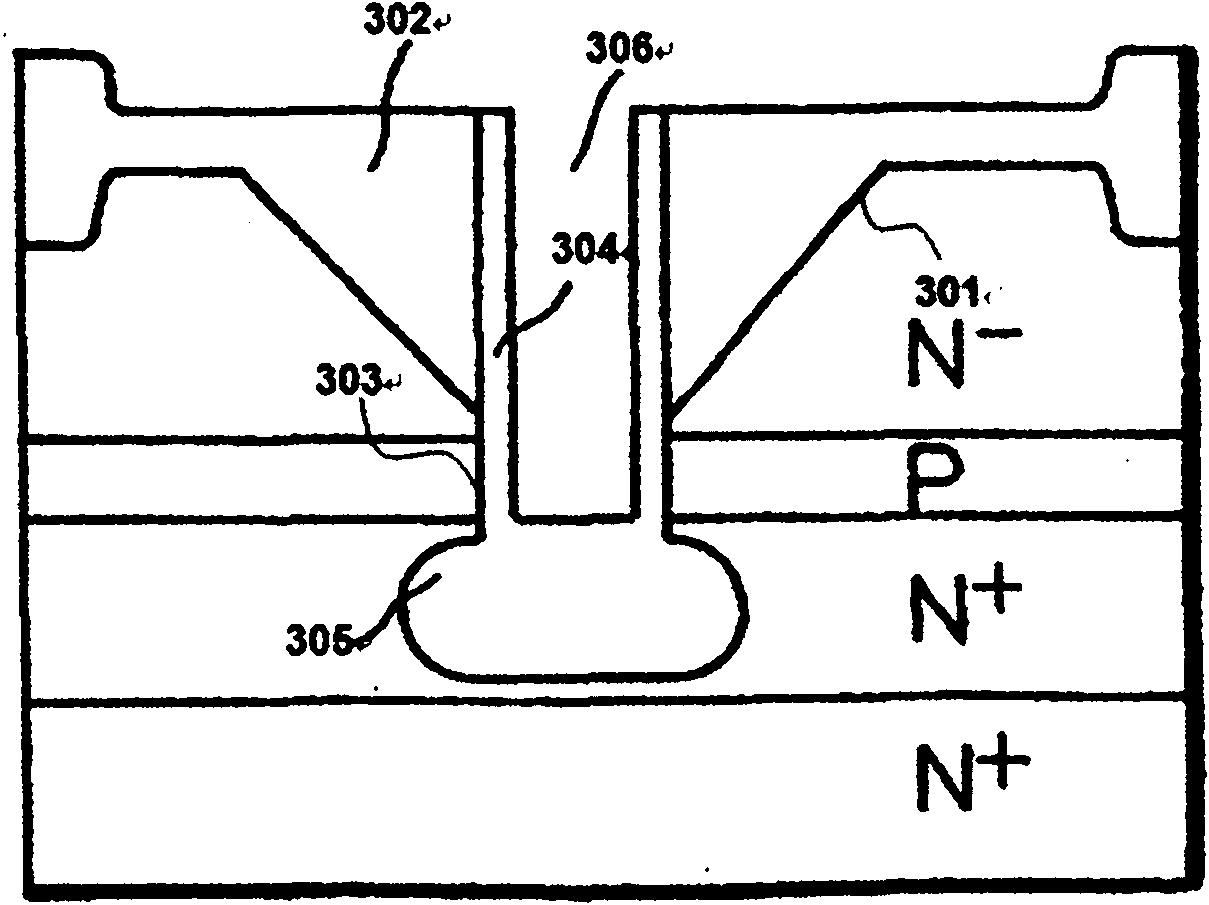

Semiconductor device and method for manufacturing the same

ActiveCN101996874AReduce contact resistanceReduce areaTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device fabrication

The invention discloses a semiconductor device and a method for manufacturing the same. The method for manufacturing a semiconductor device includes the steps of: (a) forming a gate electrode on a substrate, forming source / drain regions and a channel forming region in the substrate, and forming on the source / drain regions a first interlayer insulating layer equal in height to the gate electrode; (b) forming in the first interlayer insulating layer groove-shaped first contact portions connected to the source / drain regions; (c) forming a second interlayer insulating layer on a whole surface; (d) forming hole-shaped second contact portions in portions of the second interlayer insulating layer on the first contact portion; and (e) forming on the second interlayer insulating layer wires connected to the second contact portions.

Owner:SONY GRP CORP

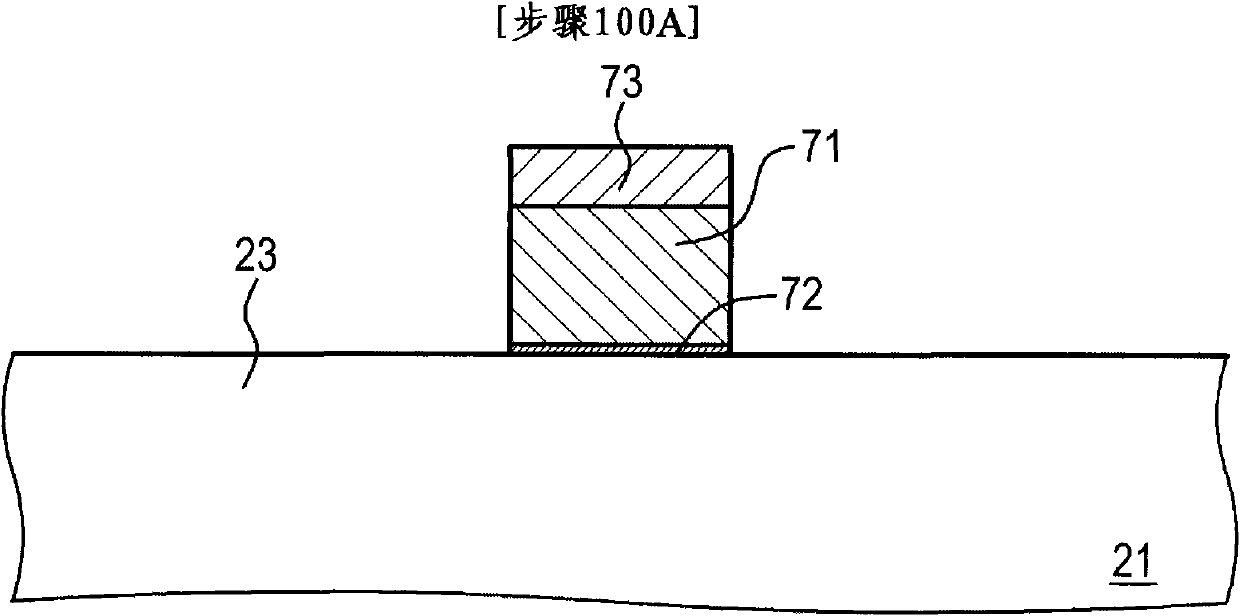

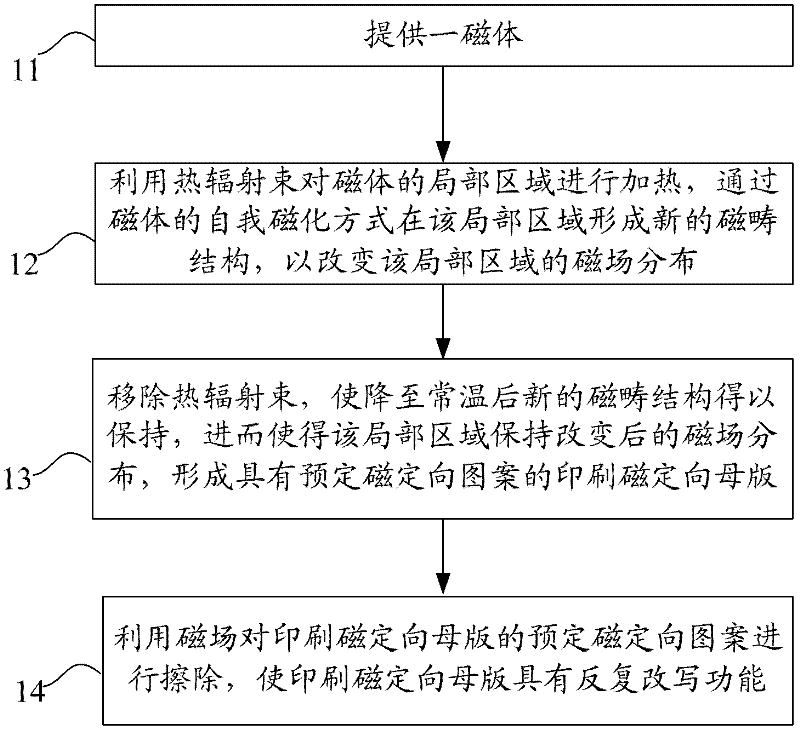

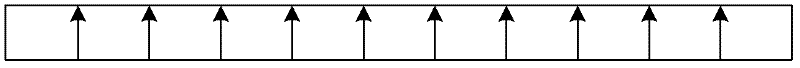

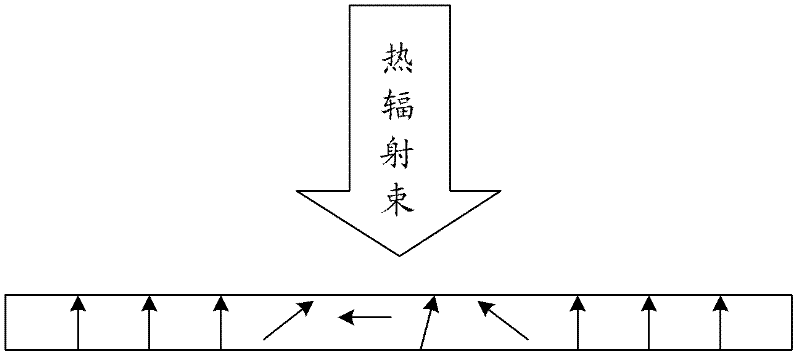

Manufacturing method and manufacturing device of printing magnetic orientation mother set and magnetic pigment presswork

ActiveCN102642419ASimplify the manufacturing processZero processing lossMagnetic bodiesDuplicating/marking methodsEngineeringThermal radiation

The invention provides a manufacturing method and a manufacturing device of a printing magnetic orientation mother set and a magnetic pigment presswork. The manufacturing method of the printing magnetic orientation mother set comprises the following steps of: providing a magnetic body; utilizing a thermal radiation beam to heat a local area of the magnetic body, and forming a new domain structure in the local area through a self-magnetization manner of the magnetic body so as to change magnetic-field distribution of the local area; and removing the thermal radiation beam, so that the new domain structure reduced to be at normal temperature is kept, and further the changed magnetic-field distribution is kept in the local area so as to form the printing magnetic orientation mother set with preset magnetic orientation patterns. Through the method, the magnetic-field distribution is changed by utilizing thermal disturbance generated by the thermal radiation beam in the local area of the magnetic body, and the printing magnetic orientation mother set with the preset magnetic orientation patterns is further formed, so that the manufacturing process of the printing magnetic orientation mother set can be simplified, and abundant pattern information can be carried.

Owner:HUIZHOU FORYOU OPTICAL TECH

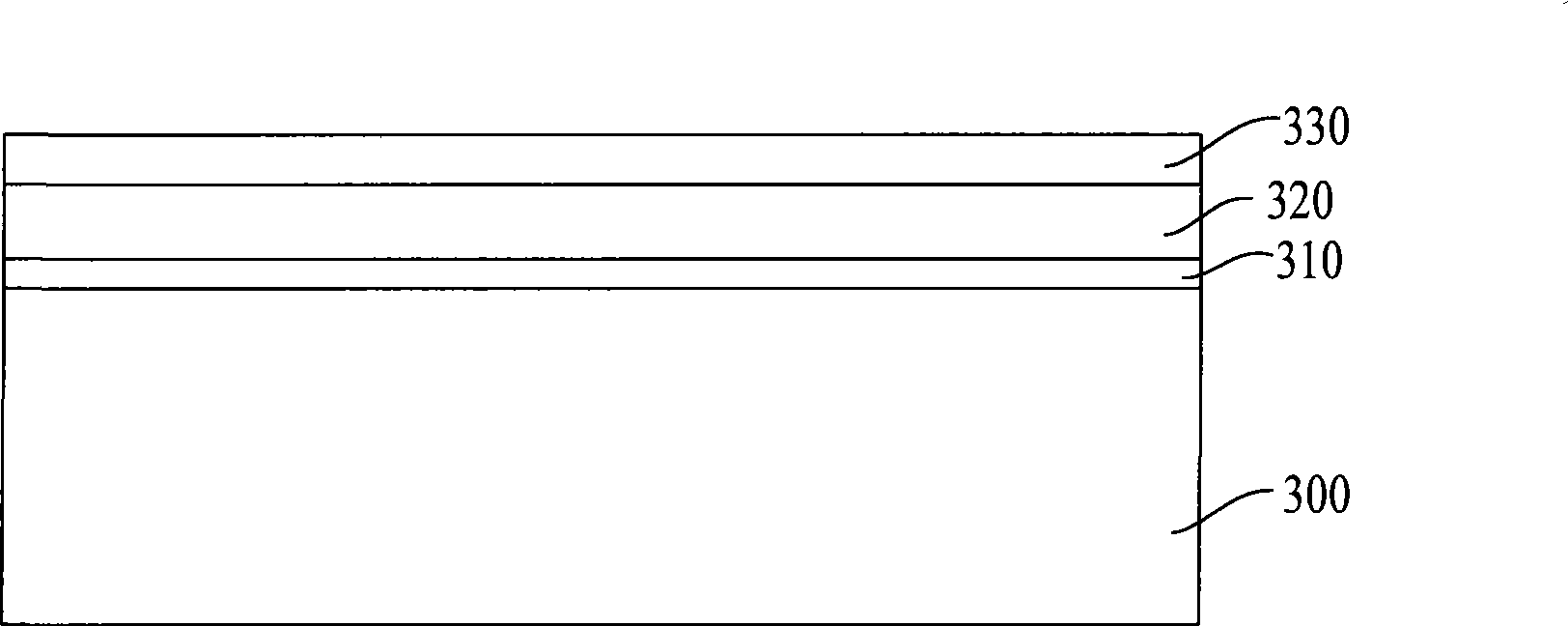

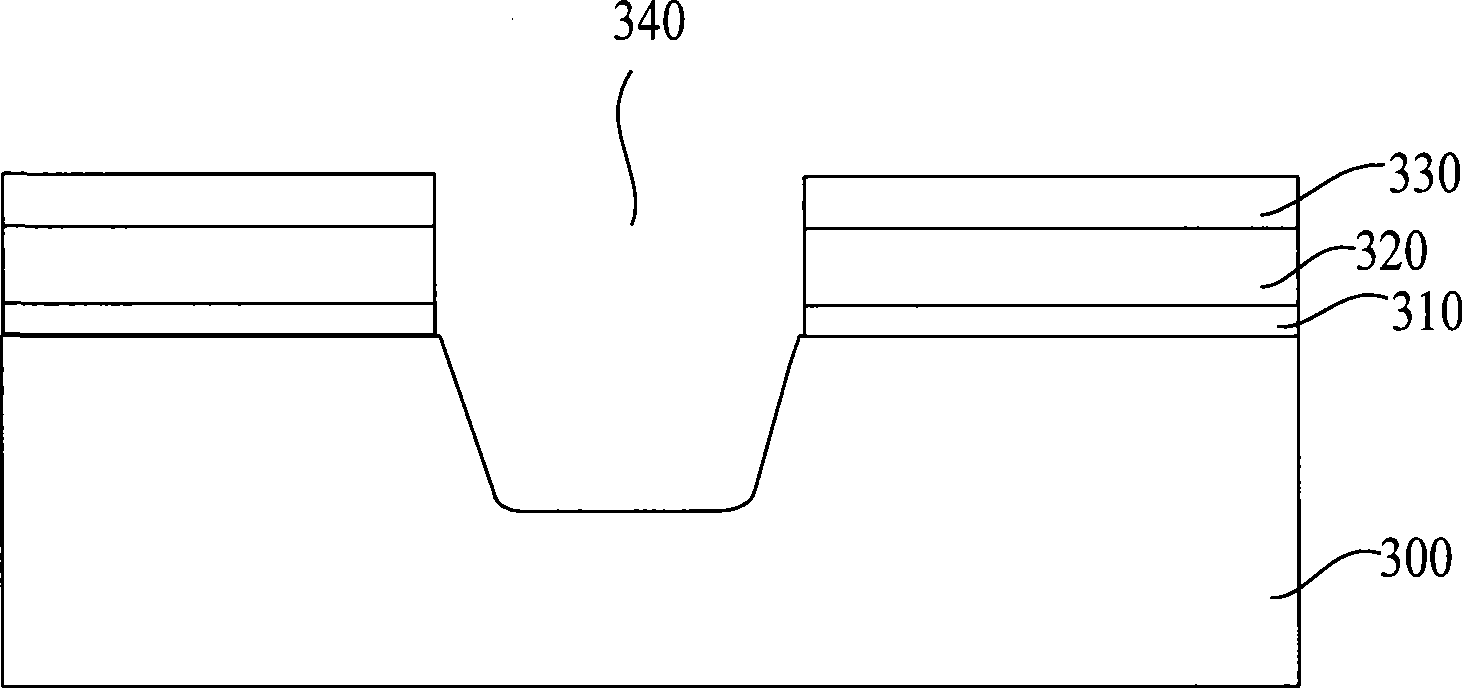

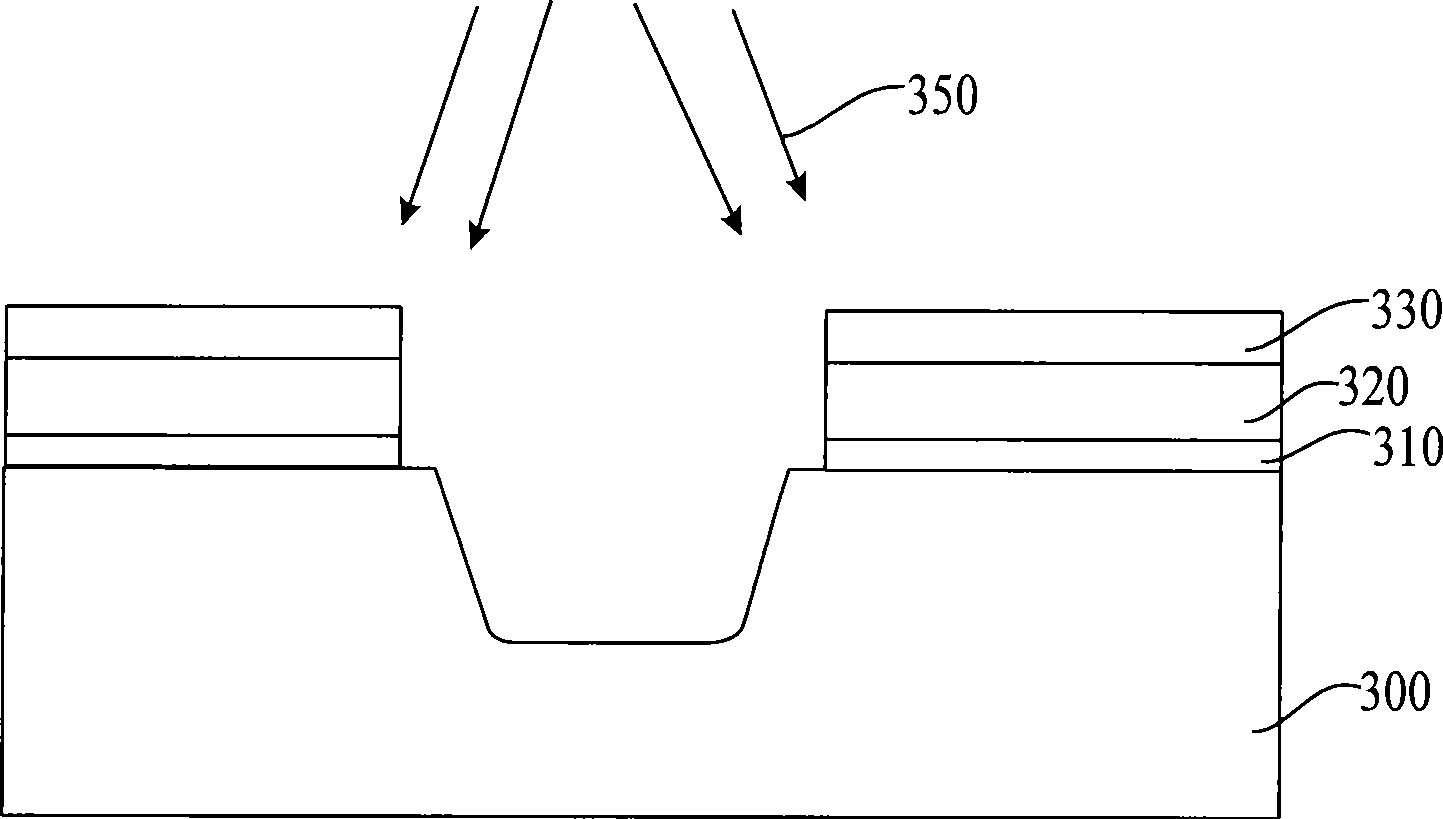

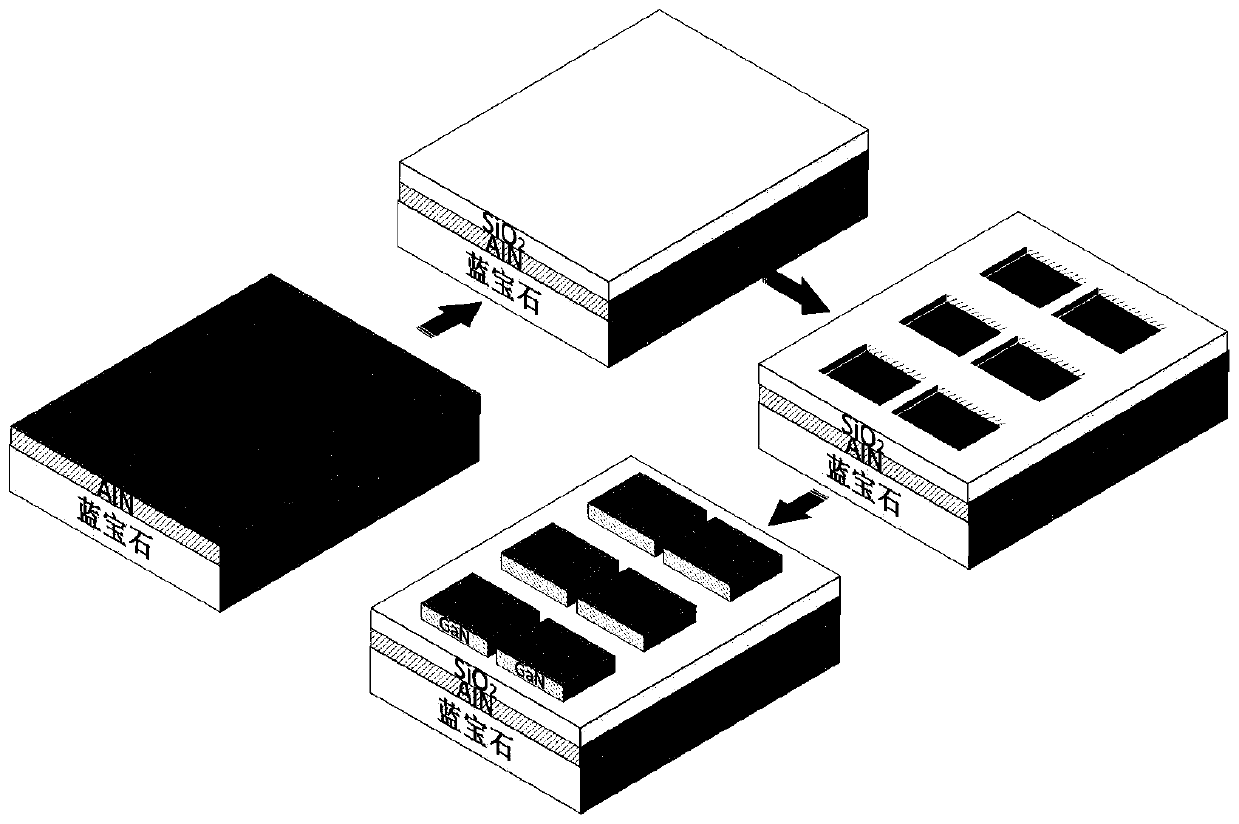

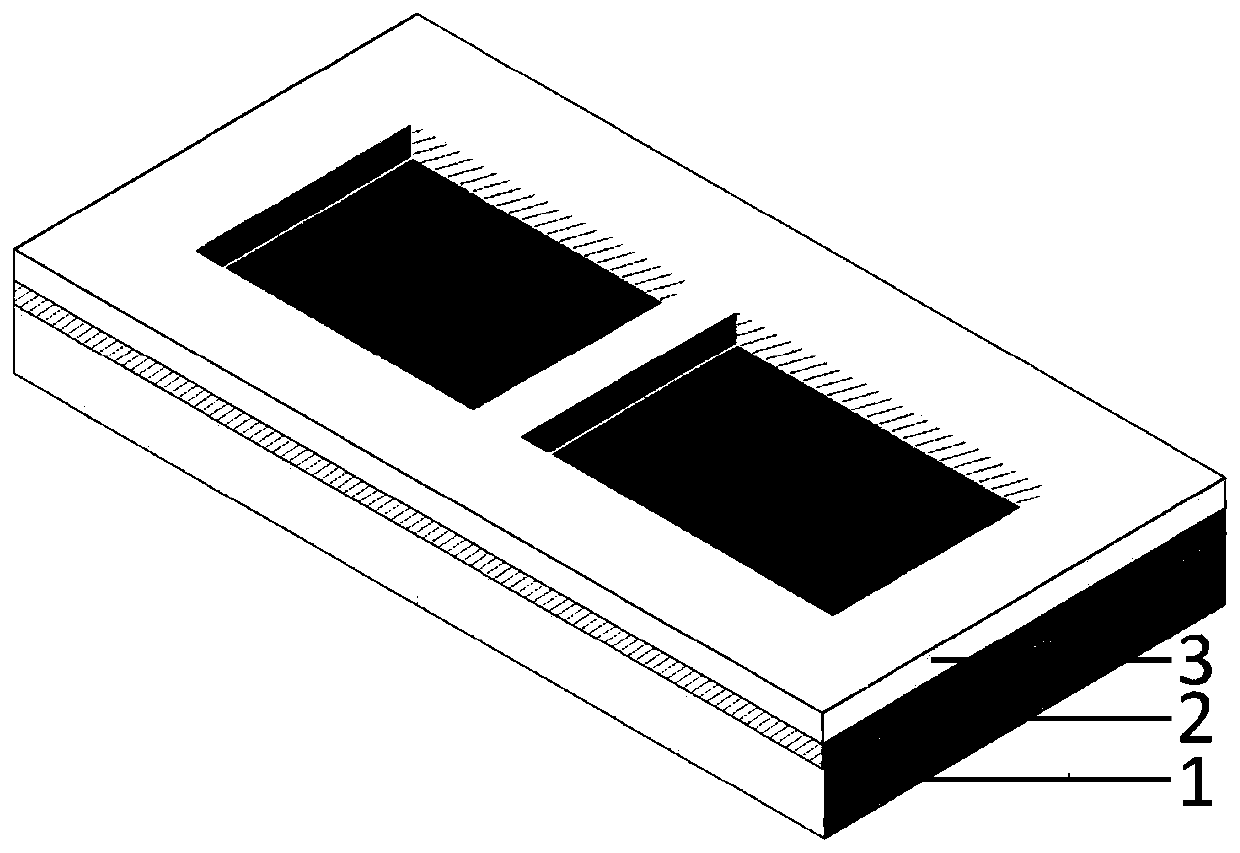

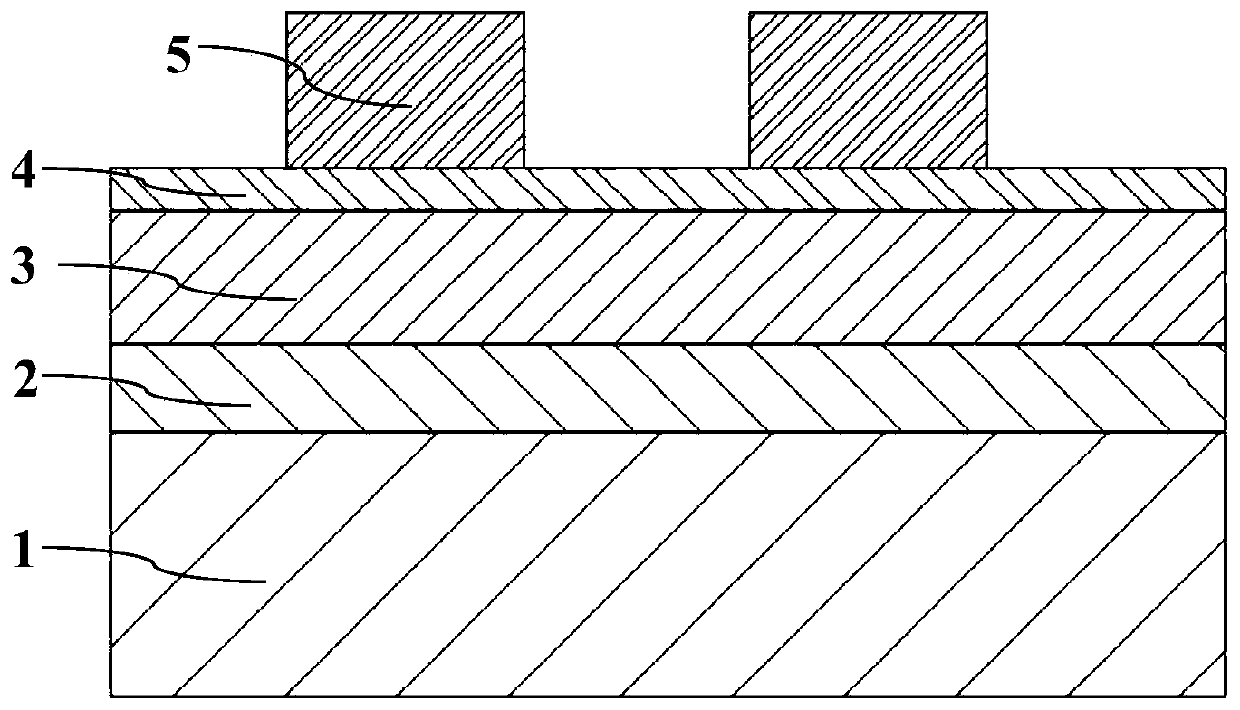

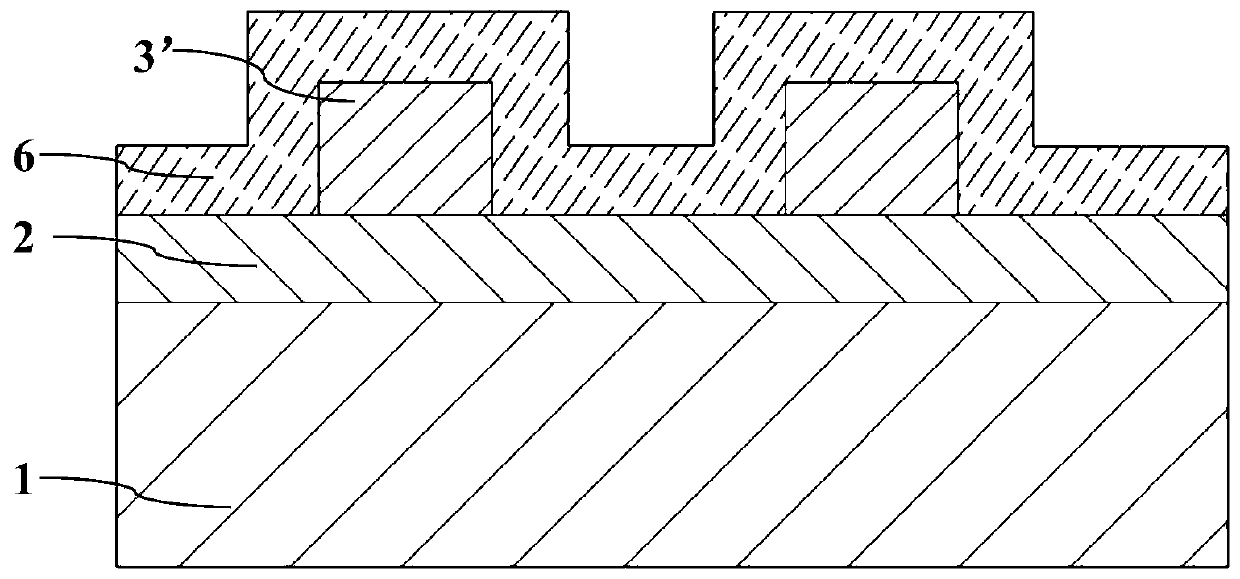

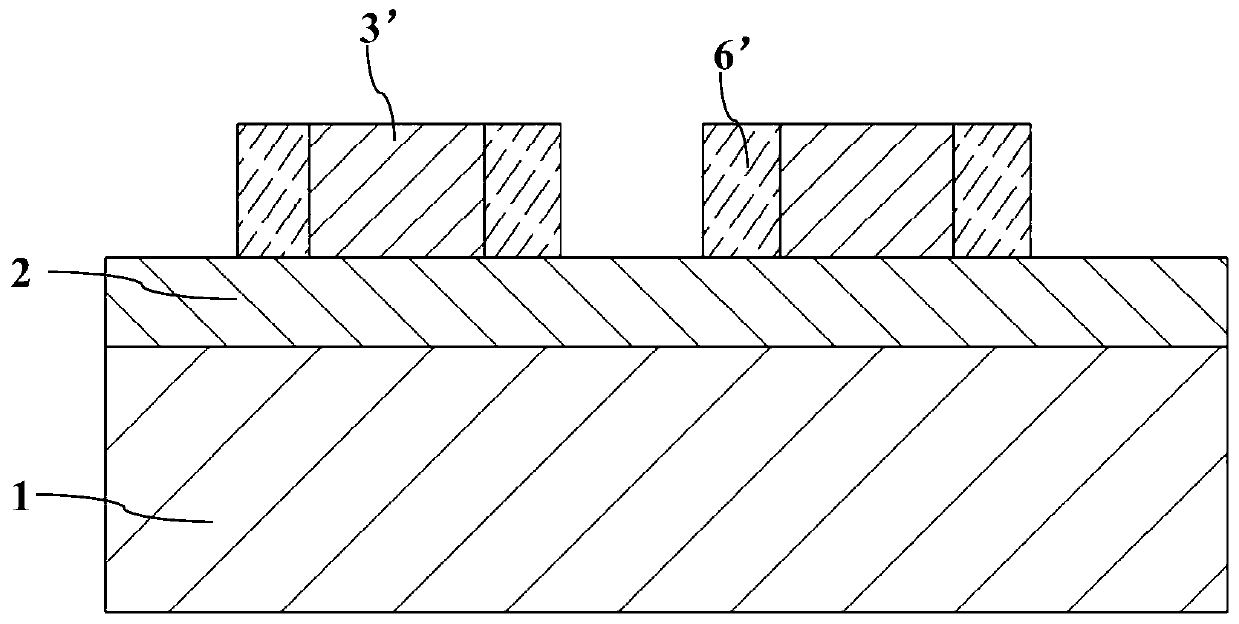

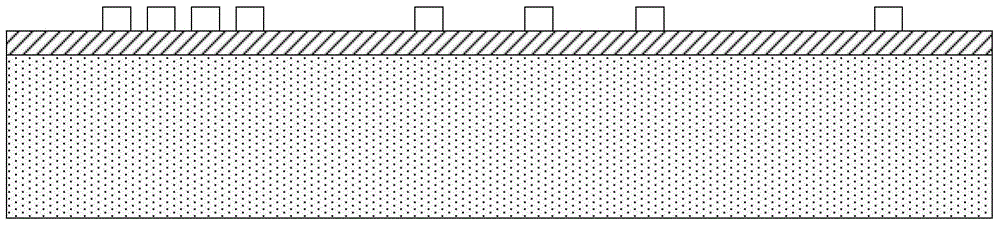

Method for growing patterned GaN on sapphire template and GaN epitaxial wafer

InactiveCN110783177AReduce performanceSmooth edgesSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectric layerSemiconductor

The invention relates to the technical field of semiconductor epitaxial growth and device technology, and provides a method for growing patterned GaN on a sapphire template and a GaN epitaxial wafer.Firstly an AlN nucleating layer and a SiO2 dielectric layer are sequentially grown on the surface of the sapphire substrate, then the SiO2 dielectric layer is etched according to predetermined patterns, the AlN nucleating layer in the etched region is exposed to form a growth window region and the secondary epitaxial growth of GaN is performed in the growth window region so as to form a patternedGaN layer. The SiO2 dielectric layer is used as a mask in the GaN epitaxial growth process and finally the GaN material is mainly nucleated and grown at the growth window position to form the GaN withthe required specific pattern. The method does not need to etch the GaN layer, and the mesa and the side walls of the device obtained after patterned GaN growth are smooth and the edges are flat without etching damage, thus avoiding the degradation of device performance caused by the etching damage.

Owner:SUN YAT SEN UNIV

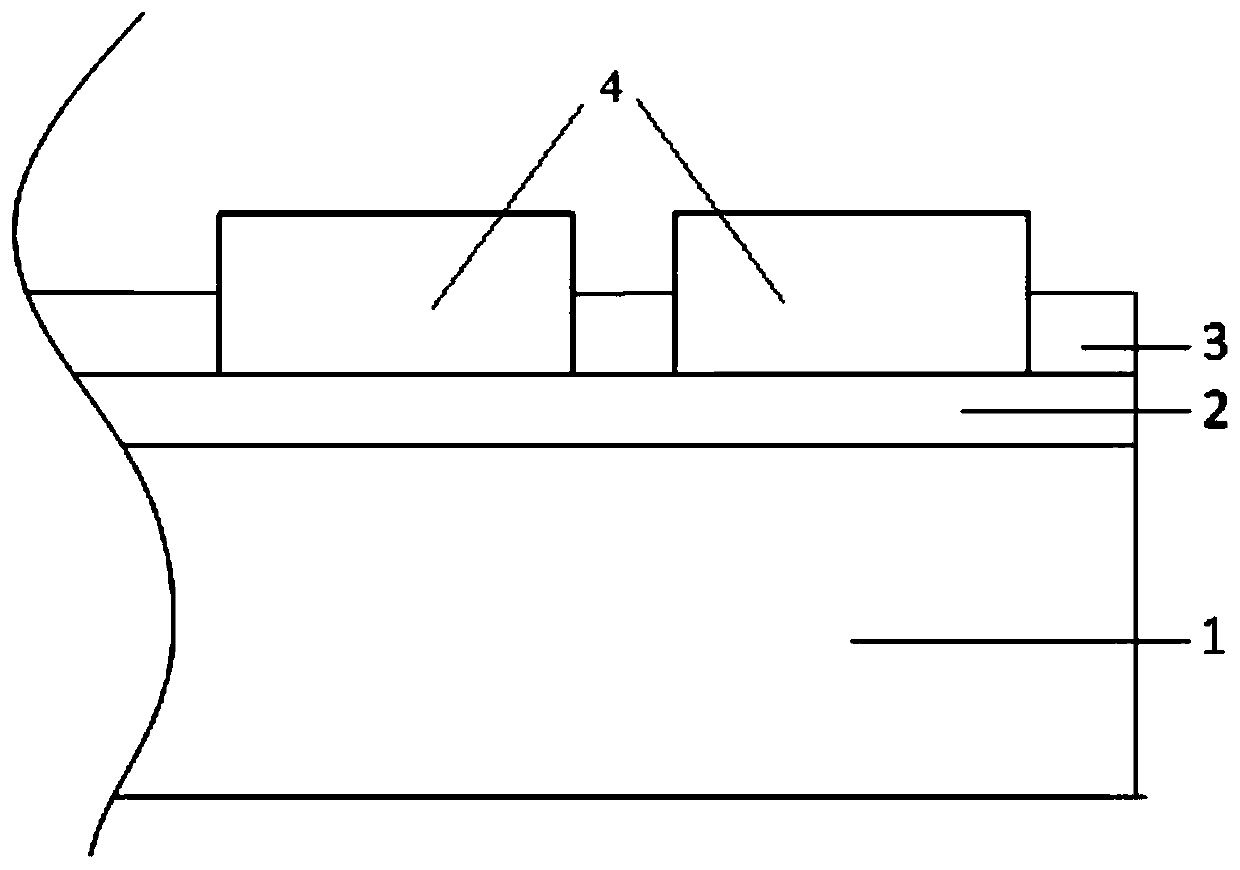

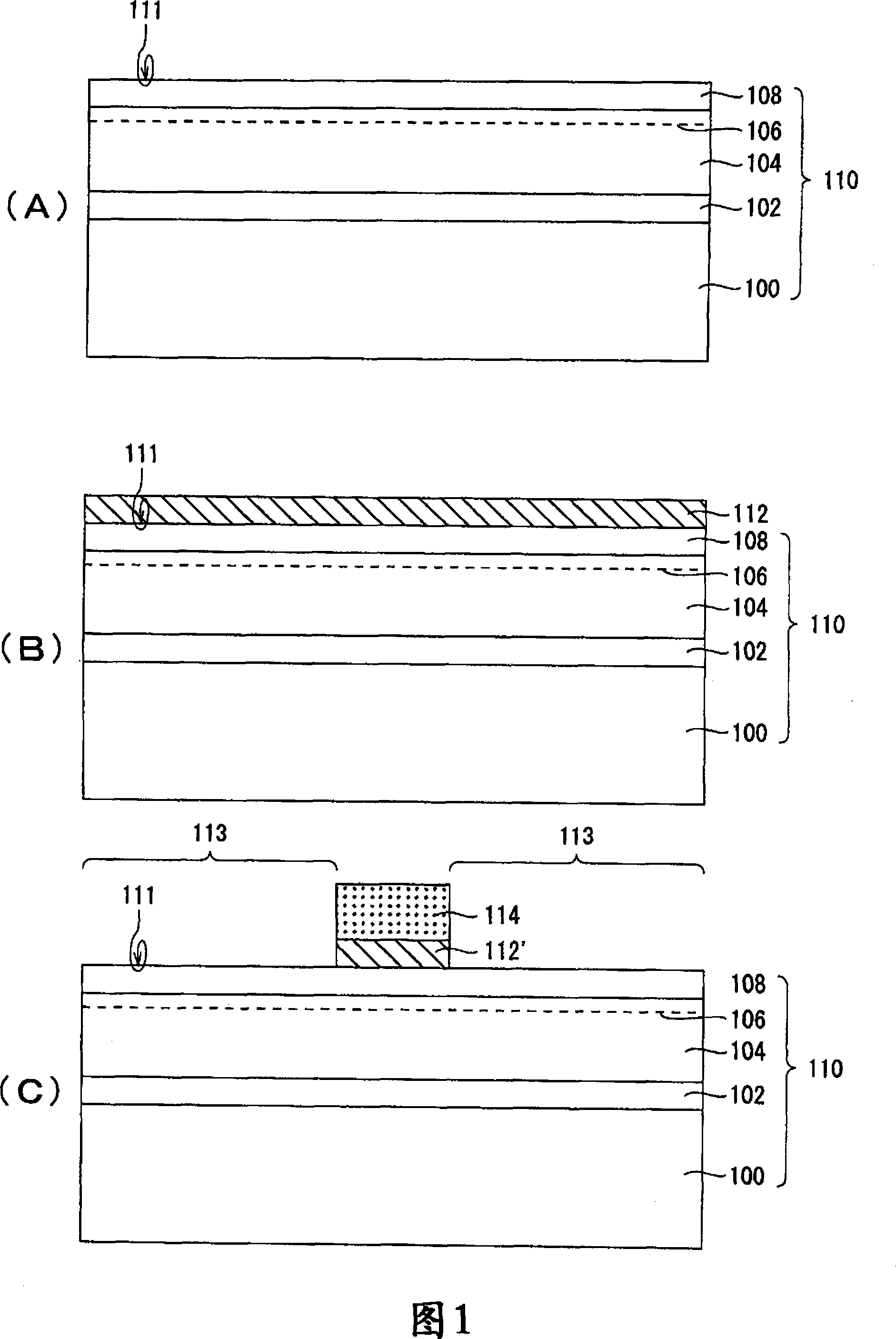

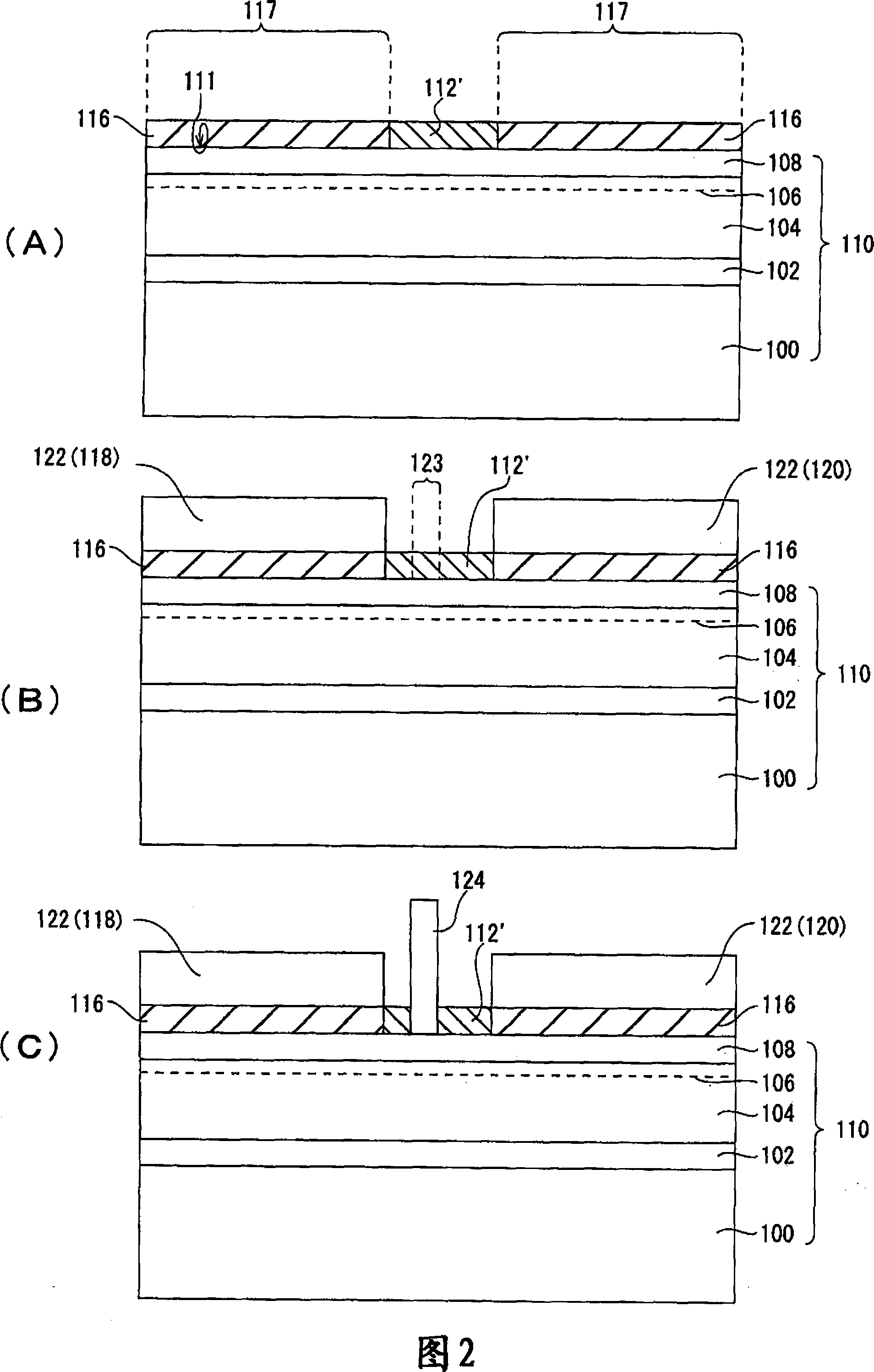

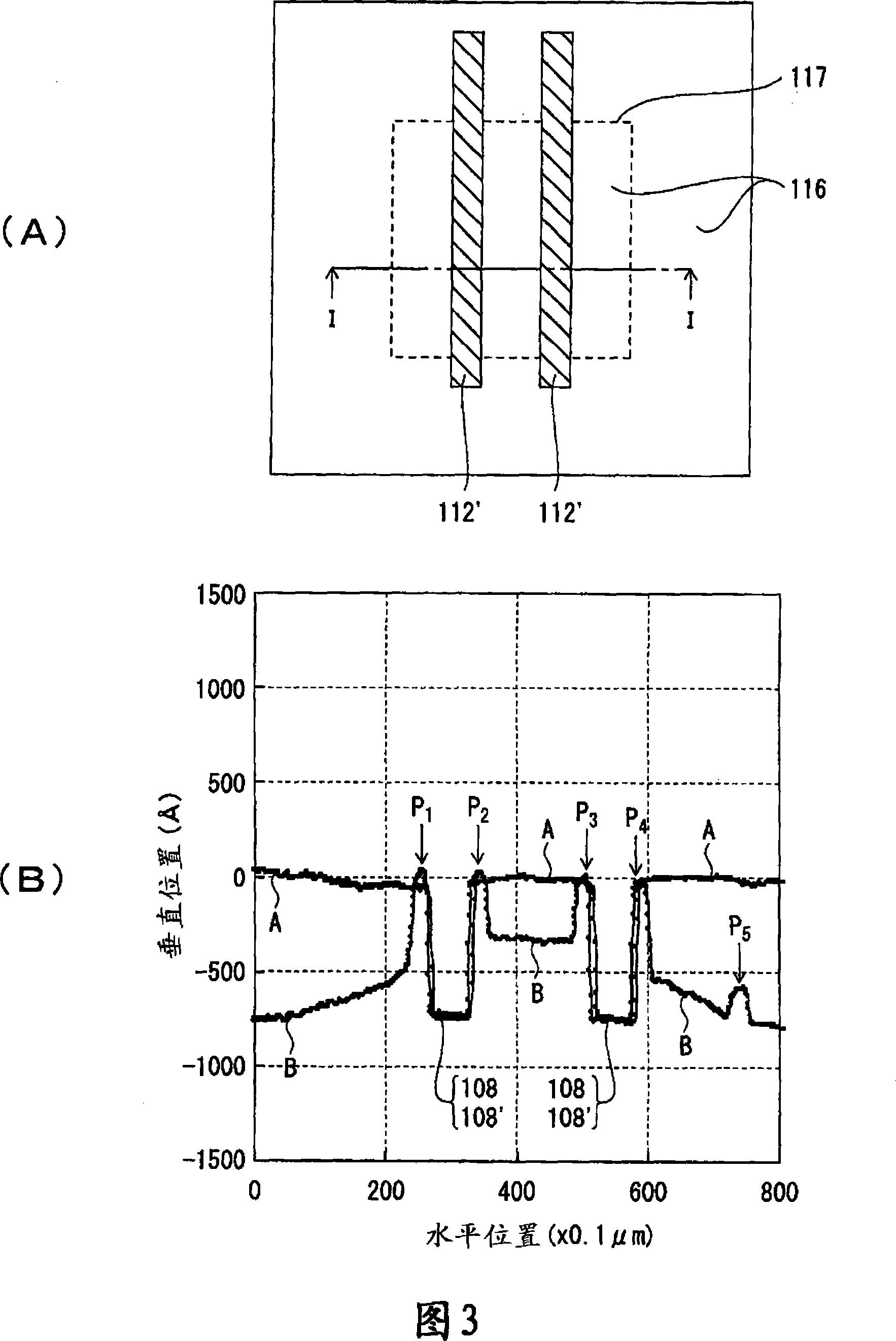

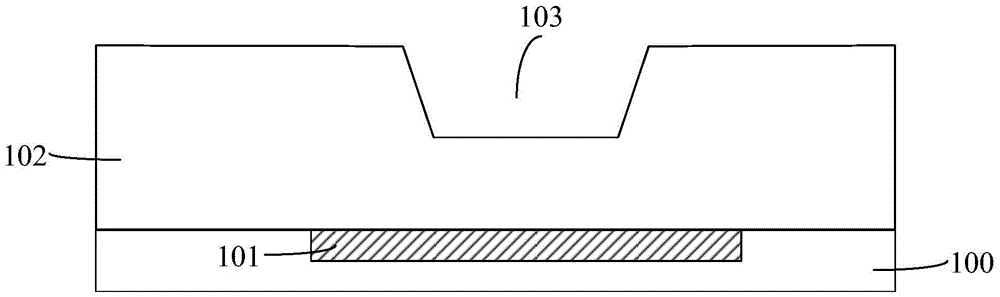

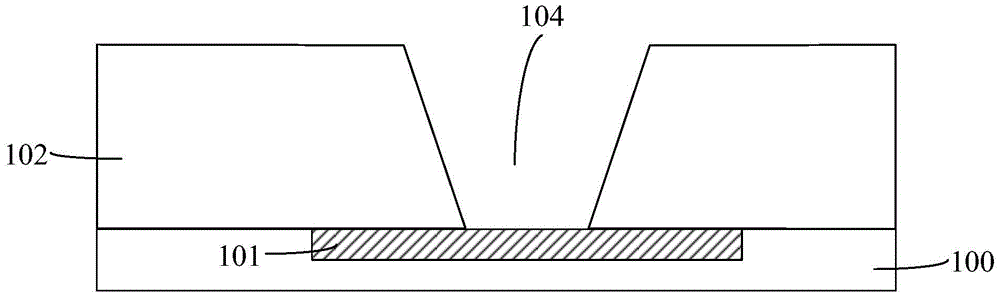

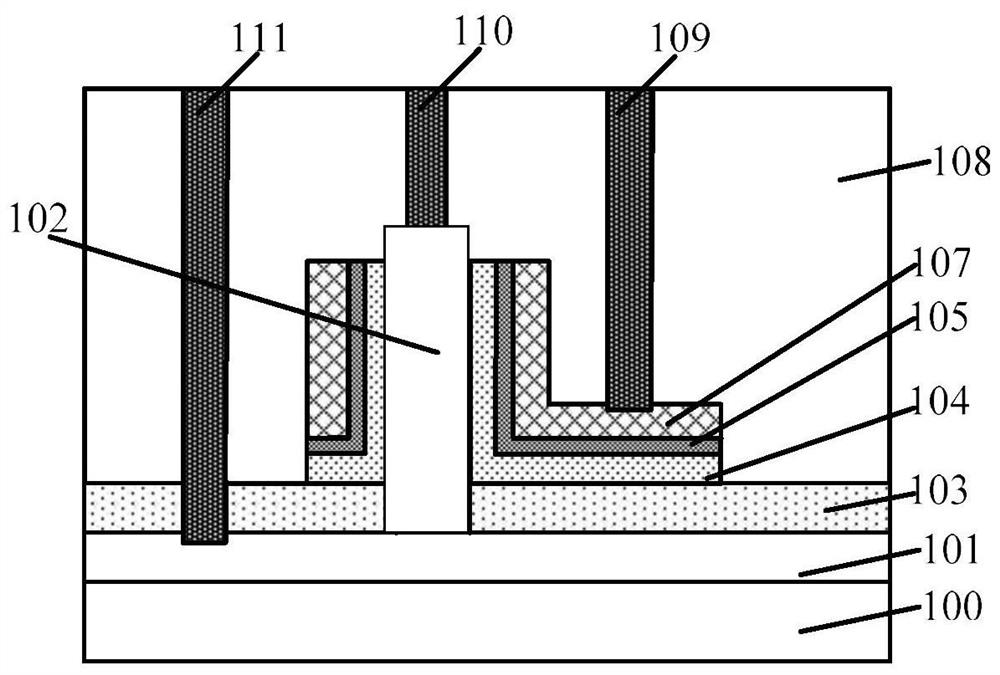

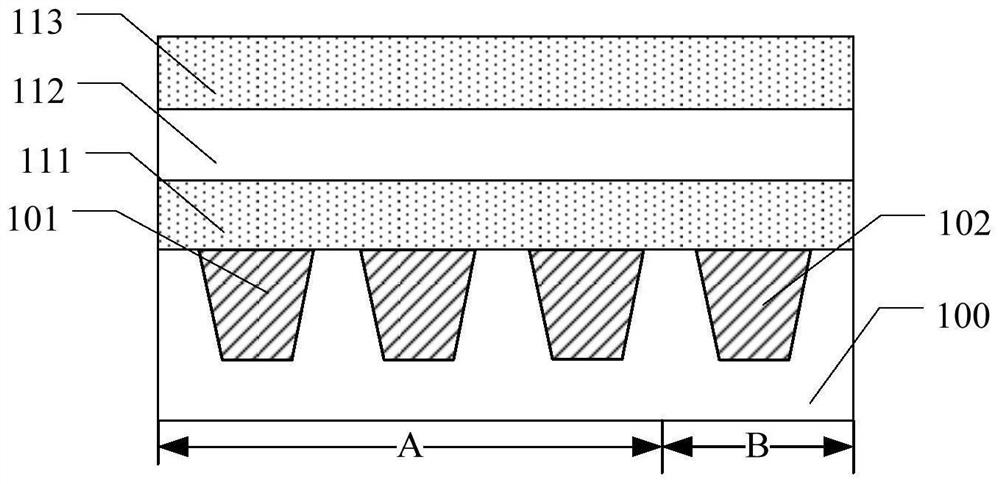

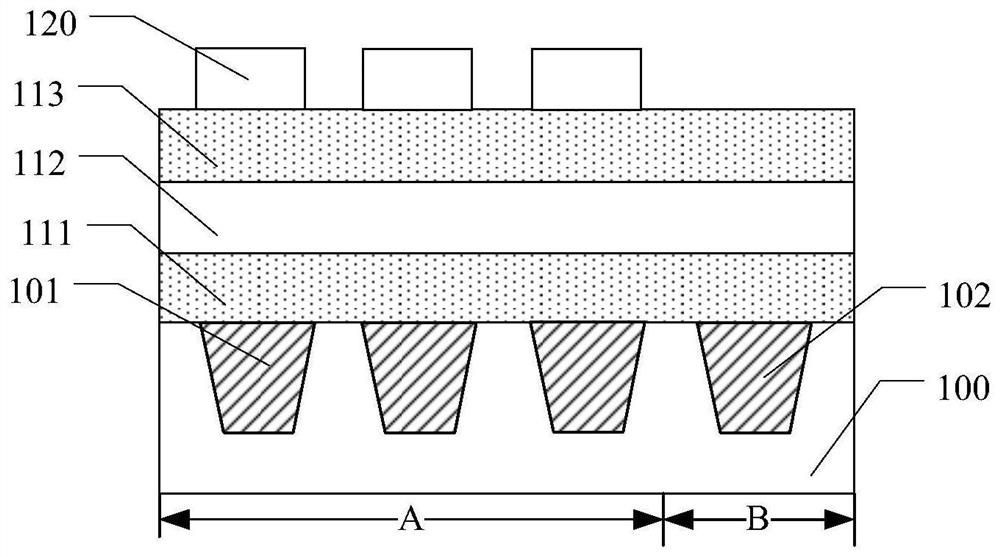

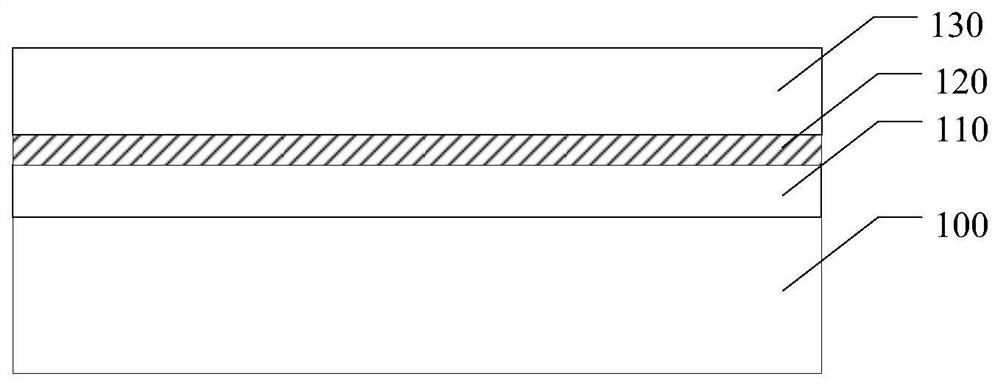

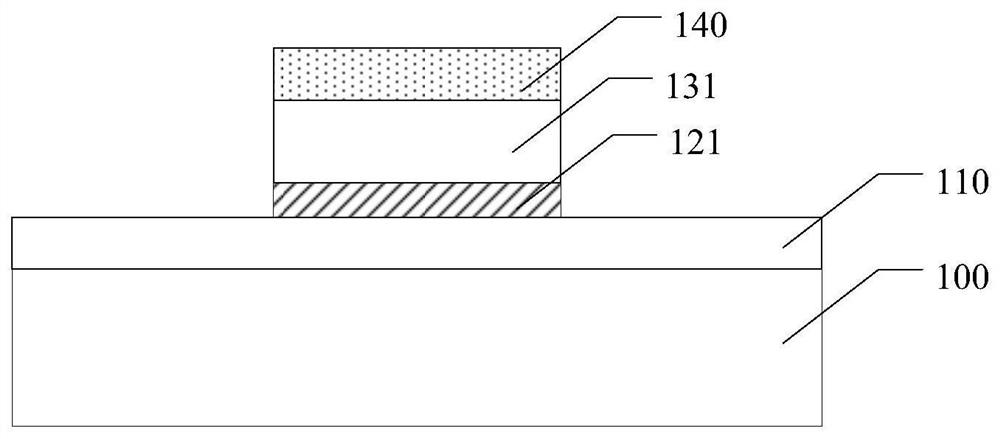

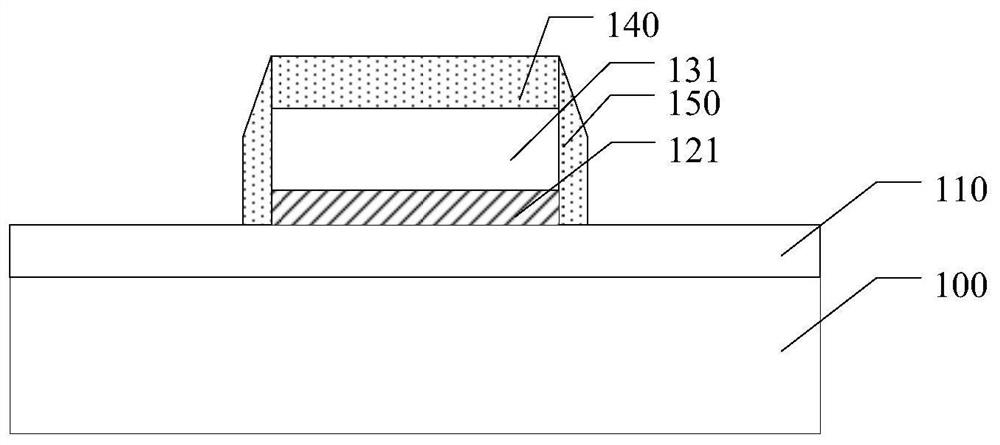

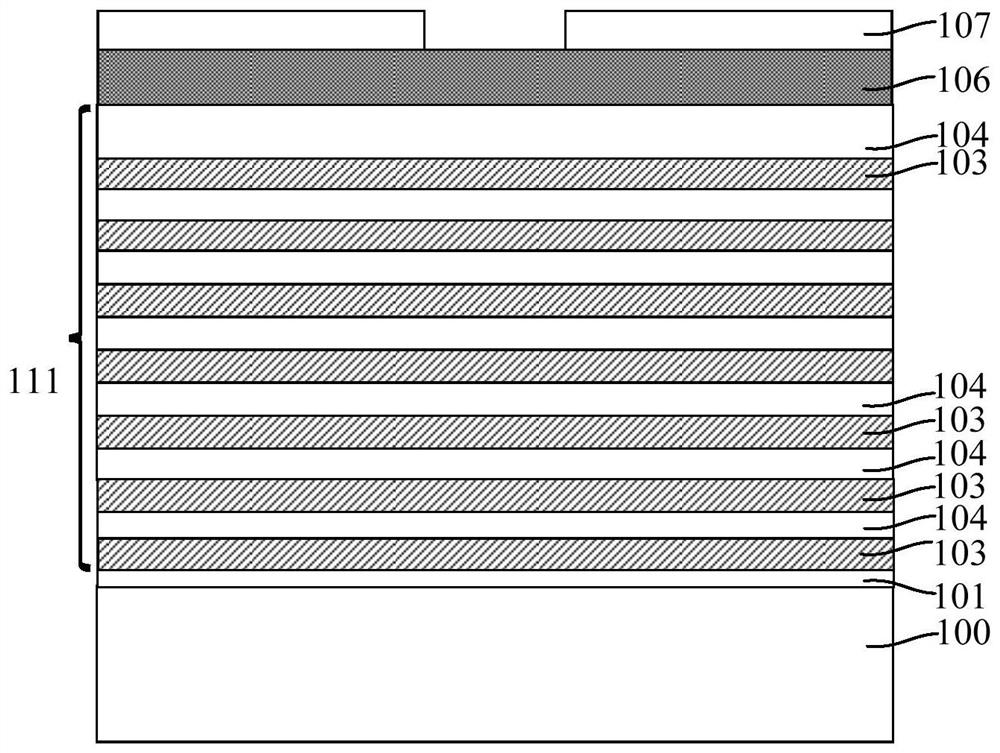

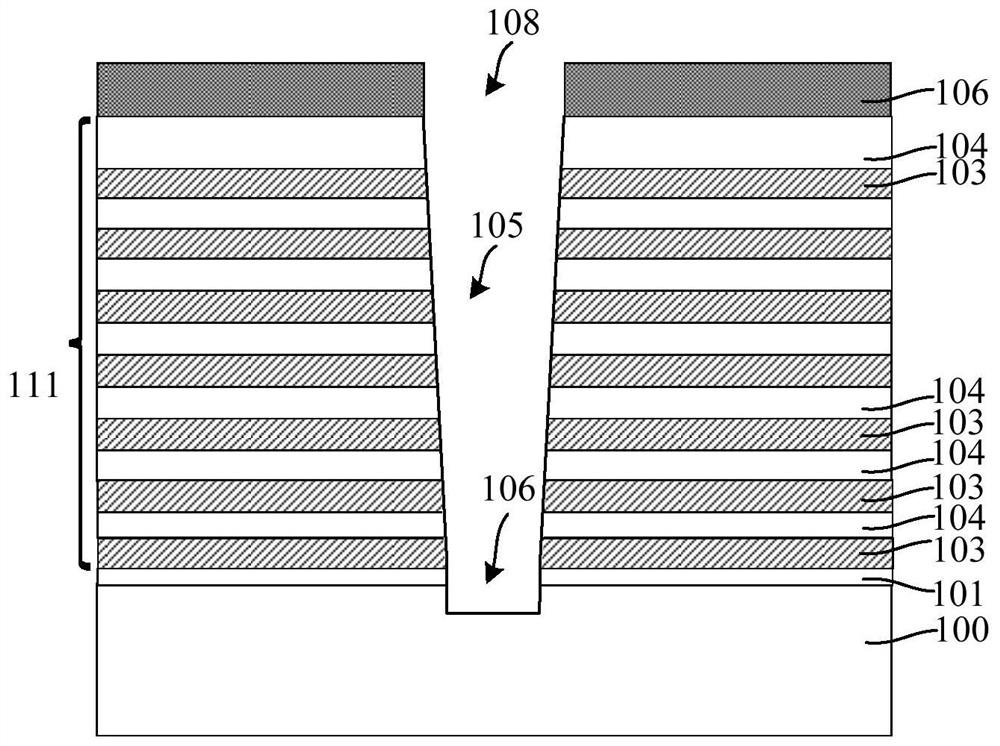

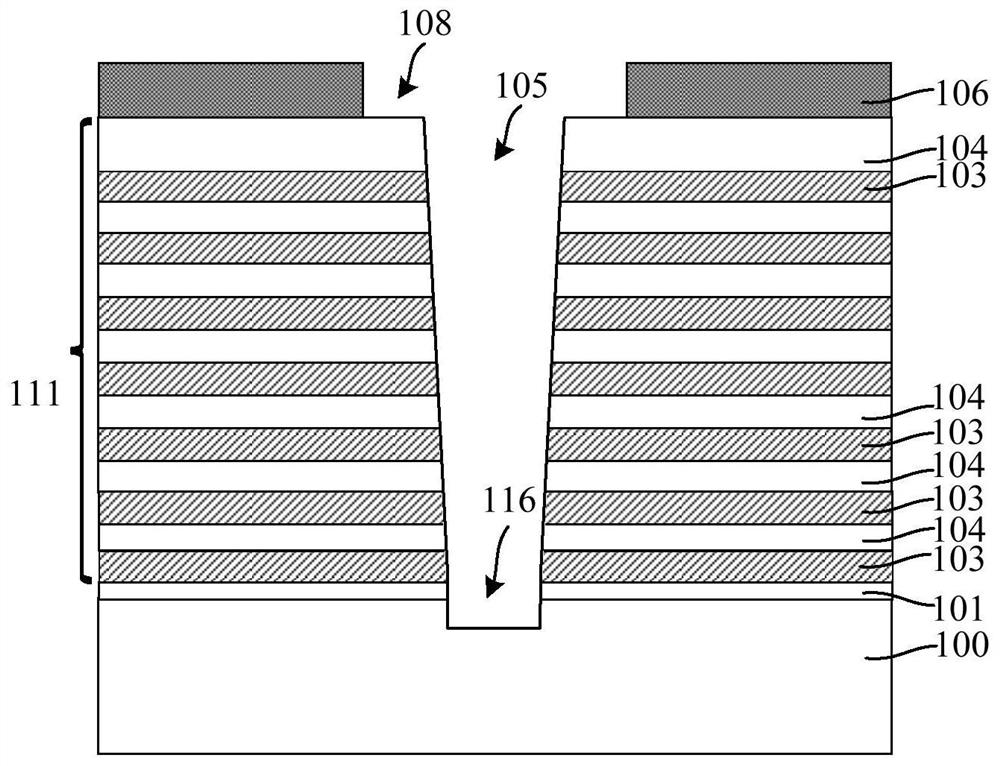

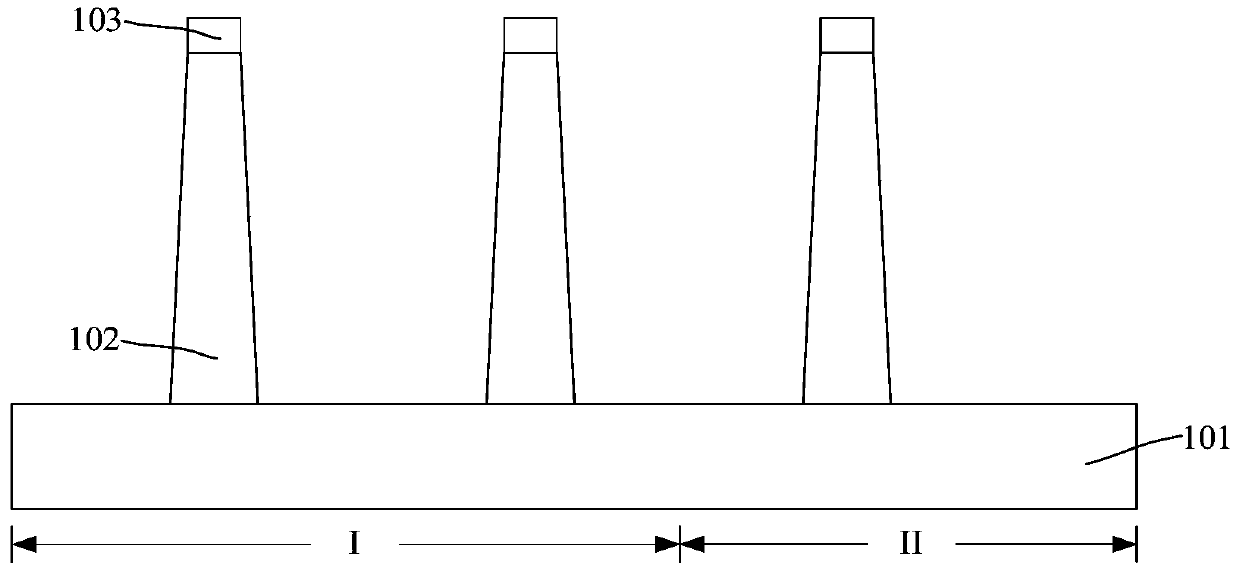

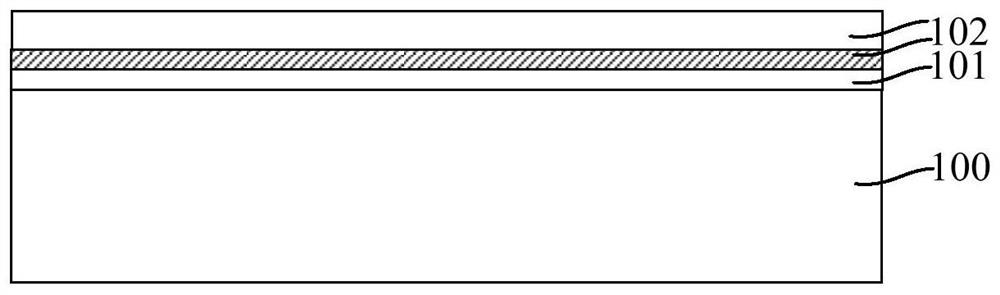

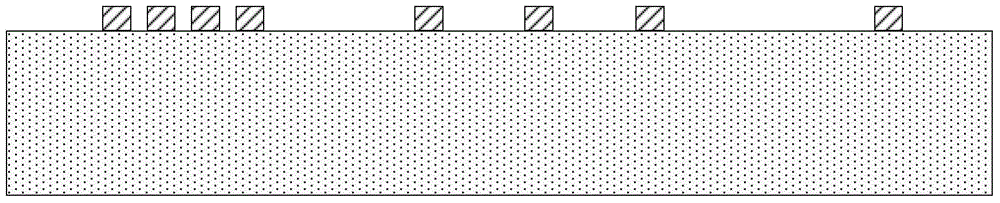

Method for manufacturing AlGaN/GaN-HEMT employing selective regrowth

InactiveCN101183647ANo shape problemNo etch damageSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorOhm

The invention relates to a manufacturing method using AlGaN / GaN-HEMT which can selectively revegetate. The method includes preparing a semiconductor main body (110) formed with a laminated structure, which cascades a cushion breaker (102) on a substrate (100), a UID-GaN layer on the cushion breaker, and a UID-AlGaN layer on the UID-GaN layer. The pattern of an insulating film (112) is formed on the first major face (111) of the surface of the semiconductor main body used as the UID-AlGaN layer in order to form a mask of an insulating film (112'). An etching process is not processed on the surface of the semiconductor main body,therefore an nSUP and / SUP-GaN layer selectively revegetates on the surface of the major face (111) of the semiconductor main body apart from the area of the insulating film. An ohm electrode is divided, a preconcerted area (117) is formed and the ohm electrode (122) is formed in the area of the selectively revegetated nSUP and / SUP-GaN layer. Then a preconcerted area (123) is formed and an opening is formed by dividing a gate electrode, and the gate electrode (124) is formed.

Owner:OKI ELECTRIC IND CO LTD

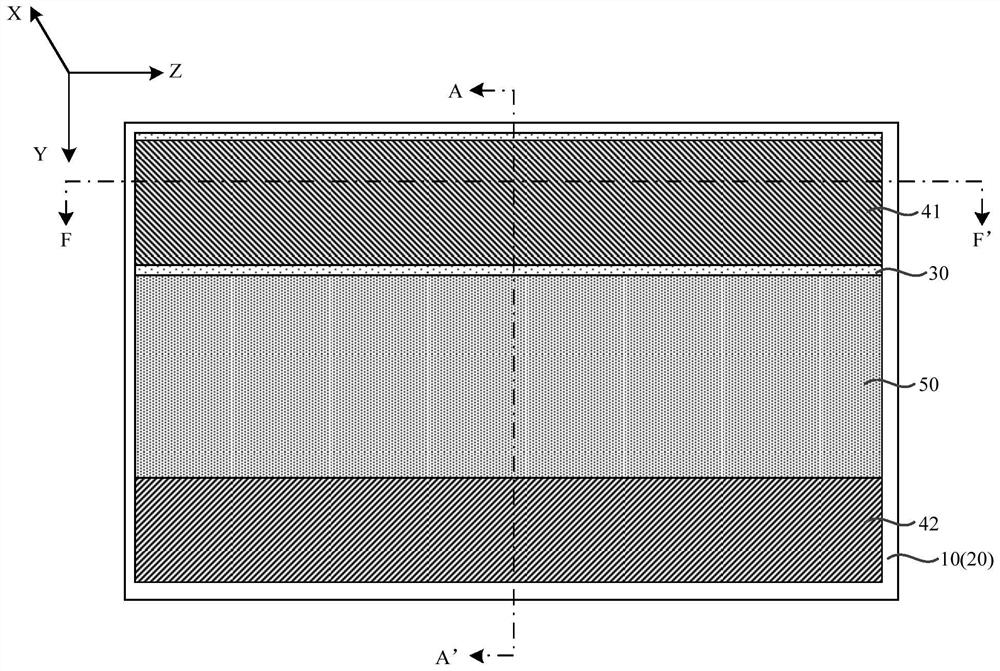

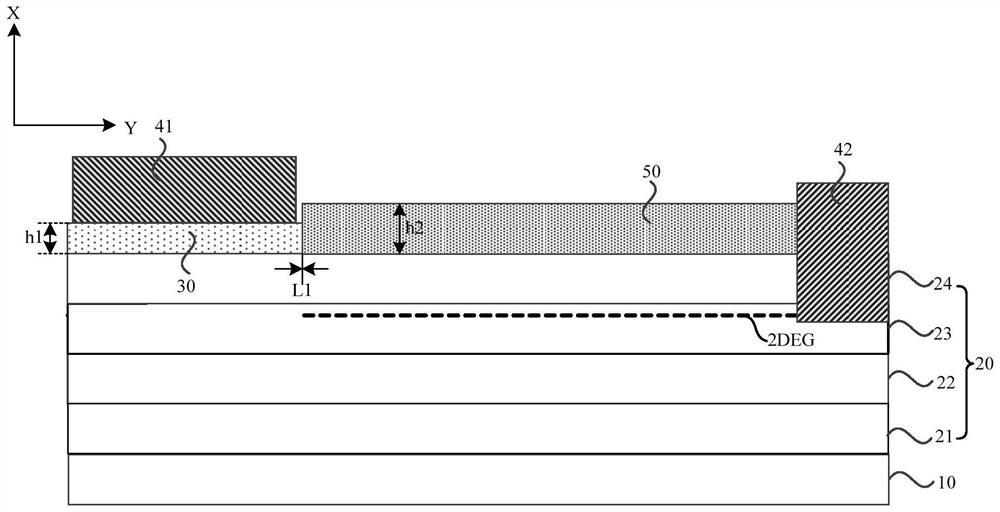

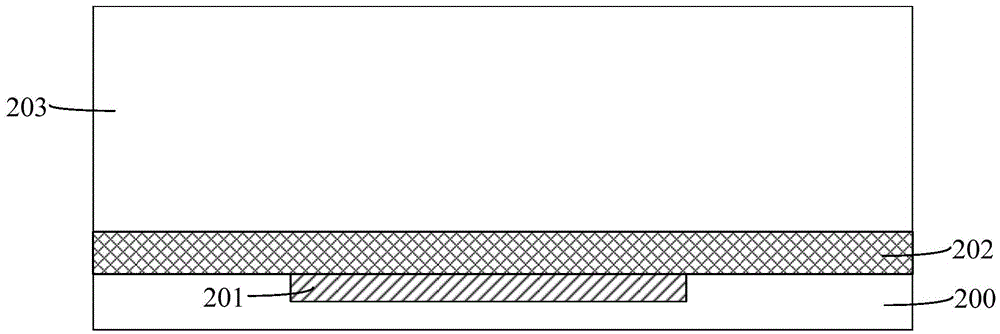

Semiconductor device and preparation method thereof

PendingCN112420850AReduce leakageAvoid interface stateSemiconductor/solid-state device manufacturingDiodeDevice materialSemiconductor

The invention discloses a semiconductor device and a preparation method thereof. The semiconductor device sequentially comprises a substrate; a multilayer semiconductor layer and a P-type epitaxial layer; an anode which is positioned on one side, far away from the multilayer semiconductor layer, of the P-type epitaxial layer; and a cathode which is positioned on one side, far away from the substrate, of the multilayer semiconductor layer, wherein the vertical projection of the anode on the substrate is at least partially overlapped with the vertical projection of the P-type epitaxial layer onthe substrate. By adopting the technical scheme, the P-type epitaxial layer is additionally arranged in the semiconductor device, and the two-dimensional electron gas below the anode is exhausted by lifting the energy band through the P-type epitaxial layer, so that the device electric leakage of the semiconductor device is reduced; on the other hand, the semiconductor device does not need to etchmultiple semiconductor layers to form an anode groove, etching damage does not exist, and the interface state of a traditional anode groove structure is avoided; compared with an anode groove etchingprocess, the uniformity of the P-type epitaxial layer is better, and the consistency of forward turn-on voltage of the device can be improved.

Owner:GPOWER SEMICON

Formation method of semiconductor structure

ActiveCN106409752AImprove electrical performancePlay a protective effectSemiconductor/solid-state device manufacturingSemiconductor structureProtection layer

A formation method of a semiconductor structure comprises the steps of providing a substrate in which a bottom-layer metal layer is formed; forming an etching barrier layer covering the surfaces of the substrate and the bottom-layer metal layer; forming a dielectric layer covering the surface of the etching barrier layer; forming an opening penetrating the dielectric layer, and exposing the surface of the etching barrier layer out of the bottom of the opening; adopting a dry etching process of an etching gas containing CF3I to etch a part of thickness of etching barrier layer located at the bottom of the opening, and forming a protection layer on the surface of the side wall of the opening while etching the part of thickness of etching barrier layer; after the protection layer is formed, adopting an isotropy dry etching process to etch and remove the residual thickness of etching barrier layer until the top surface of the bottom-layer metal layer is exposed; forming a conductive layer on the surface of the exposed bottom-layer metal layer, wherein the conductive layer fills the opening. According to the present invention, the etching damage to the bottom-layer metal layer is reduced, and the electrical property of the semiconductor structure is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

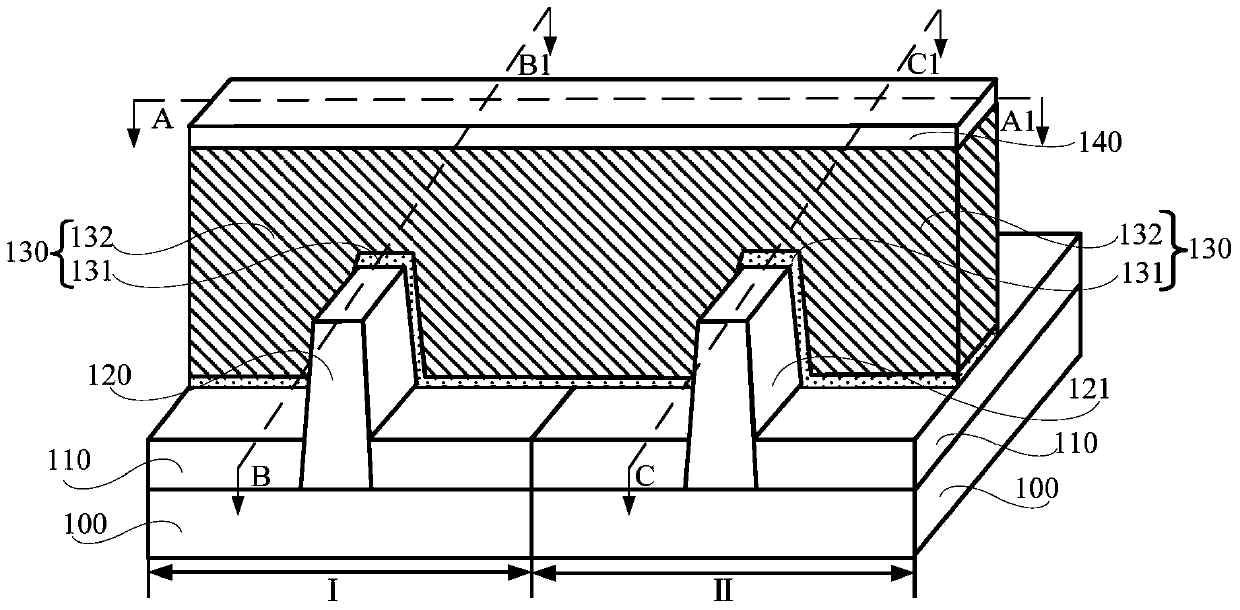

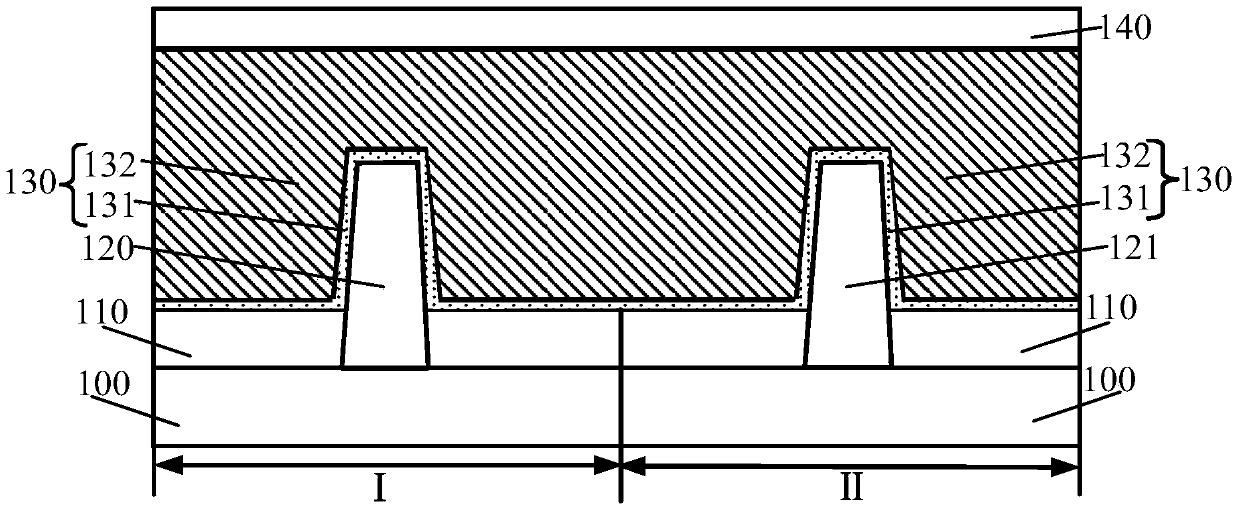

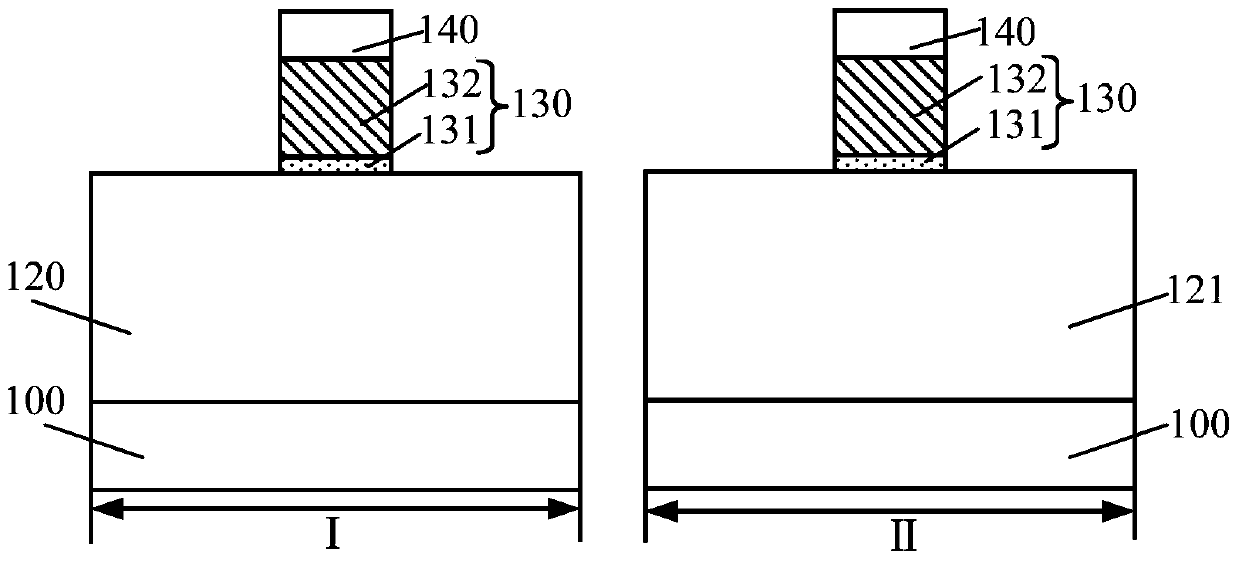

Method for forming semiconductor device

ActiveCN106558494AImprove protectionAvoid exposureSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceProtection layer

The invention discloses a method for forming a semiconductor device. The method includes the following steps: providing a substrate which has a first region and a second region which are adjacent to each other, the surface of the substrate having a gate electrode structure to stretch across the first region and the second region, the surface of the top of the gate electrode structure is covered with a protection layer; forming a first blockage layer which covers the first region and the second region; removing the protection layer of the second region and the first blockage layer on the surface of the substrate, forming a second side wall on the side wall of the gate electrode structure of the second region; following the formation of the second side wall, forming a second blockage layer which covers the first region and the second region; injecting ions to the first blockage layer and the second blockage layer; removing the protection surface of the first region and the first blockage layer and the second blockage layer after being injected with ions of the surface of the substrate, forming a first side wall on the side wall of the gate electrode structure of the first region. The method increases the properties of the semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor device forming method

ActiveCN107591363AImprove electrical performanceGood etch rate uniformityTransistorSemiconductor/solid-state device manufacturingEngineeringElectrical performance

The invention discloses a semiconductor device forming method. The method comprises steps that: a base comprising a first area and a second area is provided, wherein the first area base and the secondarea base are provided with first oxidation layers; an etching process is carried out to etch and remove the first oxidation layer with a first thickness in the first area; after the etching processis carried out, the remaining first oxidation layer in the first area is subjected to a cleaning process; the etching process and the cleaning process are carried out alternatively until the first oxidation layer in the first area is removed; and a second oxidation layer is formed on the first area base, wherein the thickness of the second oxidation layer is different from that of the first oxidation layer. The first area base can be prevented from being etched and damaged, the first area base can thus keep a good surface morphology, and the electrical performance of the formed semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

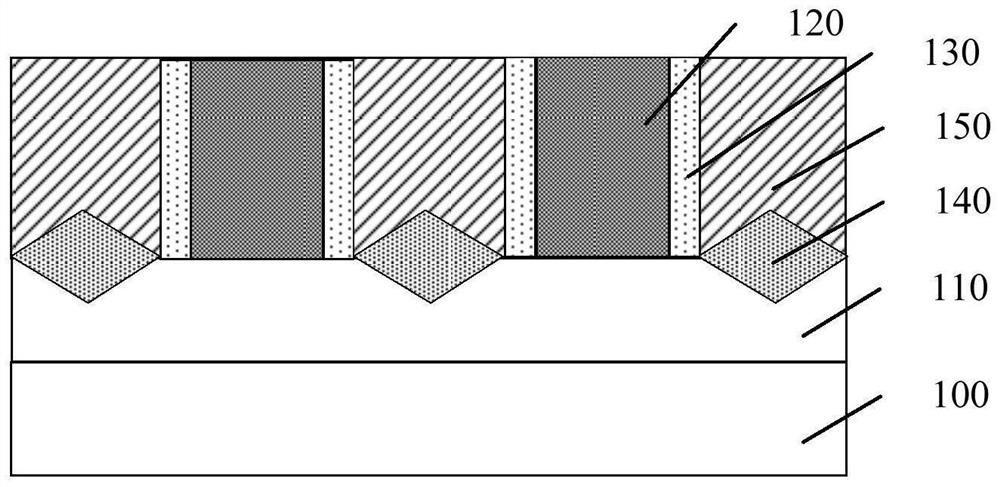

Semiconductor component and its forming method

ActiveCN106558608AImprove protectionImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

The invention provides a semiconductor component and its forming method wherein the method comprises: providing a substrate whose surface is provided with a plurality of separately arranged initial metal grid electrodes, side walls at the side walls of the initial metal grid electrodes, and a first interlayer dielectric layer covering the substrate surface and the side walls at the side walls of initial metal grid electrodes with the top surface of the first interlayer dielectric layer leveled with the top surfaces of the initial metal grid electrodes; etching the initial metal grid electrodes to form target metal grid electrodes wherein the middle parts of the target metal grid electrodes are higher than the edge parts; forming a protection layer covering the target metal grid electrodes wherein the surface of the protection layer is leveled with the top surface of the first interlayer dielectric layer; forming a second interlayer dielectric layer covering the first interlayer dielectric layer, the side walls and the protection layer; and forming self-aligning contact holes that penetrate the thicknesses of the first interlayer dielectric layer and the second interlayer dielectric layer between adjacent target metal grid electrodes. The method of the invention is capable of increasing the performance of the semiconductor.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

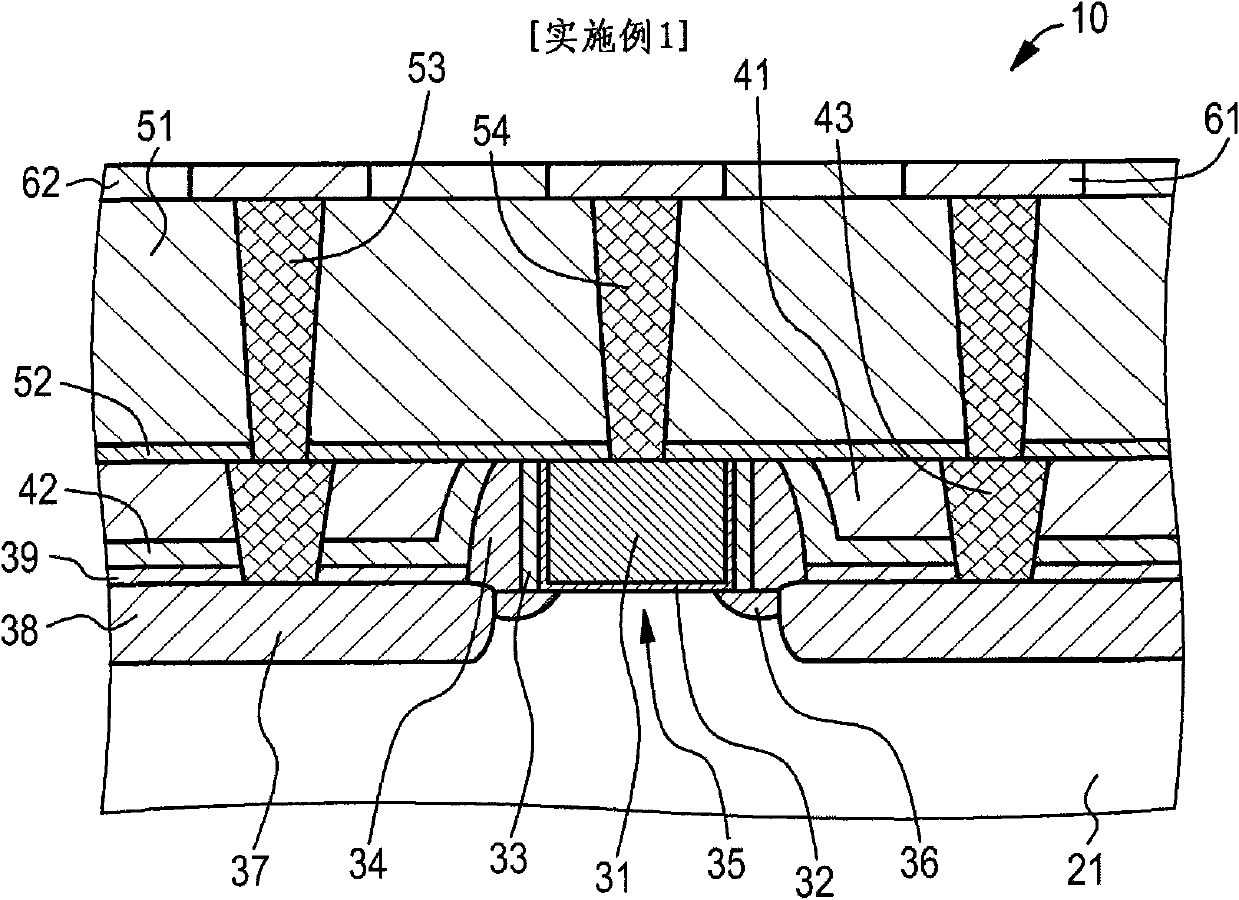

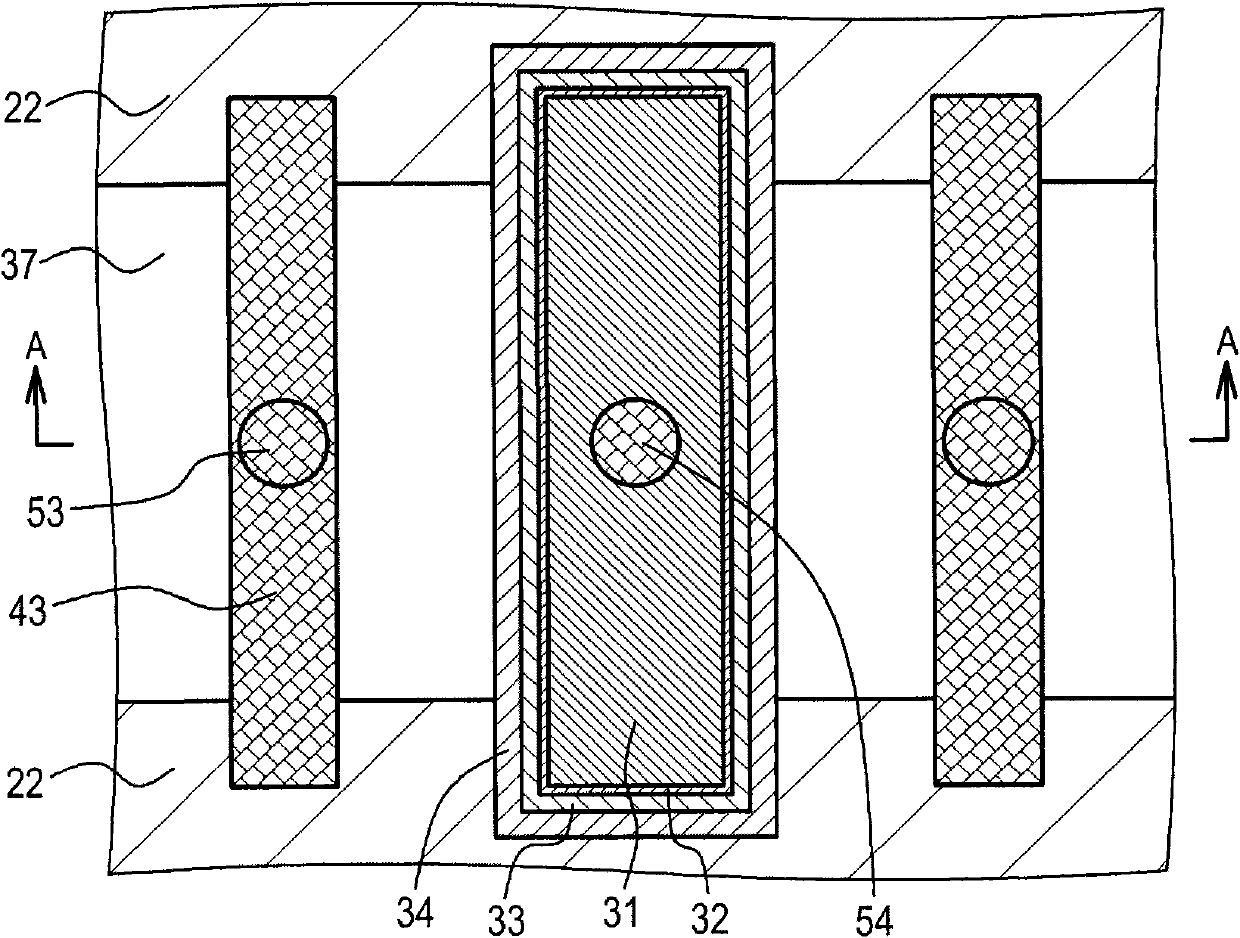

Memory structure and forming method thereof

PendingCN112038340AIncrease the areaImprove controlTransistorSemiconductor/solid-state device manufacturingStructural engineeringSemiconductor

The invention relates to a storage structure and a forming method thereof. The storage structure comprises: a semiconductor substrate, wherein a plurality of discrete active regions arranged in rows and columns are formed on the semiconductor substrate, a first groove is arranged between adjacent active regions, and the first groove is filled with an insulating layer; two second grooves located ineach active region and distributed in the row direction, wherein each active region is divided into a drain electrode located in the middle and two source electrodes located on the two sides of the drain electrode through the two second grooves; third grooves located in part of the insulating layers on the two sides of the bottoms of the second grooves, wherein at least part of the surfaces of the side walls of the two sides of the active region on the bottoms of the second grooves are exposed out of the third grooves, the third grooves are communicated with the corresponding second grooves,and every two adjacent third grooves in the row direction are not communicated; and gate structures positioned in the second grooves and the third grooves. According to the storage structure, the magnitude of leakage current is reduced.

Owner:CHANGXIN MEMORY TECH INC

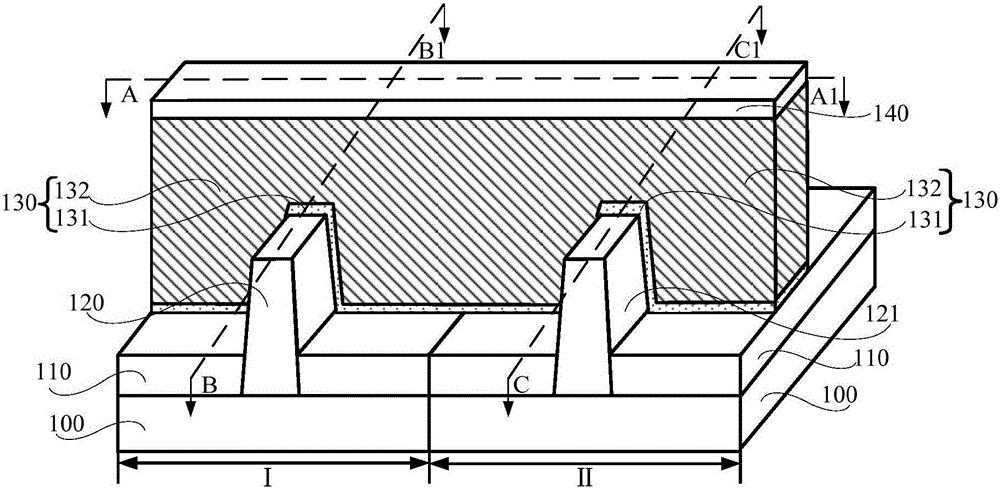

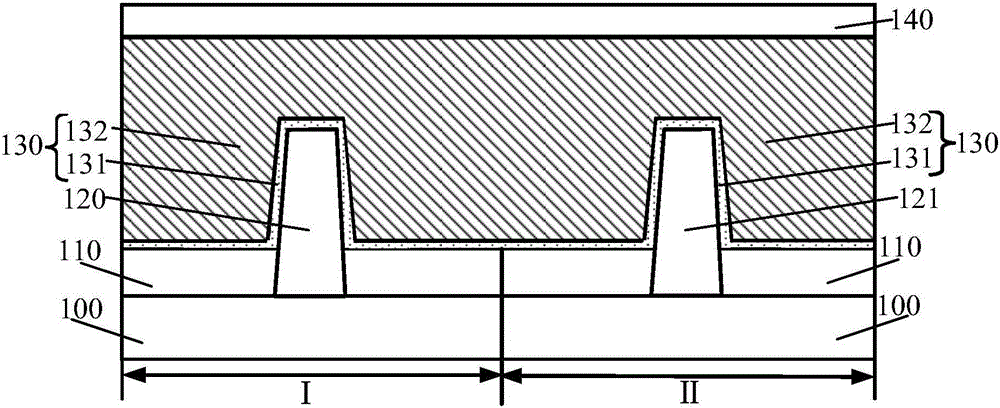

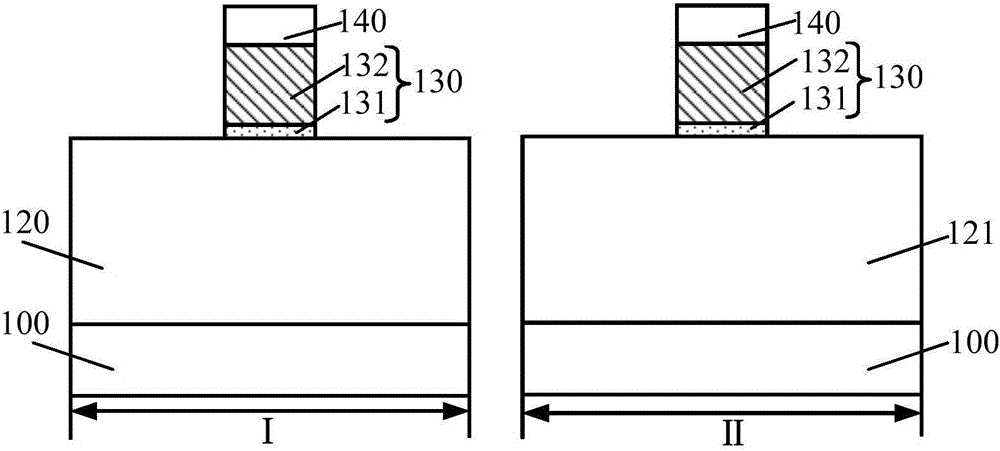

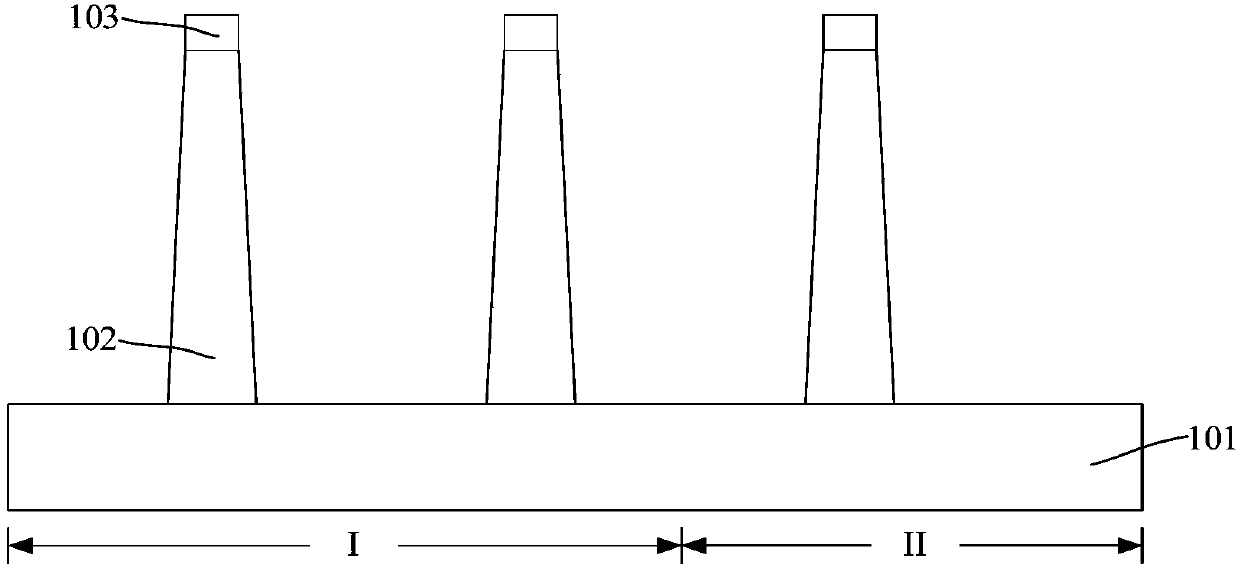

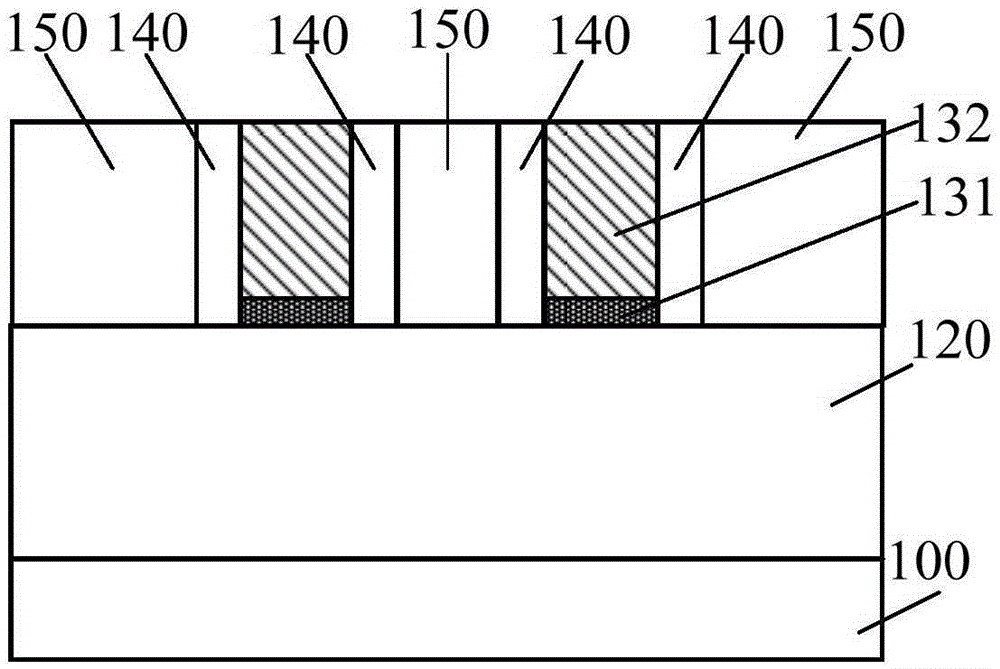

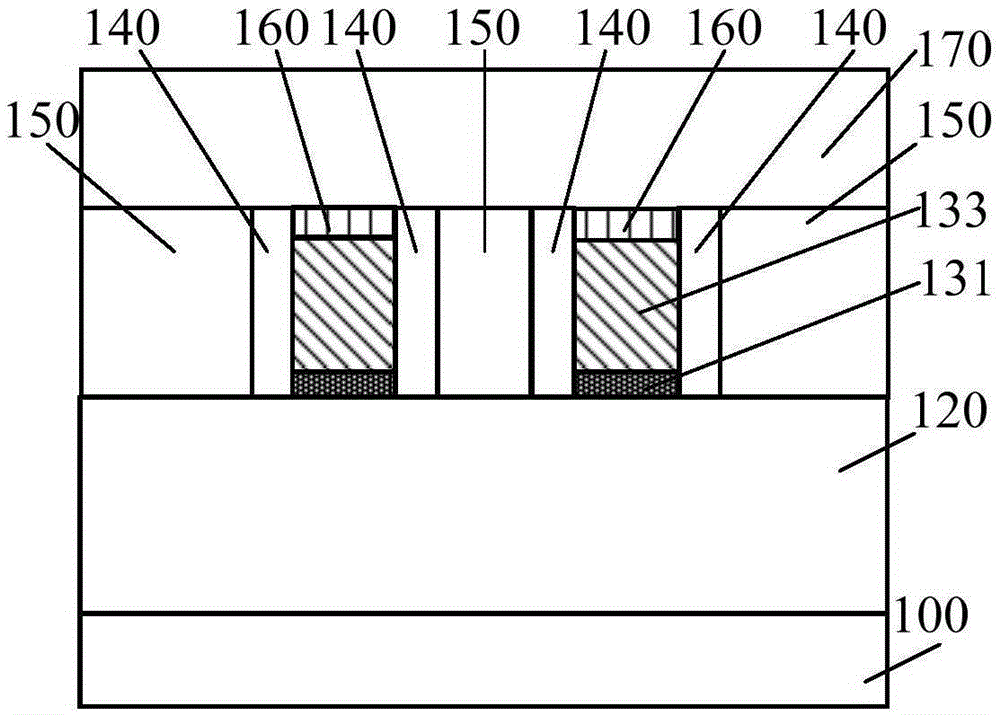

Semiconductor structure and formation method thereof

PendingCN113363321AImprove performanceNo etch damageSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsElectrically conductive

The invention discloses a semiconductor structure and a formation method thereof. The method comprises the steps of providing a substrate, wherein the surface of the substrate is provided with a source-drain doping layer; forming a channel column on the surface of part of the source-drain doping layer; forming an initial gate structure on the side wall surface and the top surface of the channel column; forming a first protection layer on the side surface of the initial gate structure; forming a dielectric structure on the substrate, wherein the dielectric structure covers the surface of the first protection layer, and the dielectric structure and the first protection layer are made of different materials; and forming a first conductive plug electrically connected with the source-drain doping layer in the dielectric structure. The semiconductor structure formed by the method is good in performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

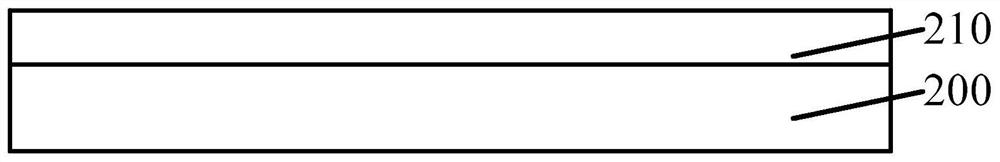

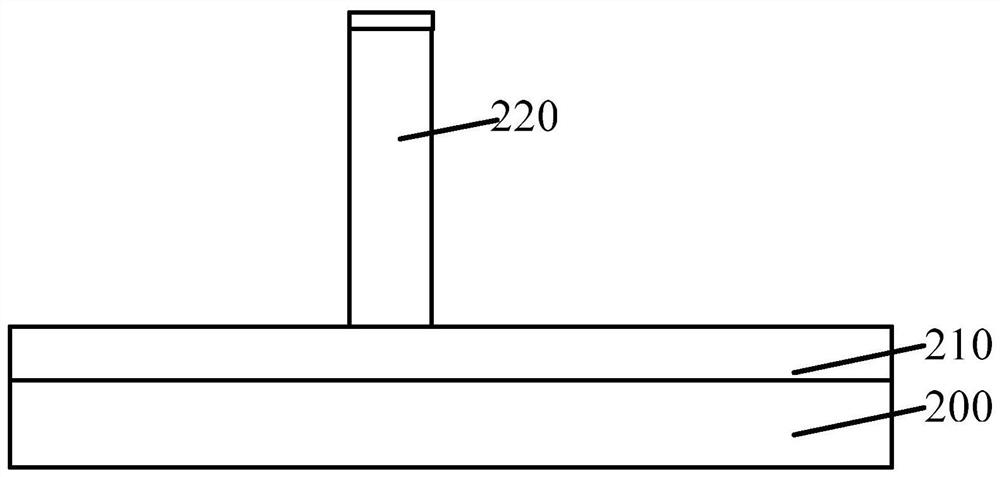

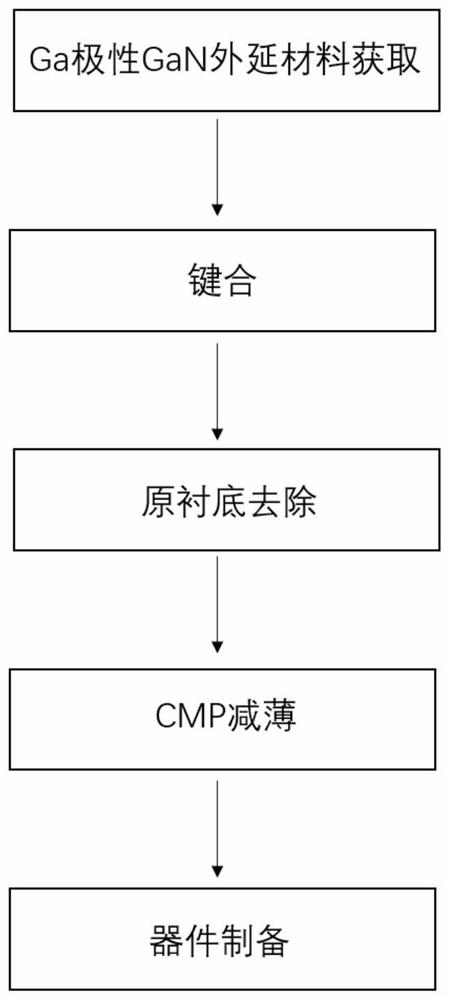

Method for preparing N-polarity GaN based on CMP, N-polarity GaN and application of N-polarity GaN

PendingCN114023640AEasy to operateLow costSemiconductor/solid-state device manufacturingSemiconductor devicesNanoparticleOhmic contact

The invention discloses a method for preparing N-polarity GaN based on CMP, the N-polarity GaN and application of the N-polarity GaN. The method for preparing N-polarity GaN based on CMP comprises the steps of exposing an N-polarity surface of a Ga-polarity GaN material; and chemically and mechanically polishing and thinning the N-polarity surface of the Ga-polarity GaN material by adopting an alkaline polishing solution so as to expose N-polarity GaN in the Ga-polarity GaN material, wherein the alkaline polishing solution contains grinding and polishing nanoparticles. The N-polarity GaN prepared by the method for preparing the N-polarity GaN based on the CMP provided by the embodiment of the invention has no etching damage, the ohmic contact resistance can be reduced, the performance of the N-polarity GaN and the performance of a device of the N-polarity GaN are further improved, and the surface roughness of the prepared N-polarity GaN is smaller.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

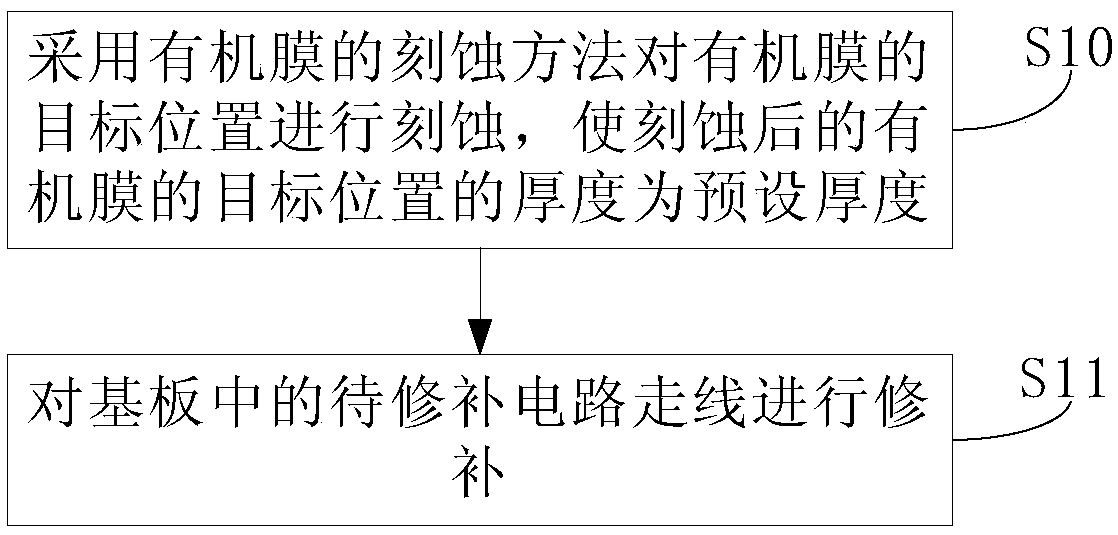

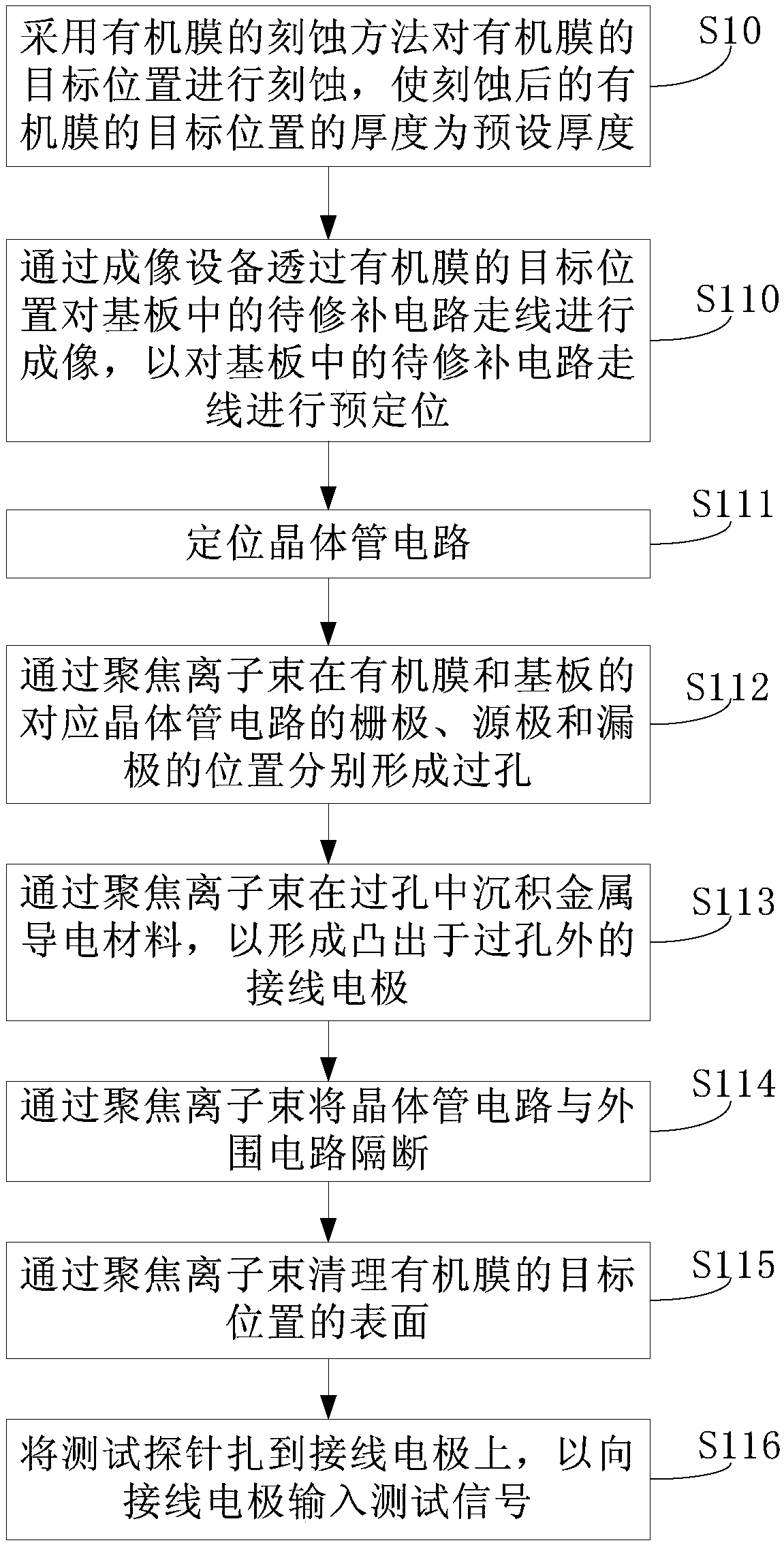

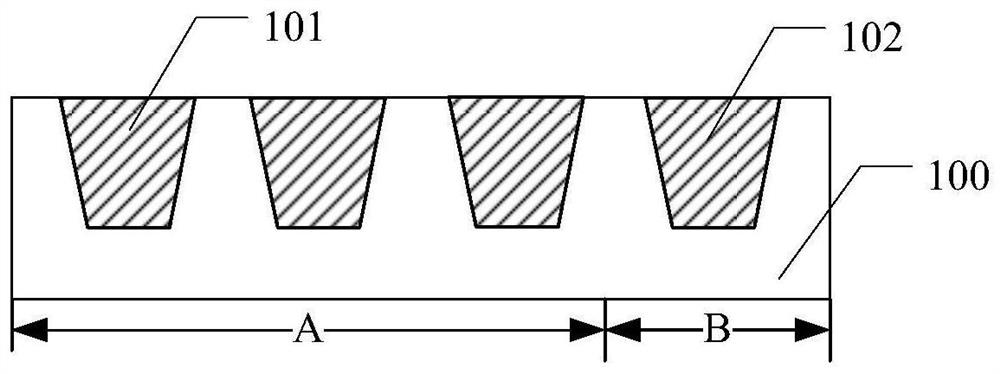

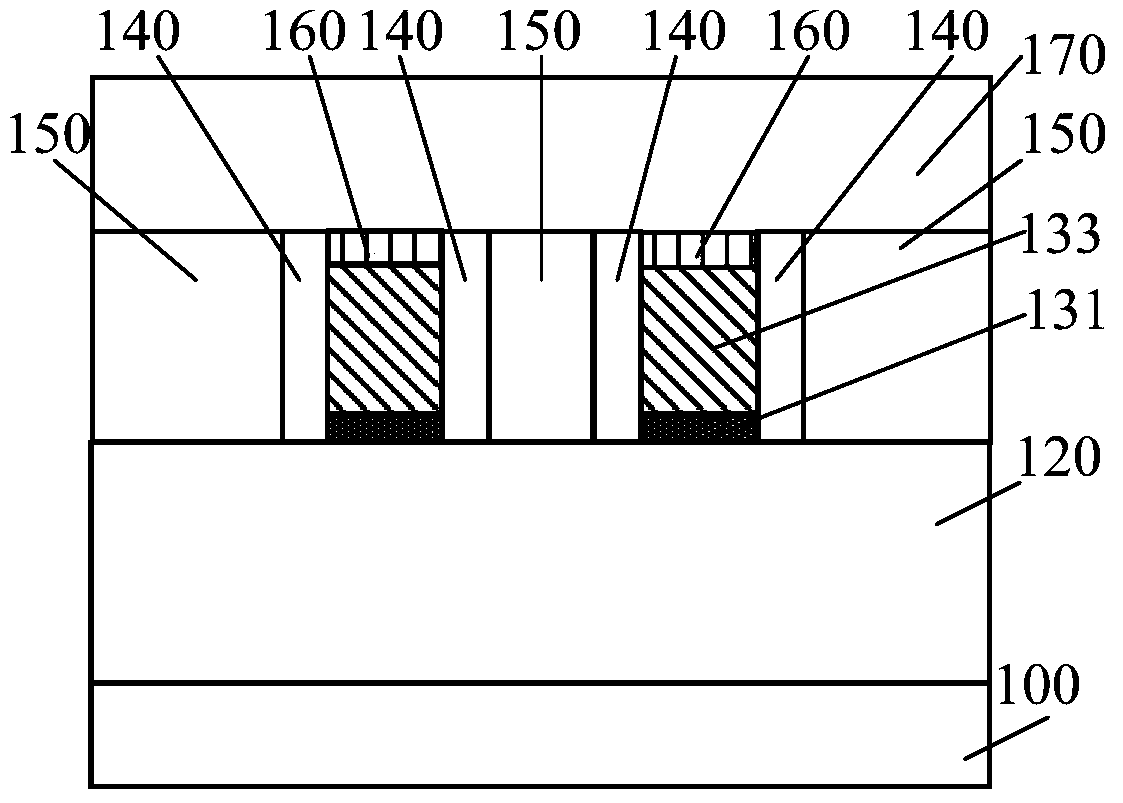

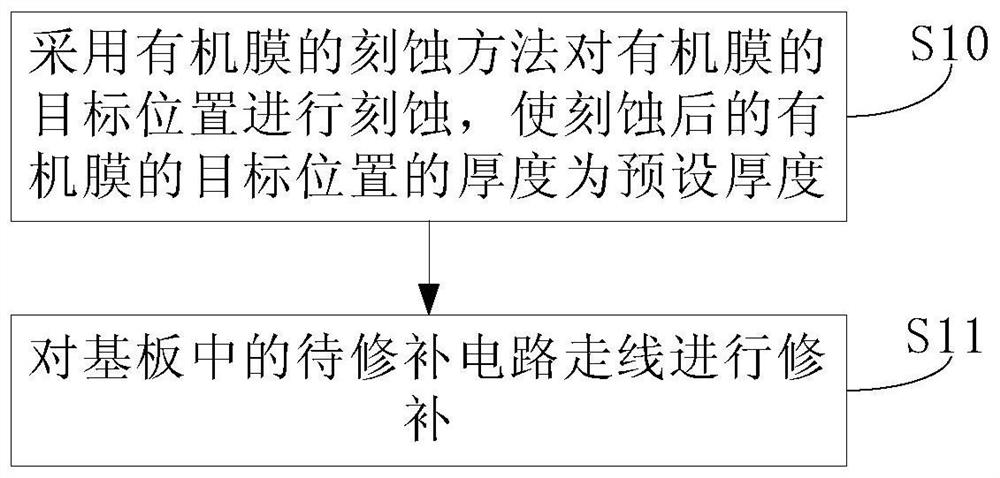

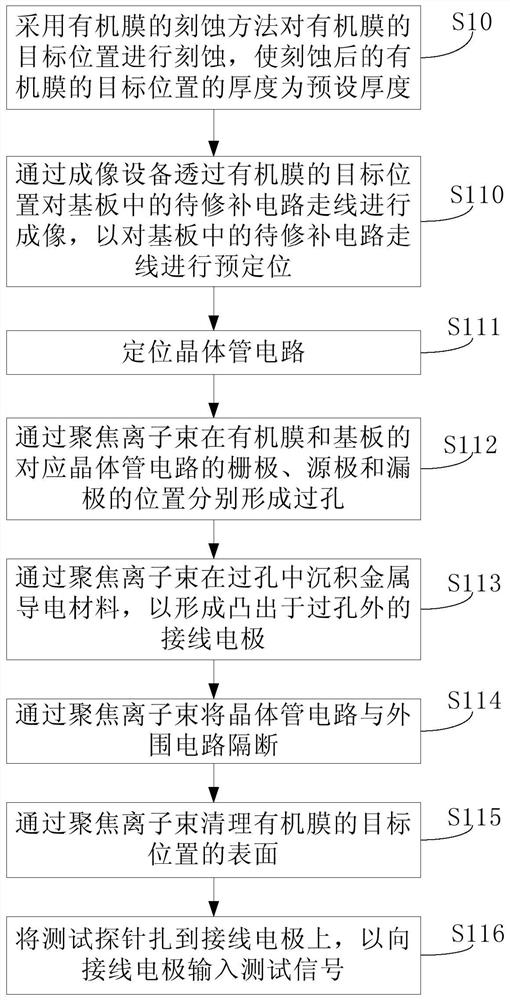

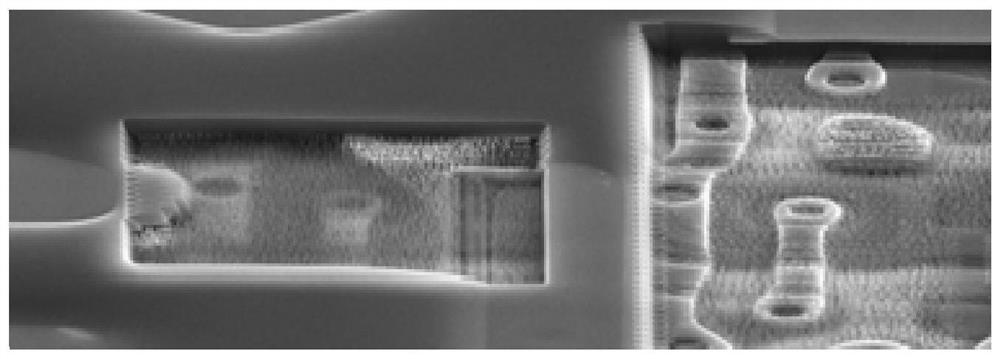

Method for etching organic film and method for repairing display area circuit of display substrate

ActiveCN109546012ANo etch damageSolve the problem of etch damageSolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmEtching

The invention provides a method for etching an organic film and a method for repairing a display area circuit of a display substrate. The etching method of the organic film comprises the following steps: etching a to-be-etched position of the organic film through a focused ion beam, and introducing water vapor into a to-be-etched surface of the to-be-etched position of the organic film in the etching process. According to the organic film etching method, the water vapor is introduced to the to-be-etched surface in the process of etching the organic film by using the focused ion beam; the to-be-etched position of the organic film can be rapidly etched in a targeted manner, and other non-etched positions of the organic film cannot be etched and damaged in the etching process, so that the problem that the non-etched positions are etched and damaged due to existing concentrated sulfuric acid etching is solved, and meanwhile, the etching speed is also increased.

Owner:BOE TECH GRP CO LTD +1

Semiconductor structure and forming method thereof

ActiveCN112635659AImprove performanceConductivity effectMagnetic-field-controlled resistorsGalvano-magnetic device detailsSemiconductor structureEngineering physics

The invention relates to a semiconductor structure and a forming method thereof, and the method comprises the steps: providing a substrate which is internally provided with a first conductive layer extending in a first direction and being arranged in a second direction, forming initial magnetic tunnel structures on the surface of the first conductive layer and the surface of the substrate; forming a first trench and a second trench in the initial magnetic tunnel structure, the second trench extending in a first direction, the first trench being located between adjacent second trenches, the first trench extending in a second direction, the first trench having a first size in the first direction, the second trench having a second size in the second direction, the first size being smaller than the second size; forming mask layers in the first trench and on the surfaces of the side walls of the second trench, the first trench is filled with the mask layers; and etching the initial magnetic tunnel structures by taking the mask layers as masks until the surface of the substrate is exposed, and forming a magnetic tunnel structure on the surface of the first conductive layer. The semiconductor structure formed by the method is good in performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor structure and forming method thereof

ActiveCN112531103AImprove performanceGood vertical shapeMagnetic-field-controlled resistorsSolid-state devicesSemiconductor structureMembrane surface

The invention discloses a semiconductor structure and a forming method thereof. The method comprises the following steps: providing a substrate; forming a first electromagnetic film on the substrate,wherein the surface of a part of the first electromagnetic film is provided with a tunnel layer and a second electromagnetic layer located on the surface of the tunnel layer; forming a first dielectric film on the surface of the first electromagnetic film, the surface of the side wall of the tunnel layer, and the surfaces of the side wall and the top of the second electromagnetic layer; forming asecond dielectric layer on the surface of the first dielectric film located at the top of the second electromagnetic layer; etching back the first dielectric film by using a first etching process until the surface of the first electromagnetic film is exposed, and forming a first dielectric layer on the surface of the side wall of the tunnel layer and the surfaces of the top and the side wall of the second electromagnetic layer, wherein the etching rate of the first etching process on the first dielectric film is higher than the etching rate of the first etching process on the second dielectriclayer; and etching the first electromagnetic film by taking the first dielectric layer and the second dielectric layer as masks until the surface of the substrate is exposed, thereby forming a firstelectromagnetic layer. The semiconductor structure formed by the method is good in performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

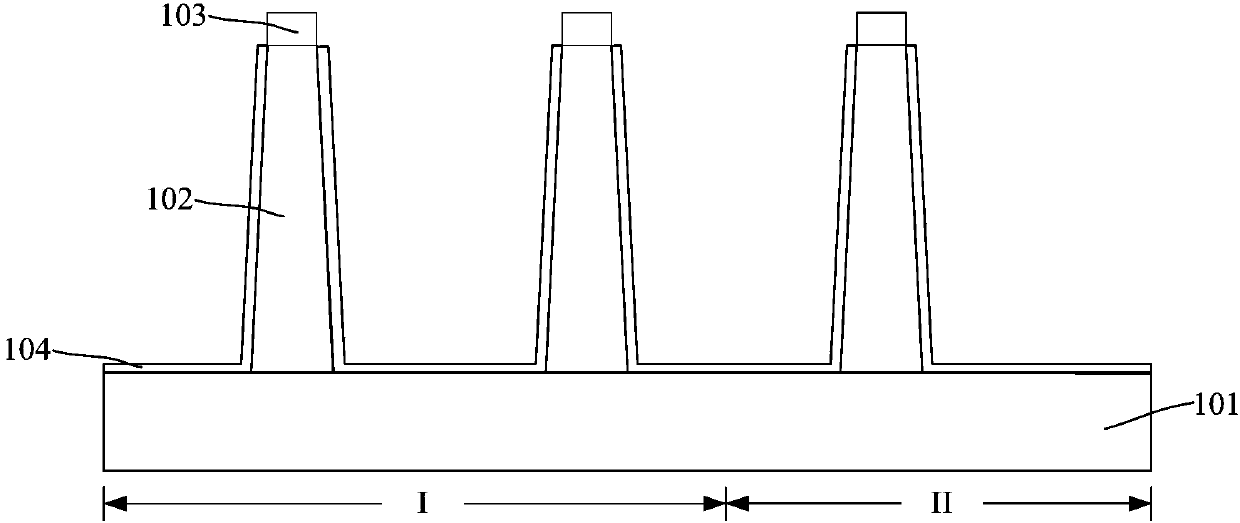

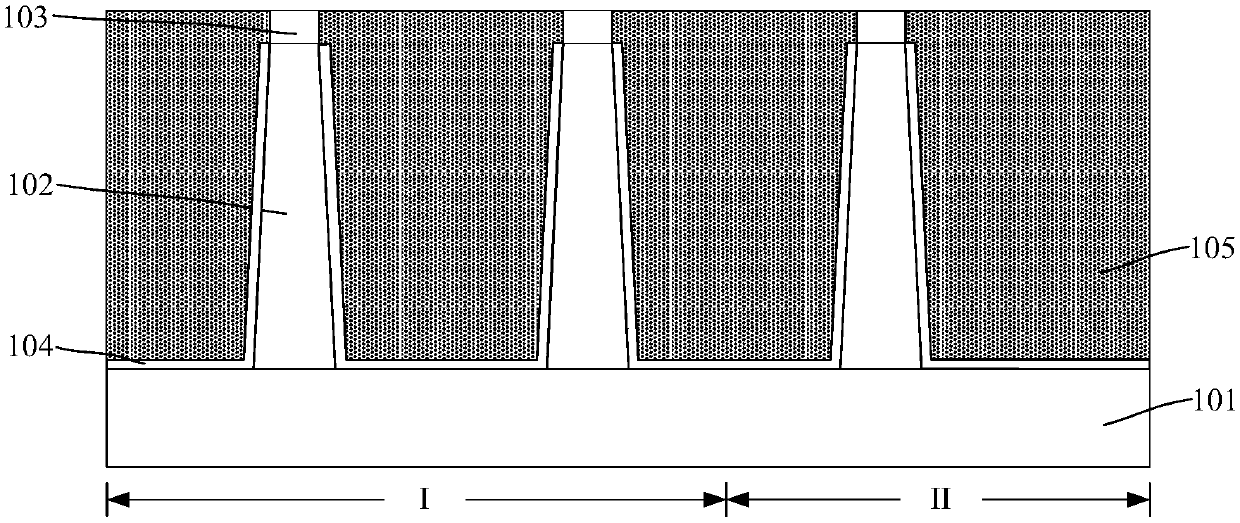

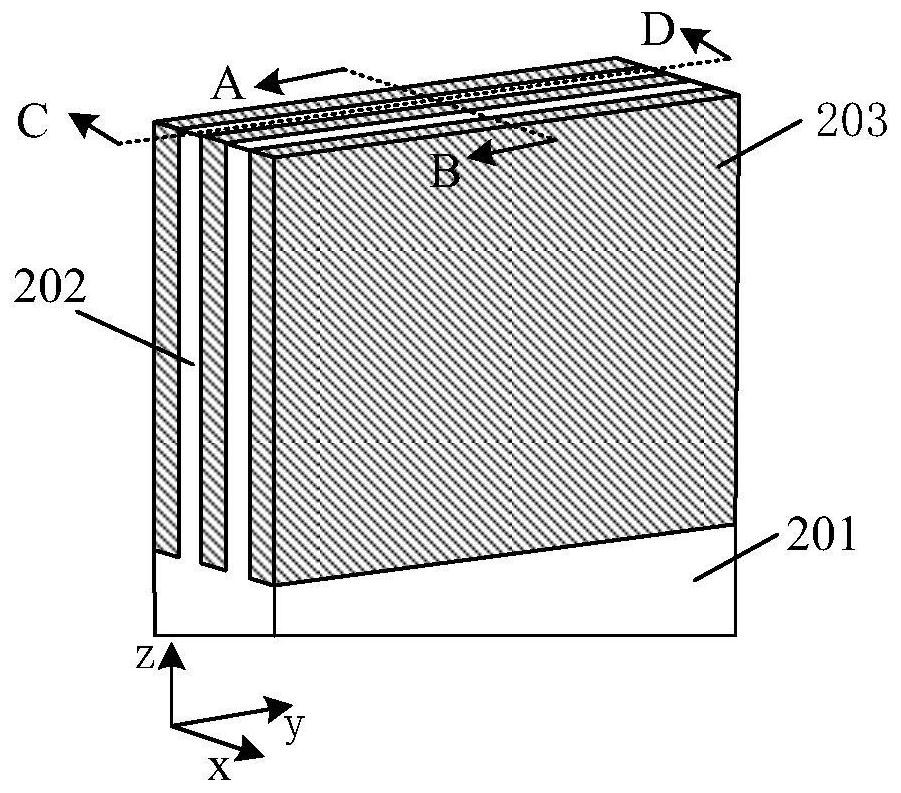

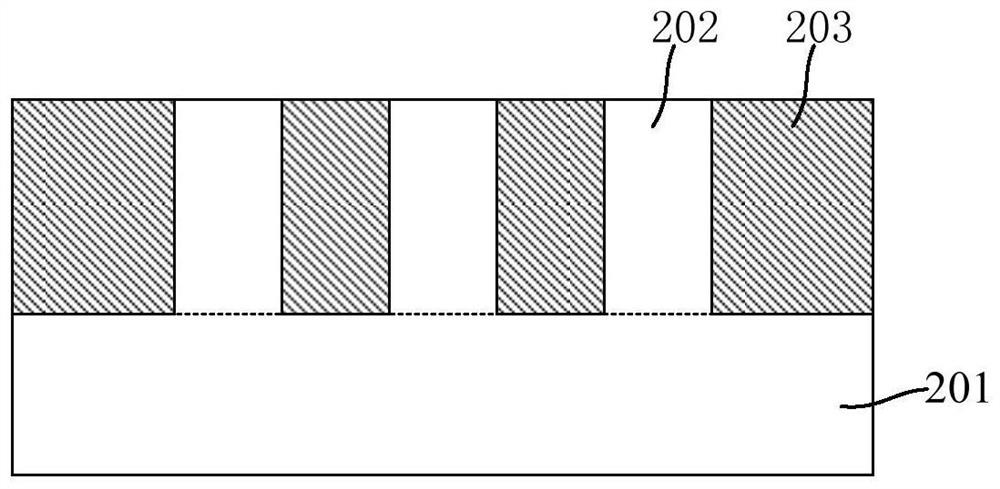

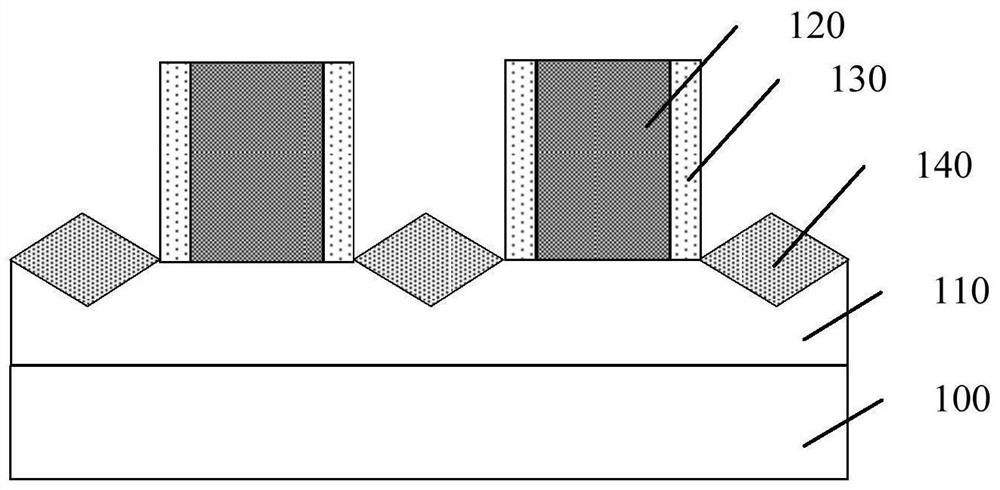

A self-aligned quadruple patterning technique

ActiveCN107993925BHigh densityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesGraphicsDeposition process

The invention provides a self-aligned quadruple pattern technology (SAQP for short). According to the SAQP of the invention, through the secondary deposition process of side wall materials, on the premise that the current photoetching technology is not changed at all (that is, the size of a photoetching window is kept unchanged), the minimum size of 1 / 4 pitch can be obtained. Compared with the original self-aligned double-pattern technology (SRDP) wherein the minimum size of only 1 / 2 pitch can be obtained, the performance of the minimum size is greatly improved. As a result, the density of a semiconductor integrated circuit can be greatly improved.

Owner:YANGTZE MEMORY TECH CO LTD

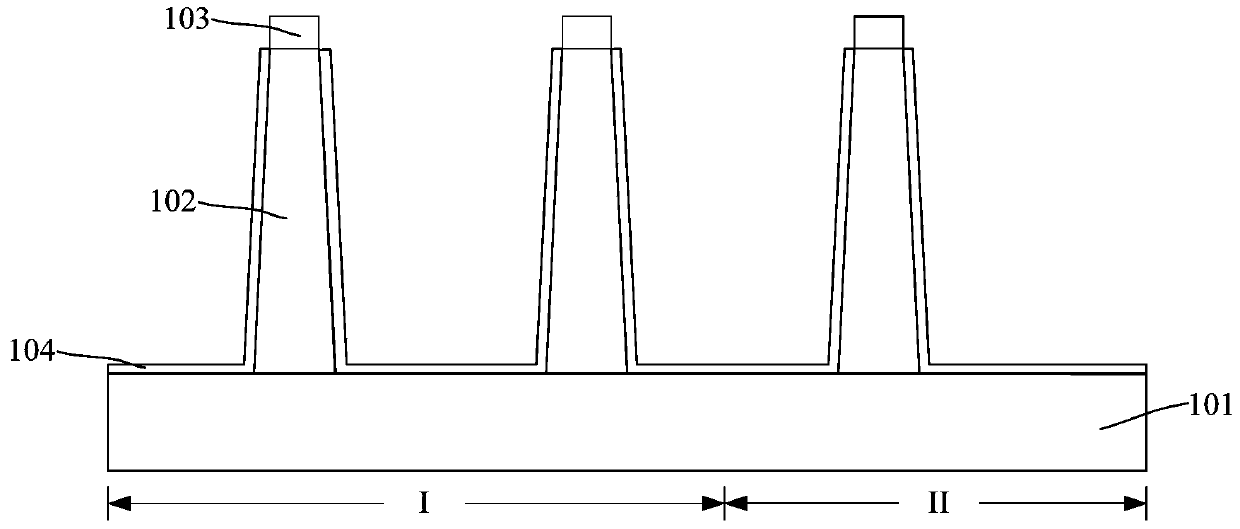

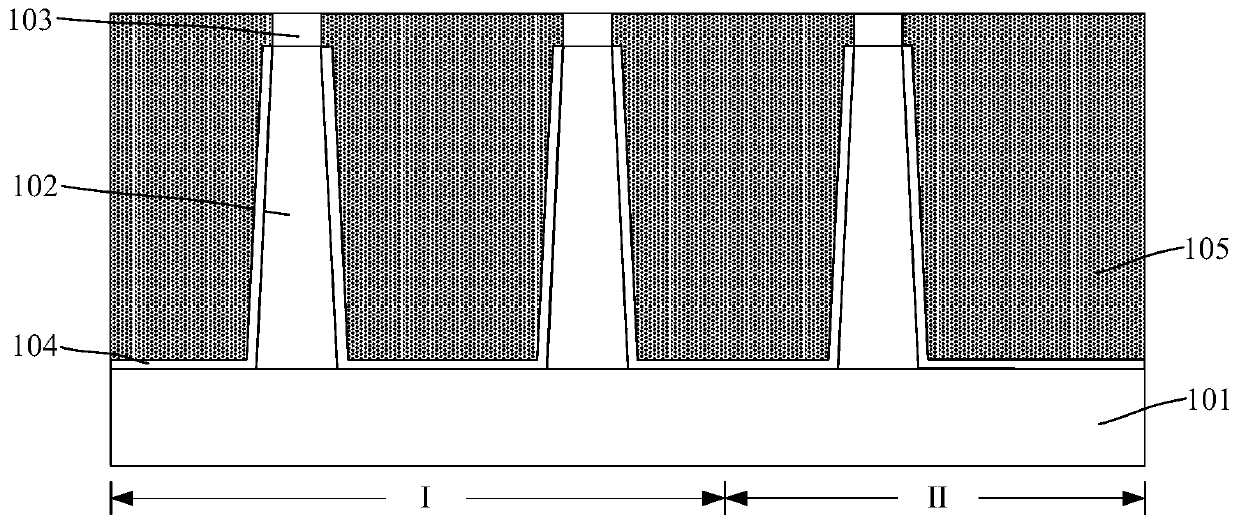

A method for realizing isolation of semiconductor devices

ActiveCN106531681BExcellent gap fillingImprove filling qualitySemiconductor/solid-state device manufacturingMicron scaleFilling rate

The invention discloses a method for achieving isolation of a semiconductor device. According to the method, a thermal oxidation technology is combined with a deposition technology; an active region of the semiconductor device is firstly formed; a high depth-to-width ratio gap is filled to form narrow STI isolation; and a low depth-to-width ratio gap is finally filled to form wide STI isolation. The method has the advantages that the method has excellent gap filling ability for a micron-scale gap or the high depth-to-width ratio gap with a sub-45nm technology node, the filling quality is good and no hole or crack is generated; the filling rate is high, stable and controllable; an etching damage of an HDP-CVD to a substrate is avoided; and the method does not depend on the shape and form of the section of the gap, and is completely compatible with a bulk silicon CMOS process, simple in process and low in cost.

Owner:PEKING UNIV

Semiconductor device and method of forming the same

ActiveCN106558608BImprove protectionImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesProtection layerDielectric layer

The invention provides a semiconductor component and its forming method wherein the method comprises: providing a substrate whose surface is provided with a plurality of separately arranged initial metal grid electrodes, side walls at the side walls of the initial metal grid electrodes, and a first interlayer dielectric layer covering the substrate surface and the side walls at the side walls of initial metal grid electrodes with the top surface of the first interlayer dielectric layer leveled with the top surfaces of the initial metal grid electrodes; etching the initial metal grid electrodes to form target metal grid electrodes wherein the middle parts of the target metal grid electrodes are higher than the edge parts; forming a protection layer covering the target metal grid electrodes wherein the surface of the protection layer is leveled with the top surface of the first interlayer dielectric layer; forming a second interlayer dielectric layer covering the first interlayer dielectric layer, the side walls and the protection layer; and forming self-aligning contact holes that penetrate the thicknesses of the first interlayer dielectric layer and the second interlayer dielectric layer between adjacent target metal grid electrodes. The method of the invention is capable of increasing the performance of the semiconductor.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Etching method of organic film and repairing method of display area circuit of display substrate

ActiveCN109546012BNo etch damageSolve the problem of etch damageSolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmEtching

The invention provides an etching method of an organic film and a repairing method of a circuit in a display area of a display substrate. The etching method of the organic film includes etching the position to be etched of the organic film by means of a focused ion beam; In the etching method of the organic film, water vapor is fed to the surface to be etched during the process of etching the organic film by the focused ion beam, so that the position to be etched of the organic film can be etched quickly in a targeted manner, and the During the etching process, it will not cause etching damage to other non-etching positions of the organic film, thereby solving the problem of non-etching positions being damaged by etching caused by the existing concentrated sulfuric acid etching, and also speeding up the etching process. speed.

Owner:BOE TECH GRP CO LTD +1

3d NAND memory and its formation method

ActiveCN111540752BIncrease widthAvoid cutsSolid-state devicesSemiconductor devicesStructural engineeringMechanical engineering

Owner:YANGTZE MEMORY TECH CO LTD

Method for forming semiconductor device

ActiveCN107591363BImprove electrical performanceGood etch rate uniformityTransistorSemiconductor/solid-state device manufacturingDevice materialElectrical performance

The invention discloses a semiconductor device forming method. The method comprises steps that: a base comprising a first area and a second area is provided, wherein the first area base and the secondarea base are provided with first oxidation layers; an etching process is carried out to etch and remove the first oxidation layer with a first thickness in the first area; after the etching processis carried out, the remaining first oxidation layer in the first area is subjected to a cleaning process; the etching process and the cleaning process are carried out alternatively until the first oxidation layer in the first area is removed; and a second oxidation layer is formed on the first area base, wherein the thickness of the second oxidation layer is different from that of the first oxidation layer. The first area base can be prevented from being etched and damaged, the first area base can thus keep a good surface morphology, and the electrical performance of the formed semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Formation method of semiconductor structure

ActiveCN106409752BImprove electrical performancePlay a protective effectSemiconductor/solid-state device manufacturingSemiconductor structureDielectric layer

A formation method of a semiconductor structure comprises the steps of providing a substrate in which a bottom-layer metal layer is formed; forming an etching barrier layer covering the surfaces of the substrate and the bottom-layer metal layer; forming a dielectric layer covering the surface of the etching barrier layer; forming an opening penetrating the dielectric layer, and exposing the surface of the etching barrier layer out of the bottom of the opening; adopting a dry etching process of an etching gas containing CF3I to etch a part of thickness of etching barrier layer located at the bottom of the opening, and forming a protection layer on the surface of the side wall of the opening while etching the part of thickness of etching barrier layer; after the protection layer is formed, adopting an isotropy dry etching process to etch and remove the residual thickness of etching barrier layer until the top surface of the bottom-layer metal layer is exposed; forming a conductive layer on the surface of the exposed bottom-layer metal layer, wherein the conductive layer fills the opening. According to the present invention, the etching damage to the bottom-layer metal layer is reduced, and the electrical property of the semiconductor structure is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

3D NAND memory and method of forming the same

ActiveCN109727981BFlat surfaceHigh positioning accuracySolid-state devicesSemiconductor devicesEngineeringDielectric layer

A 3D NAND memory and its forming method, the forming method, before forming the stack structure, a semiconductor epitaxial layer is formed in the groove, when forming the semiconductor epitaxial layer, the forming process will not be affected by the depth of the through hole in the stack structure , size and shape, so that the surface of the formed semiconductor epitaxial layer has a flat surface, so that the channel layer in the storage structure and the semiconductor epitaxial layer can have good contact performance. In addition, the surface of the formed semiconductor epitaxial layer is lower than the surface of the dielectric layer, so that the formed etching stop layer (especially when the etching stop layer is made of metal material) can be limited in the groove above the semiconductor epitaxial layer, so that the etching The stop layer can maintain high position accuracy, and make the dielectric layer have a flat surface, which facilitates subsequent formation of a stacked structure.

Owner:YANGTZE MEMORY TECH CO LTD

Method of forming semiconductor device

ActiveCN106558494BImprove protectionAvoid exposureSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceProtection layer

The invention discloses a method for forming a semiconductor device. The method includes the following steps: providing a substrate which has a first region and a second region which are adjacent to each other, the surface of the substrate having a gate electrode structure to stretch across the first region and the second region, the surface of the top of the gate electrode structure is covered with a protection layer; forming a first blockage layer which covers the first region and the second region; removing the protection layer of the second region and the first blockage layer on the surface of the substrate, forming a second side wall on the side wall of the gate electrode structure of the second region; following the formation of the second side wall, forming a second blockage layer which covers the first region and the second region; injecting ions to the first blockage layer and the second blockage layer; removing the protection surface of the first region and the first blockage layer and the second blockage layer after being injected with ions of the surface of the substrate, forming a first side wall on the side wall of the gate electrode structure of the first region. The method increases the properties of the semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for achieving isolation of semiconductor device

ActiveCN106531681AExcellent gap fillingImprove filling qualitySemiconductor/solid-state device manufacturingMicron scalePower semiconductor device

The invention discloses a method for achieving isolation of a semiconductor device. According to the method, a thermal oxidation technology is combined with a deposition technology; an active region of the semiconductor device is firstly formed; a high depth-to-width ratio gap is filled to form narrow STI isolation; and a low depth-to-width ratio gap is finally filled to form wide STI isolation. The method has the advantages that the method has excellent gap filling ability for a micron-scale gap or the high depth-to-width ratio gap with a sub-45nm technology node, the filling quality is good and no hole or crack is generated; the filling rate is high, stable and controllable; an etching damage of an HDP-CVD to a substrate is avoided; and the method does not depend on the shape and form of the section of the gap, and is completely compatible with a bulk silicon CMOS process, simple in process and low in cost.

Owner:PEKING UNIV

Semiconductor structure and forming method thereof

PendingCN114792730AImprove performanceReduce parasitic capacitanceSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingContact holeSemiconductor structure

The invention discloses a semiconductor structure and a forming method thereof. The method comprises the steps of providing a substrate; forming a gate structure and a source-drain plug on the substrate, wherein a sacrificial side wall is arranged between the gate structure and the source-drain plug; forming a source-drain contact hole in the source-drain plug; forming a gate contact hole in the gate structure; after the source-drain contact hole and the gate contact hole are formed, the sacrificial side wall is removed, and a cavity is formed between the gate structure and the source-drain plug; and forming a dielectric layer on the gate structure and the source-drain plug, wherein the dielectric layer seals the top of the cavity. The semiconductor structure formed by the method is good in performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for preparing high quality GaN base material on specific saphire pattern substrate

InactiveCN1294650CNo etch damageNo maskLaser detailsSemiconductor/solid-state device manufacturingEpitaxial materialOptoelectronics

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

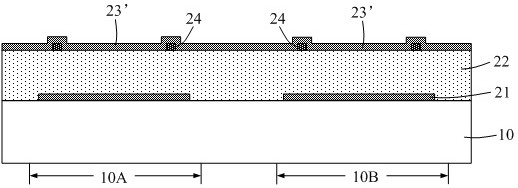

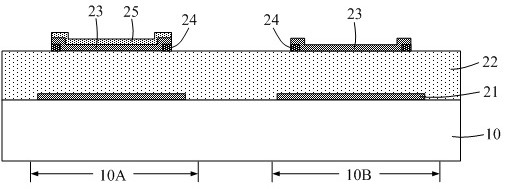

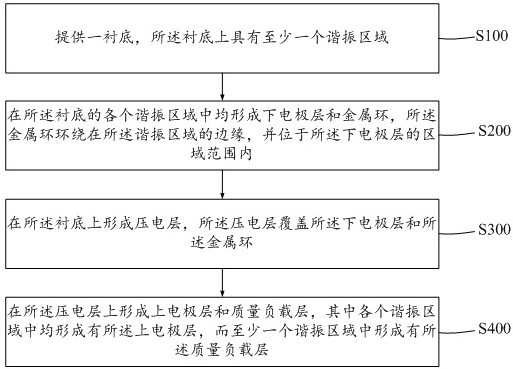

Semiconductor device and method of forming the same

ActiveCN112803912BImprove production efficiencyNo etch damageImpedence networksDevice materialEngineering

The invention provides a semiconductor device and a forming method thereof. By preferentially preparing the metal ring, the piezoelectric layer covers the metal ring, so that the metal ring will not be exposed from the surface of the piezoelectric layer, thereby avoiding damage to the metal ring when preparing the mass load layer, and can effectively improve the quality The limitation of the process of the load layer and the flexible adjustment of the order of the mass load layer and the upper electrode layer also improve the manufacturing efficiency of the device.

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP