Method for achieving isolation of semiconductor device

A device isolation and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of voids or cracks in trenches, high side profile requirements, etc., and achieve fast filling rate, excellent gap filling ability, low cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be described in detail below with reference to the drawings and specific examples.

[0046] The isolation of nano-scale silicon-based devices can be achieved according to the following steps:

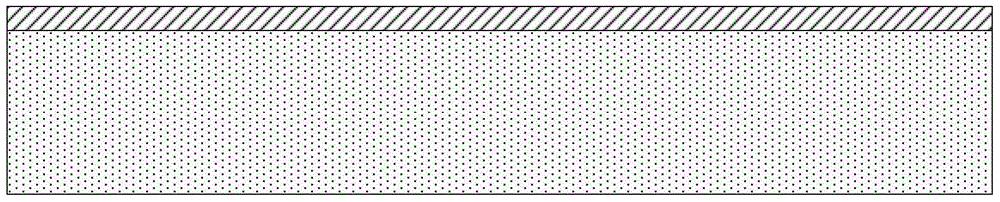

[0047] 1) ALD on (100) bulk silicon substrate SiO 2 , Si 3 N 4 The laminated structure is used as a hard mask layer, such as figure 1 Shown

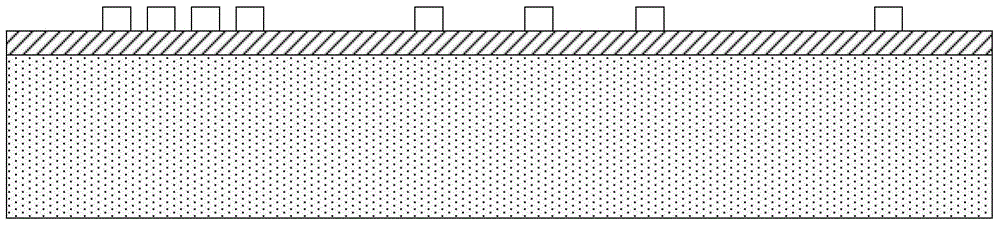

[0048] 2) Electron beam lithography defines the active region window, where the line width is 40nm, the minimum line spacing is 30nm, and the maximum line spacing is 0.5μm. Such as figure 2 Shown

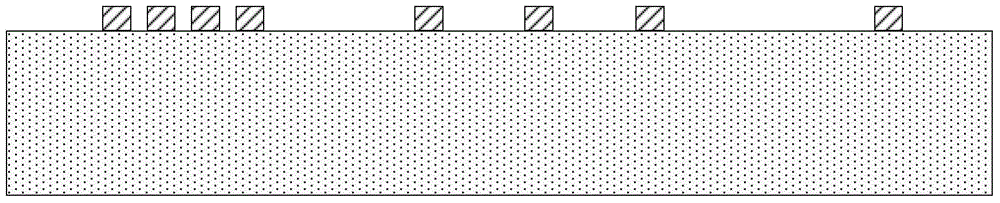

[0049] 3) Anisotropically etch the hard mask layer, and transfer the pattern defined by photolithography to the hard mask, exposing the silicon substrate;

[0050] 4) Remove the photoresist, such as image 3 Shown

[0051] 5) Anisotropic dry etching silicon Transfer the pattern of the hard mask to the silicon substrate to form the active area of silicon, such as Figure 4 Shown

[0052] 6) Dry oxygen oxidation is performed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More