3D NAND memory and method of forming the same

A 3DNAND, memory technology, applied in semiconductor devices, electric solid state devices, electrical components, etc., can solve problems such as poor contact between the channel layer and the epitaxial silicon layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

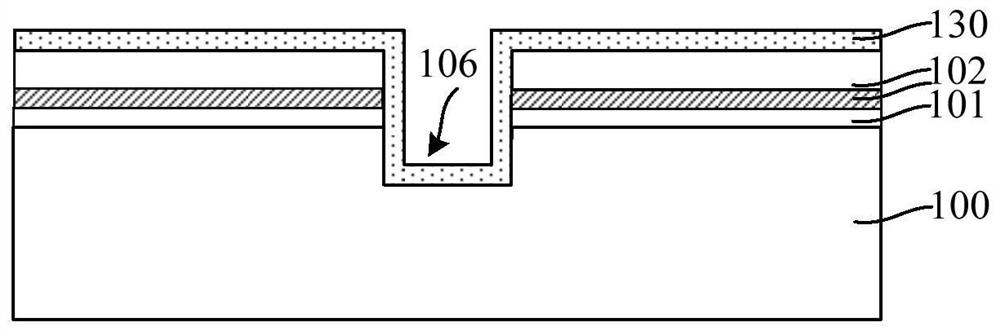

[0034] As mentioned in the background, the existing 3D NAND memory has the problem of poor contact between the channel layer and the epitaxial silicon layer (SEG).

[0035] The study found that the reason for the poor contact between the channel layer and the epitaxial silicon layer (SEG) in the existing 3D NAND memory is that: the existing formation of the epitaxial silicon layer (SEG) is through the selective epitaxial process after the channel hole is formed in the stack structure. However, during the selective epitaxial process, due to the influence of factors such as the depth, size and shape of the channel hole in the stacked structure, the surface of the formed epitaxial silicon layer (SEG) is not flat, and the subsequent formation of the epitaxial silicon layer (SEG) in the channel hole When the charge storage layer and the channel layer are separated, it is easy to cause poor contact between the channel layer and the surface of the epitaxial silicon layer (SEG).

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More