Formation method of semiconductor structure

A semiconductor and conductive layer technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems that the electrical properties of semiconductor structures need to be improved

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] It can be seen from the background art that the electrical performance of the semiconductor structure formed in the prior art needs to be improved.

[0033] The method for forming a semiconductor structure includes the following steps:

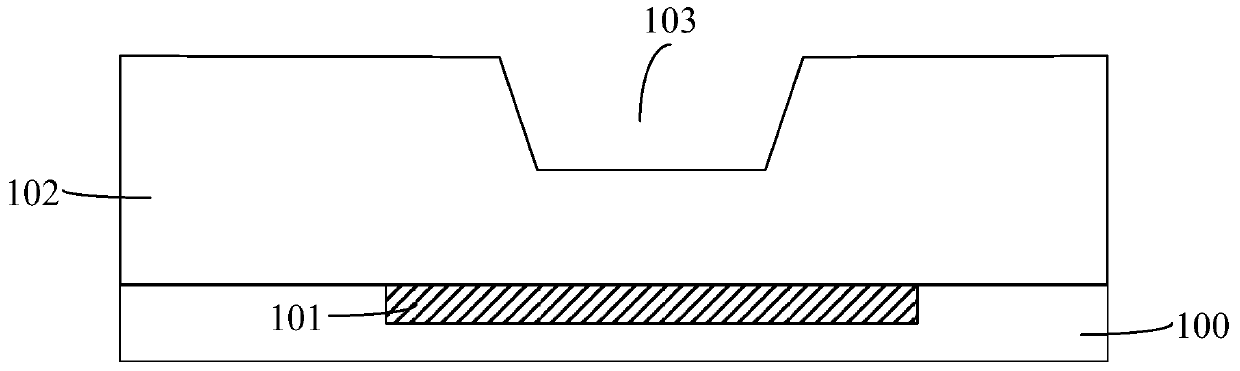

[0034] refer to figure 1 1. Provide a substrate 100 with an underlying metal layer 101 formed in the substrate 100 and a dielectric layer 102 formed on the surface of the substrate 100; a partial thickness of the dielectric layer 102 is etched to form a pre-opening 103 in the dielectric layer 102 .

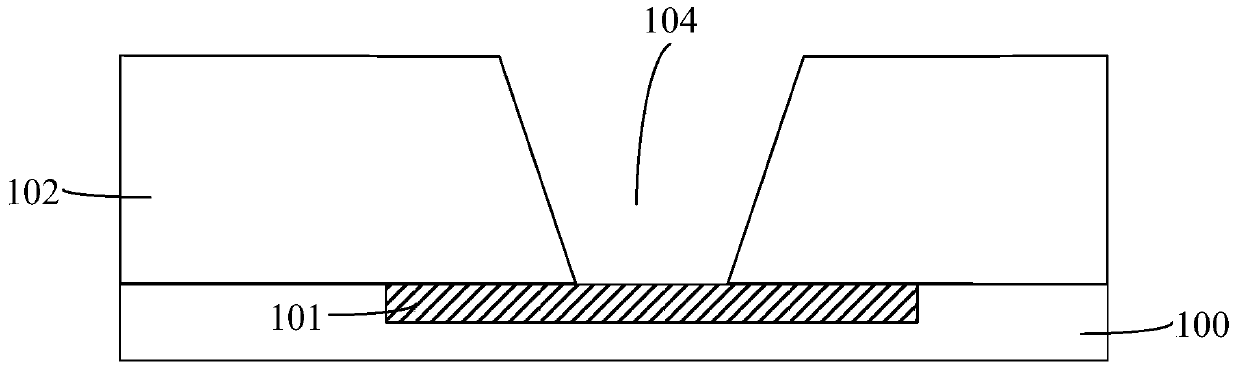

[0035] refer to figure 2 , etch at the pre-opening 103 (refer to figure 1 ) below the dielectric layer 102 to form an opening 104 penetrating through the dielectric layer 102, the bottom of the opening 104 exposes the surface of the underlying metal layer 101; a conductive layer filling the opening 104 is formed.

[0036] In the above method, the underlying metal layer 101 is severely damaged by etching, which makes the electrical per...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More