Semiconductor structure and formation method thereof

A technology of semiconductor and gate structure, which is applied in the field of semiconductor structure and its formation, and can solve problems such as the need to improve the performance of transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] As mentioned in the background, the performance of the existing fin field effect transistor with surrounding trench gate structure needs to be improved.

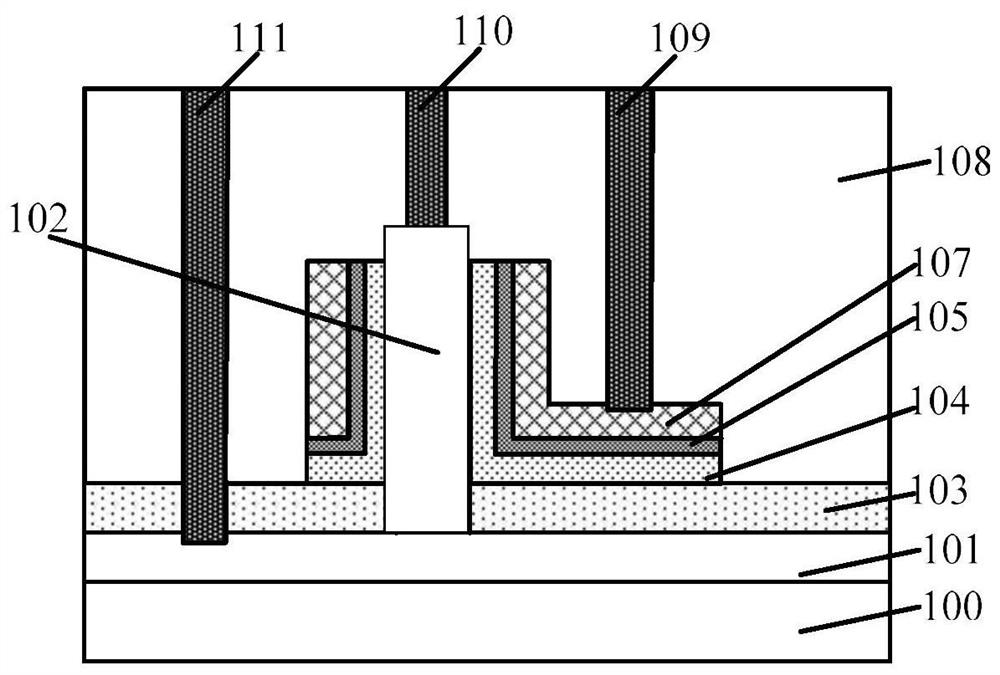

[0033] Describe in detail below in conjunction with accompanying drawing, figure 1 It is a structural schematic diagram of a fin field effect transistor with a trench gate surrounding structure.

[0034] Please refer to figure 1 , comprising: a substrate 100; a source-drain doped layer 101 on the substrate 100; a channel column 102 located on the source-drain doped layer 101; The isolation layer 103, the top surface of the isolation layer 103 is lower than the top surface of the channel column 102; the gate structure located on the side wall of the channel column 102, the gate structure includes: a gate dielectric layer 104, located at the gate The work function layer 105 on the dielectric layer 104, and the gate layer 107 on the work function layer 105, part of the gate structure is also located on the surface of t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More