Method for forming semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve problems such as bulging, device performance degradation, defects, etc., and achieve the effect of reducing the number of defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

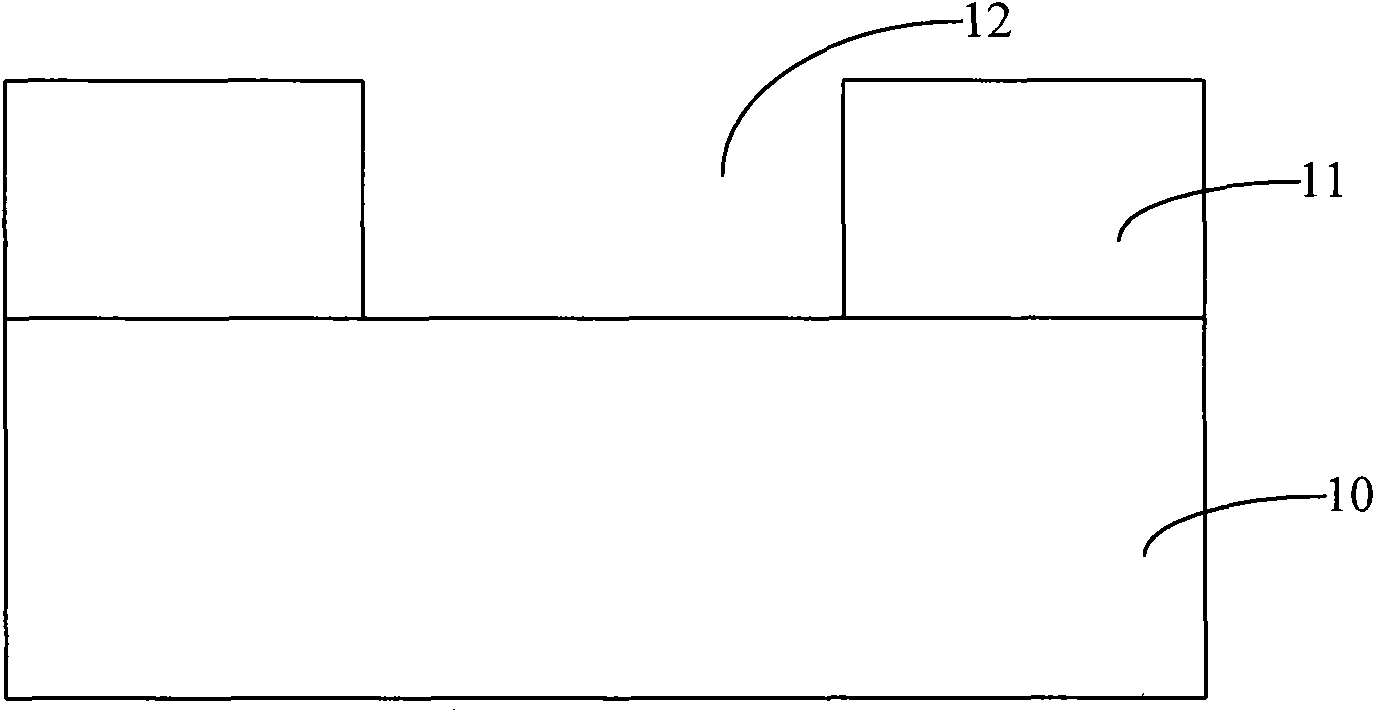

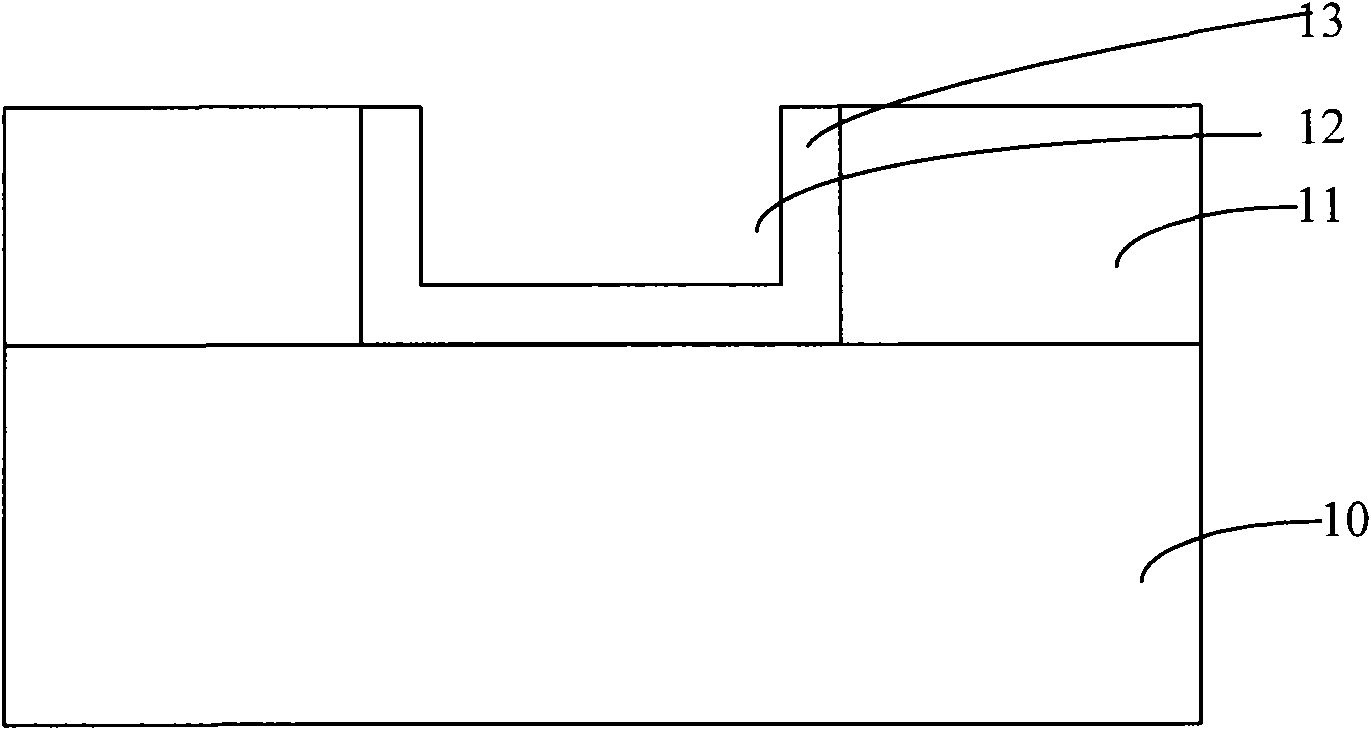

[0016] After a large number of experiments, the inventor of the present invention found that the metal layer formed on the semiconductor substrate does not match the material of the semiconductor substrate. The metal layer formed by the prior art usually has tensile stress. In the further development of the metal layer, a multi-layer film is usually formed on the surface of the metal layer, so that the stress of the metal layer is further expanded, and there will be a multi-step high temperature process after the metal layer is formed. The metal layer and the semiconductor substrate And the subsequent thermal expansion coefficients of the films formed on the surface of the metal layer are not the same. In the multi-step high temperature process, bulging and defects will occur on the surface of the metal layer, resulting in a decrease in device performance.

[0017] To this end, the present invention provides a method for forming a semiconductor device, Figure 5 It is a schematic ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More