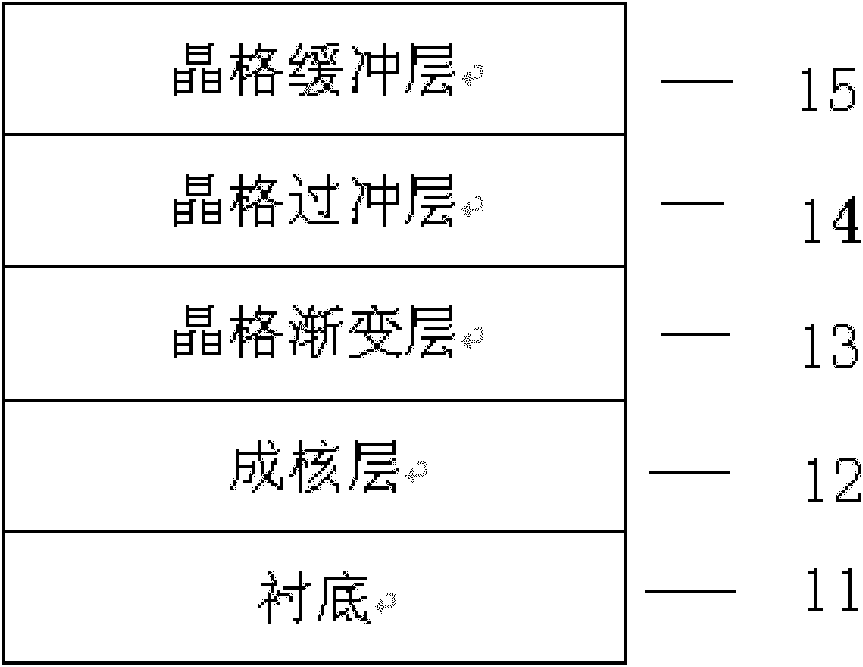

Method for manufacturing lattice graded buffer layer

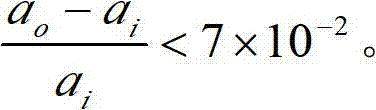

A graded buffer layer and graded layer technology, applied in the field of semiconductors, can solve the problems of high penetration dislocation density on the structure and device surface, the influence of heterojunction material interface materials and device performance, and the inability to eliminate mismatch well, etc. Achieve the effects of reducing dependencies, overcoming performance degradation, and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0025] A method for preparing a lattice gradient buffer layer, the steps are:

[0026] Step (1): use germanium (Ge) single crystal as substrate 11; the substrate material can be germanium, silicon, and III-V and II-VI group materials or their combination, including gallium arsenide, indium phosphide , Gallium phosphide, gallium nitride, gallium antimonide, etc.; the surface of the substrate can have (100), (110) or (111) crystallographic directions, or other exponential plane directions, and include those in the above directions to other directions Deflection angle of 0-15 degrees.

[0027] Step (2): Use existing epitaxial techniques such as metal organic chemical vapor deposition (MOCVD), molecular beam epitaxy (MBE) and liquid phase epitaxy (LPE) to perform epitaxial growth of materials; in order to make the core functional layer of the present invention— —The structure of the lattice-graded buffer layer is not affected by the defects of the substrate. First, a layer of material...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More