Semiconductor chip encapsulation structure and encapsulation method

A chip packaging structure and chip packaging technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of high cost, inability to reduce the area of the package body, and complex packaging methods. Improved electrical performance, improved flexibility and effectiveness, and simplified packaging process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

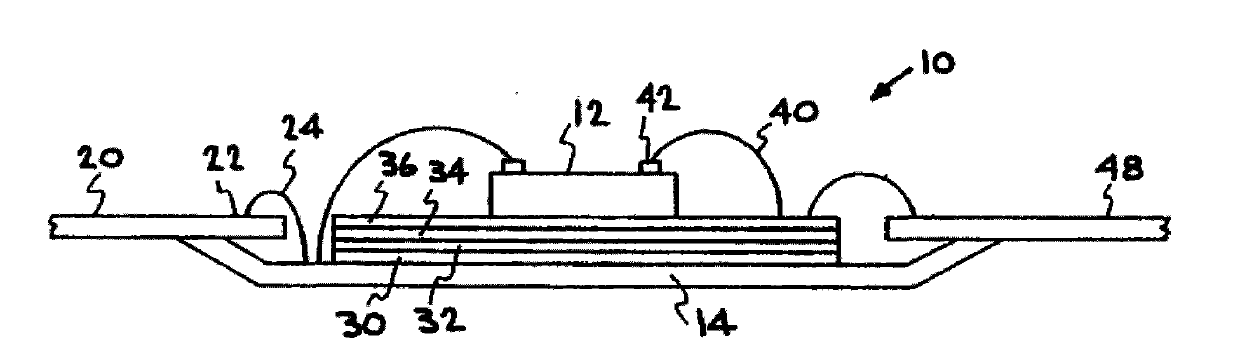

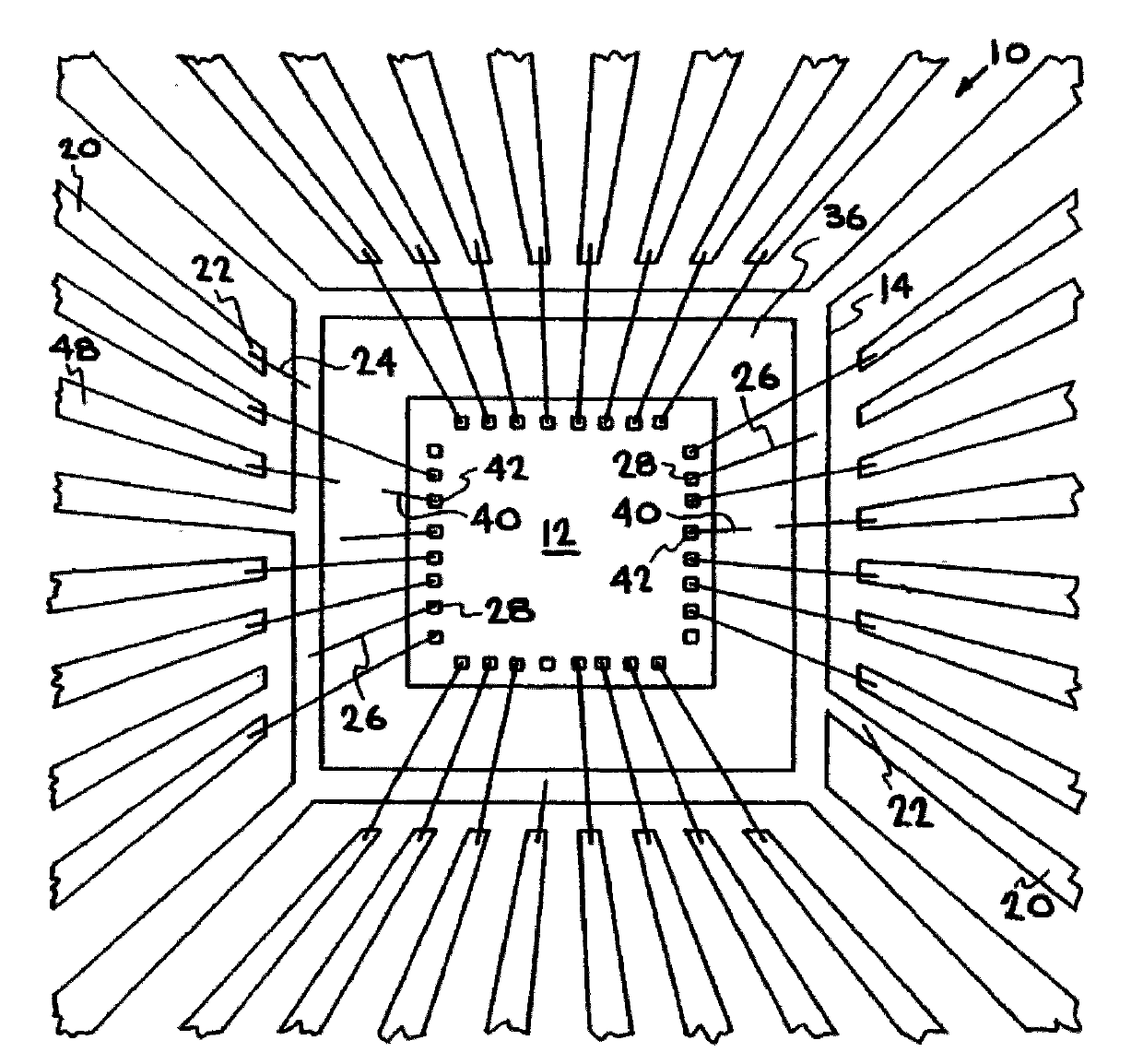

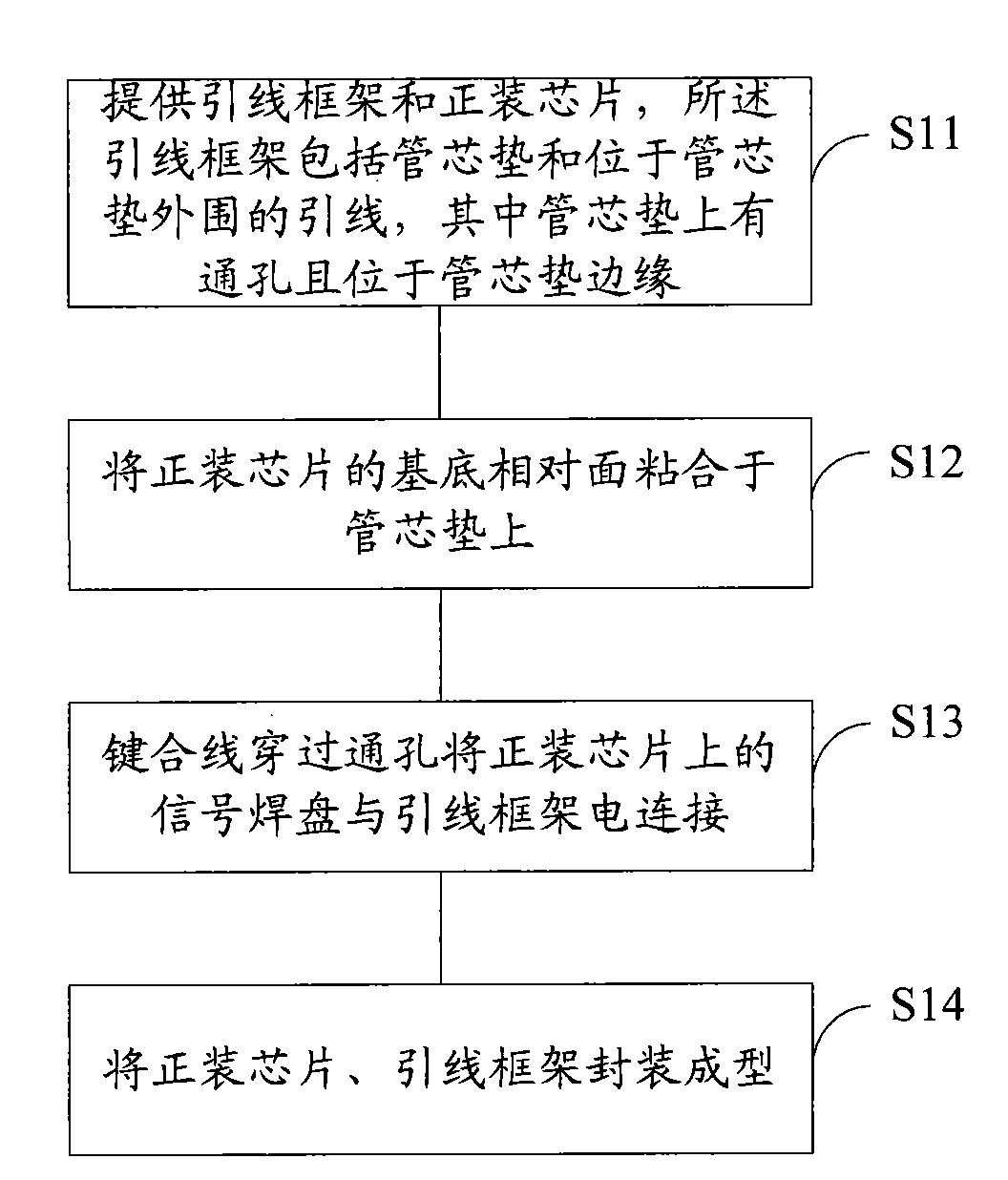

[0033] The present invention has through holes on the die pad, and the through holes are located at the edge of the die pad, so that subsequent chips mounted on both sides of the die pad can be placed in the same direction. Therefore, the internal wiring of the chips on both sides of the die pad is symmetrical, so that the semiconductor The chip packaging process is simplified, which improves the flexibility and effect of the manufacturing process; the through holes on the die pad are used, and the bonding wire can be connected up, down, left, and right, which is equivalent to providing a multi-layer connection surface function, which greatly reduces manufacturing cost. In addition, the bonding wires pass through the through holes to electrically connect the signal pads on the front-mounted chip with the lead frame, without the need to form other conductive layers on the die pads, which not only reduces manufacturing costs, but also achieves low function / grounding Impedance imp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com