Embedded sram structure and chip

一种静态随机存取、存储器芯片的技术,应用在静态存储器、数字存储器信息、信息存储等方向,能够解决装置控制能力及数据稳定性影响等问题,达到提高静态噪声边限及晶体管匹配性、改善可靠度的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The following describes the preferred embodiment of the present invention. Each embodiment is used to illustrate the principles of the present invention, but not to limit the present invention. The scope of the invention should be determined by the terms of the appended claims.

[0034] As used herein, the term "gate poly" refers to any wire capable of forming the gate of a transistor, although the wire can still be a conductive material (eg, metal, metal silicide, metal nitride, or combinations thereof) of amorphous silicon material.

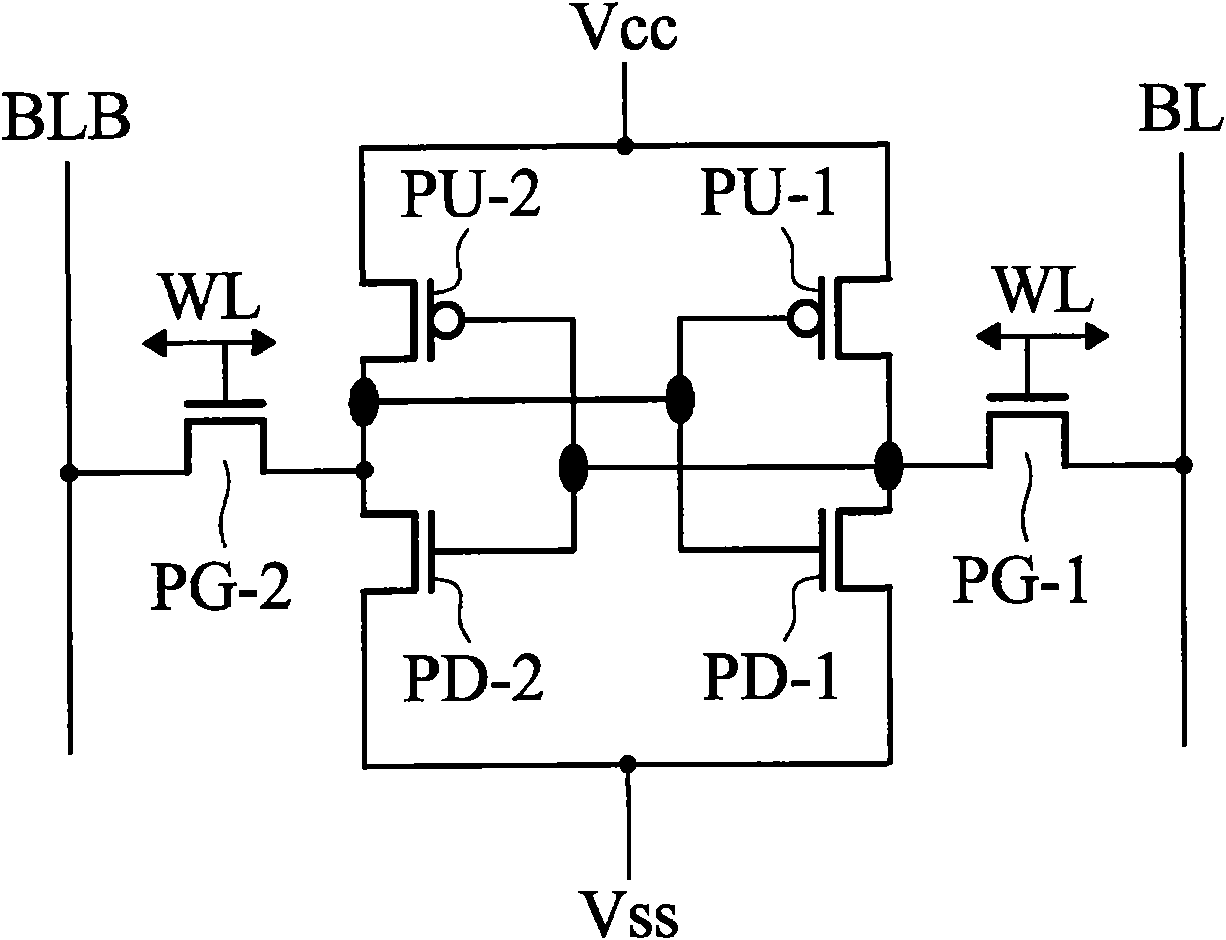

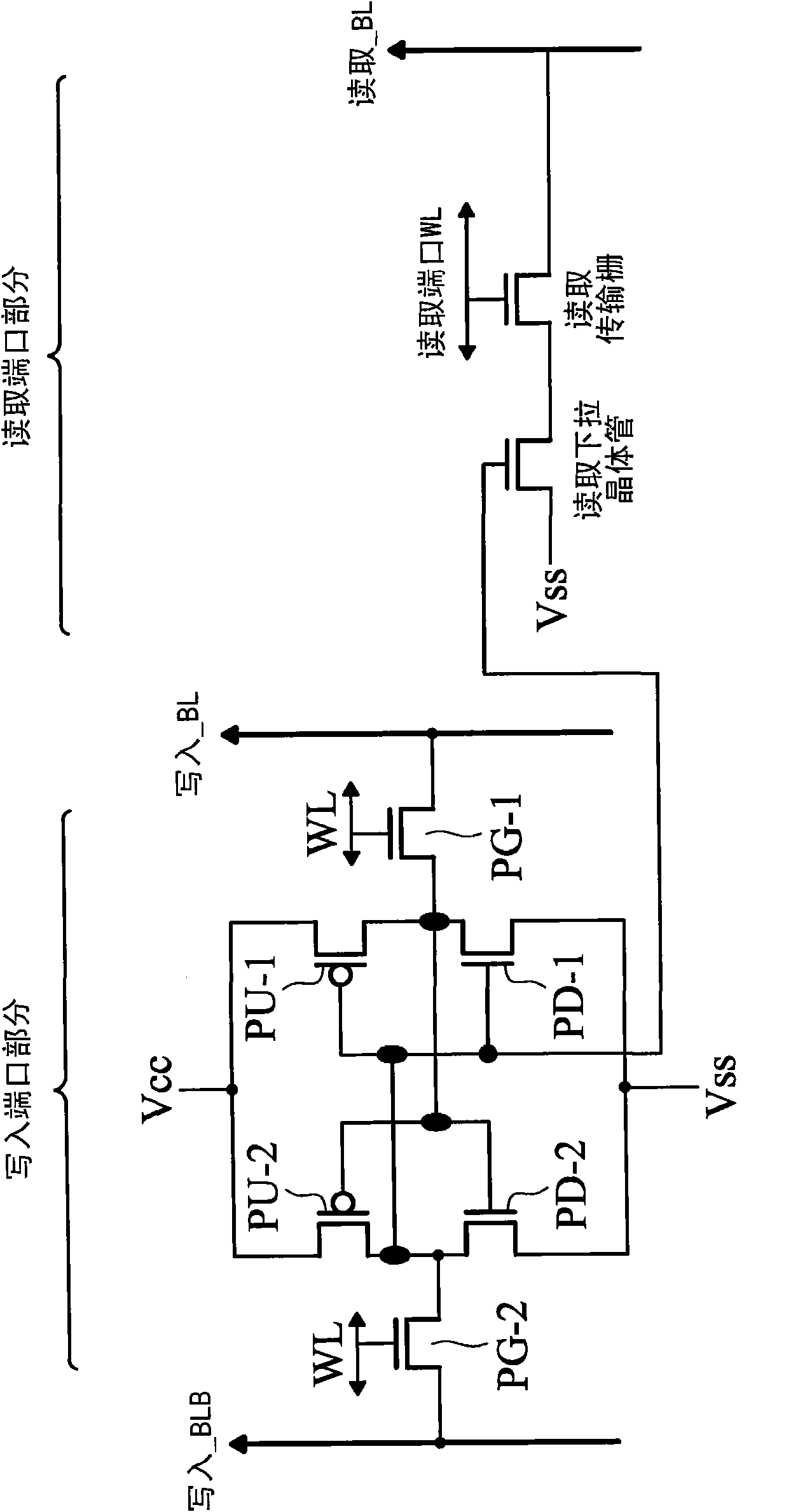

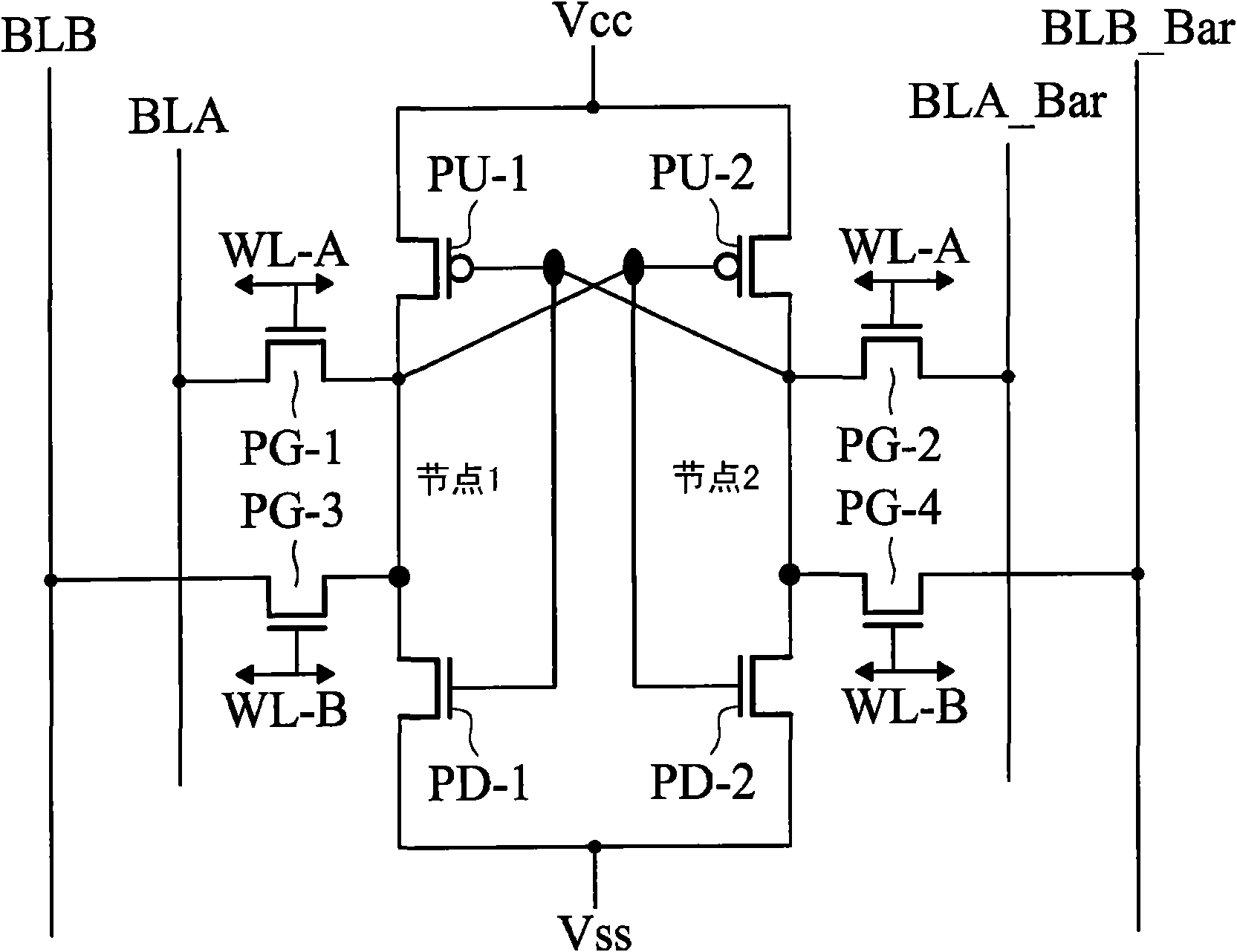

[0035] As is known to those of ordinary skill in the art familiar with SRAM design, one way to measure the performance of an SRAM is to measure its cell array speed. The bit lines are connected to sense amplifiers for signal comparison. The voltage difference between the bit lines BL and BLB determines the speed of the SRAM. There are two ways to improve the BL / BLB differential voltage, one is to increase the lattice current, and the ot...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More