Method and structure for filling clearances among stacked multi-layer wafers

A technology of multi-layer wafers and stacked structures, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc. It can solve the problems of height difference and inability to dispense and fill, so as to avoid short circuits and improve production efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

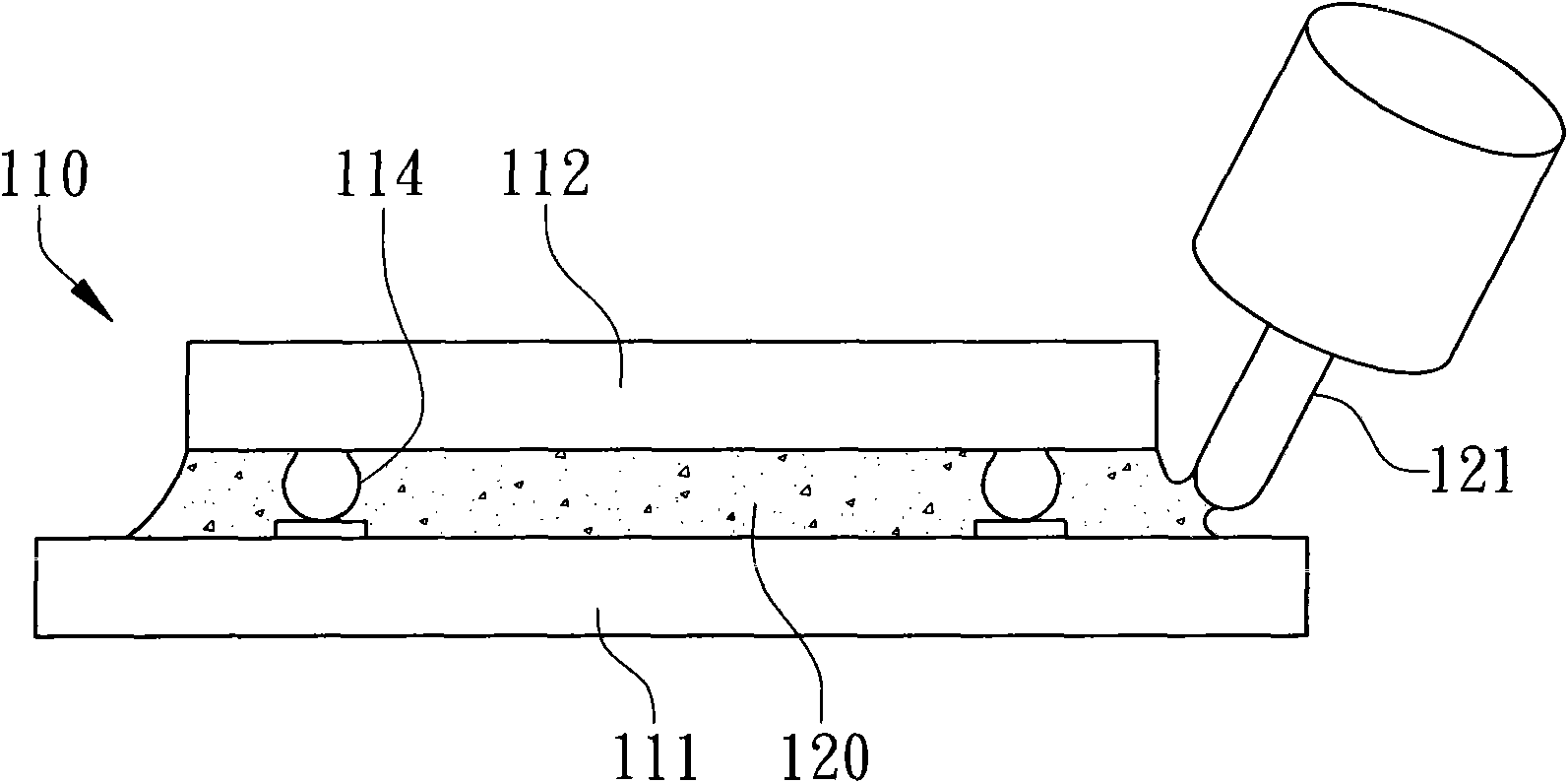

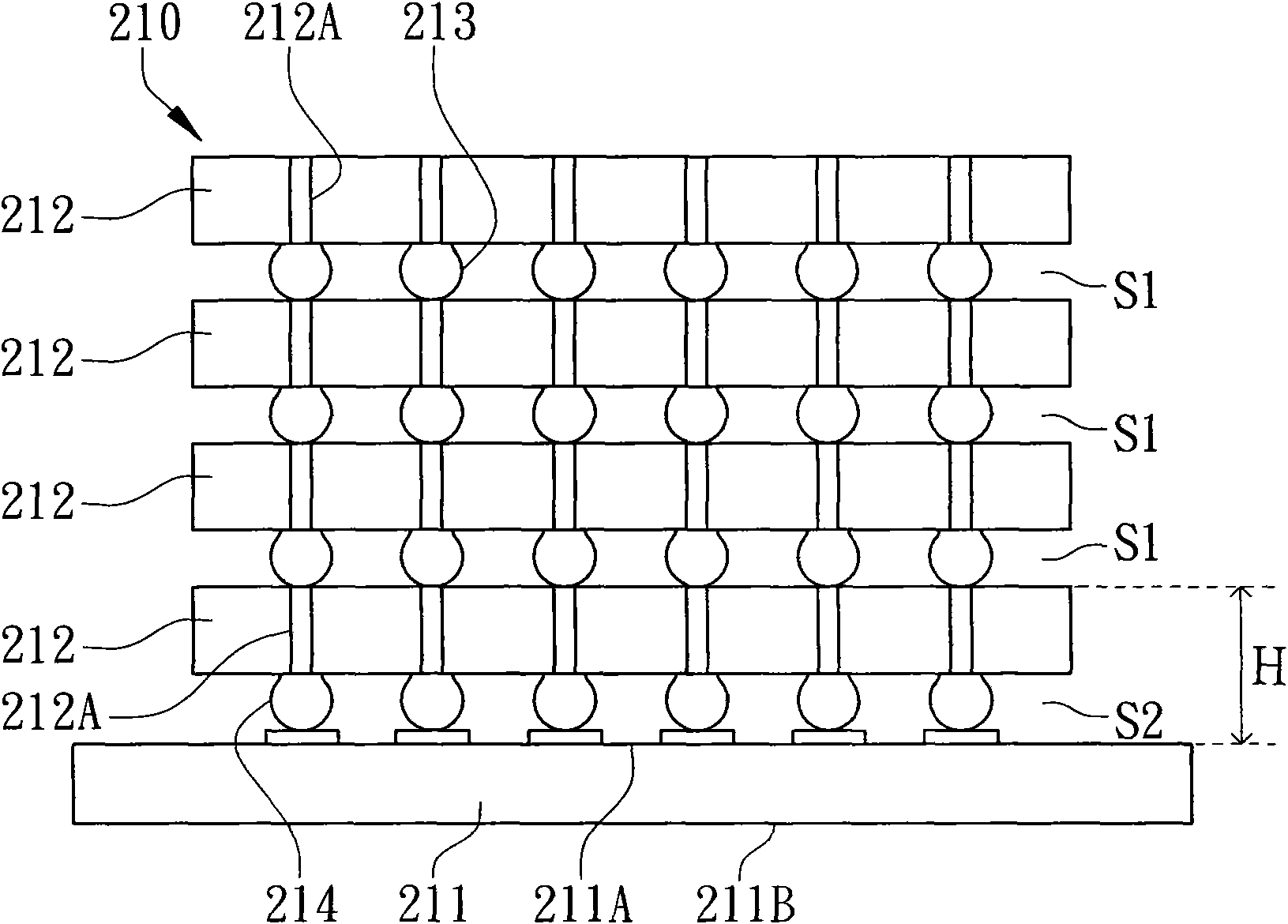

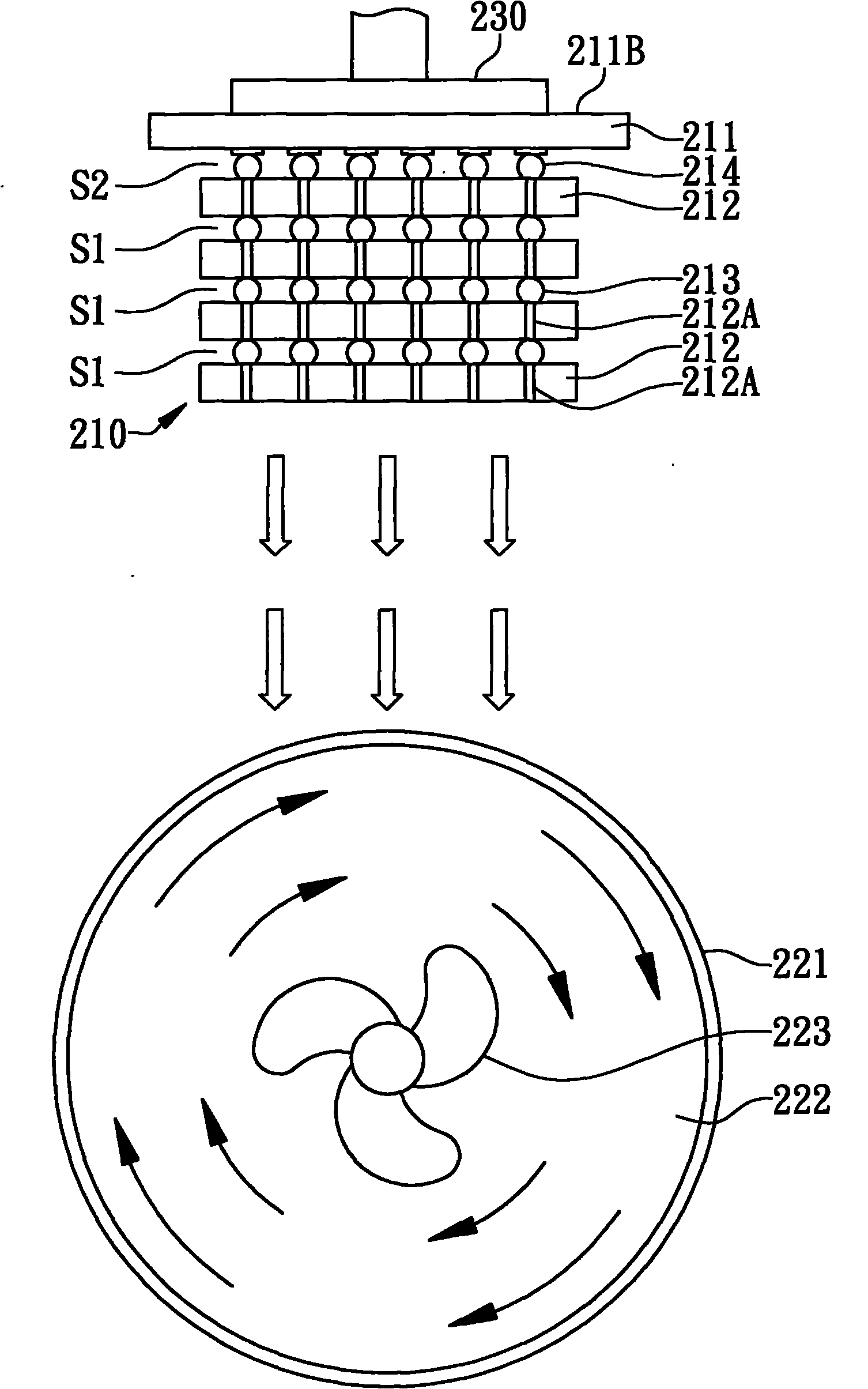

[0053] In order to further explain the technical means and effects of the present invention to achieve the intended purpose of the invention, the specific implementation methods, The method, steps, structure, features and effects thereof are described in detail below.

[0054] Some embodiments of the present invention will be described in detail as follows. However, in addition to the following descriptions, the present invention can also be widely implemented in other embodiments, and the protection scope of the present invention is not limited by the embodiments, which shall prevail by the protection scope of the claims. Moreover, in order to provide a clearer description and an easier understanding of the present invention, various parts in the drawings have not been drawn according to their relative sizes, and some dimensions have been exaggerated compared with other relevant dimensions; irrelevant details have not been completely drawn. are drawn for the sake of simplici...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com