Array structure of reconfigurable operators

An array structure and operator technology, which is applied in the field of the array structure of reconfigurable operators to achieve the effect of speeding up the design speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described in detail below through specific embodiments in conjunction with the accompanying drawings.

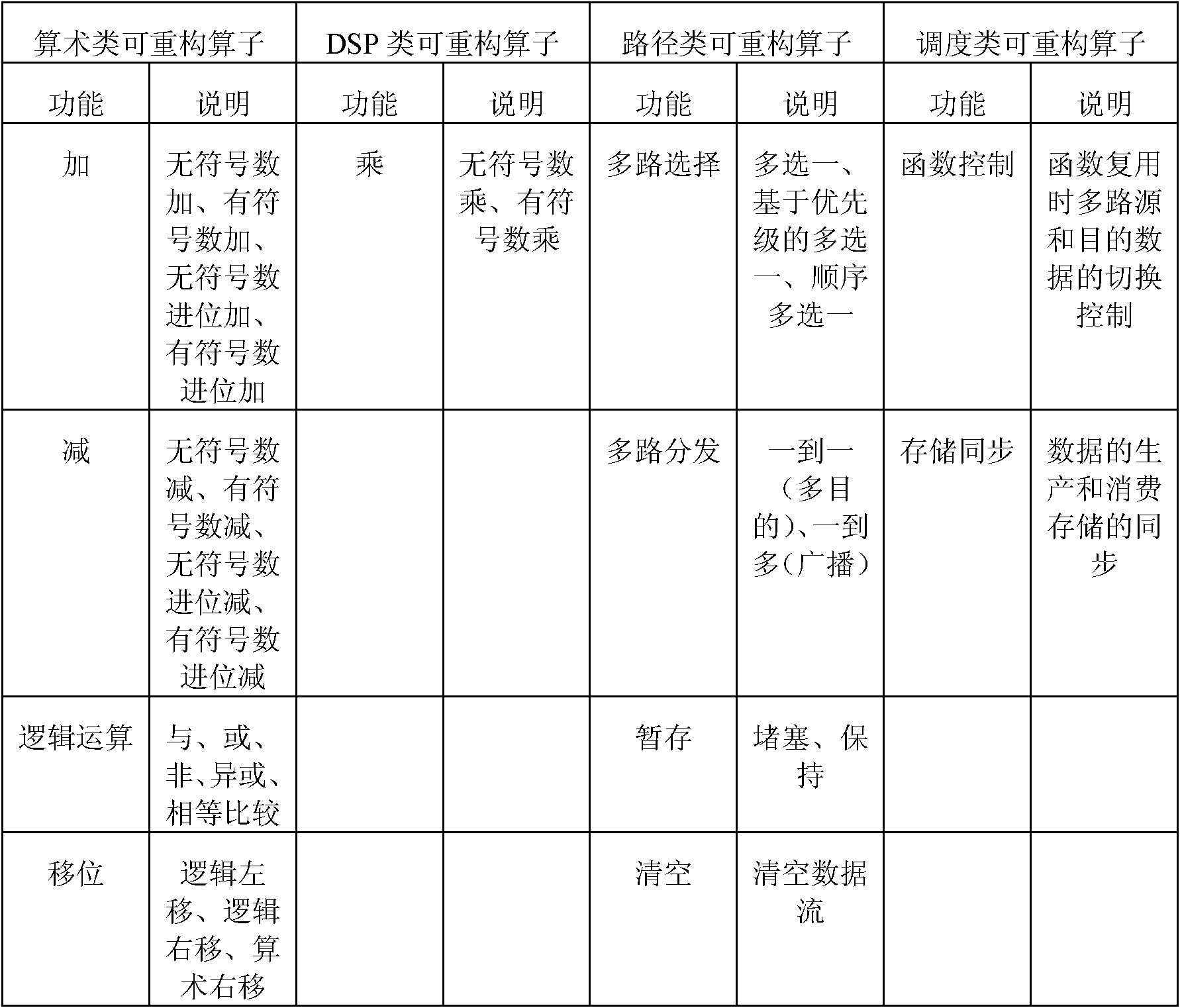

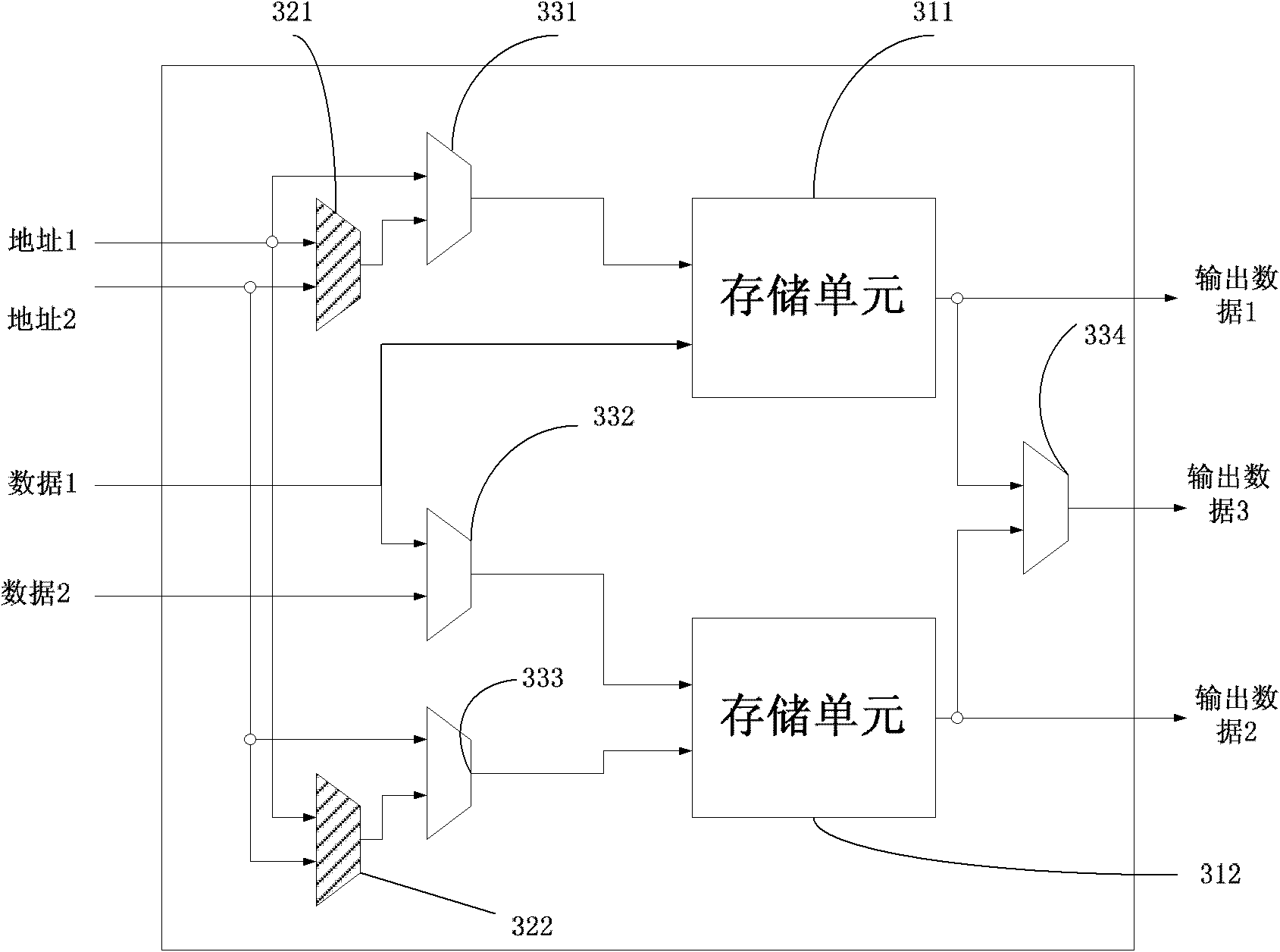

[0024] The array structure involved in the present invention includes logic units for realizing logic functions, connection units for realizing connection relations, and input and output units for realizing communication with external signals. The configuration information is loaded into the array structure through the input and output unit, and the logic function of the logic unit and the connection relationship of the connection unit are configured, so that the array structure has programmability. Attached below Figures 1 to 6 The specific implementation process of the present invention is described in detail:

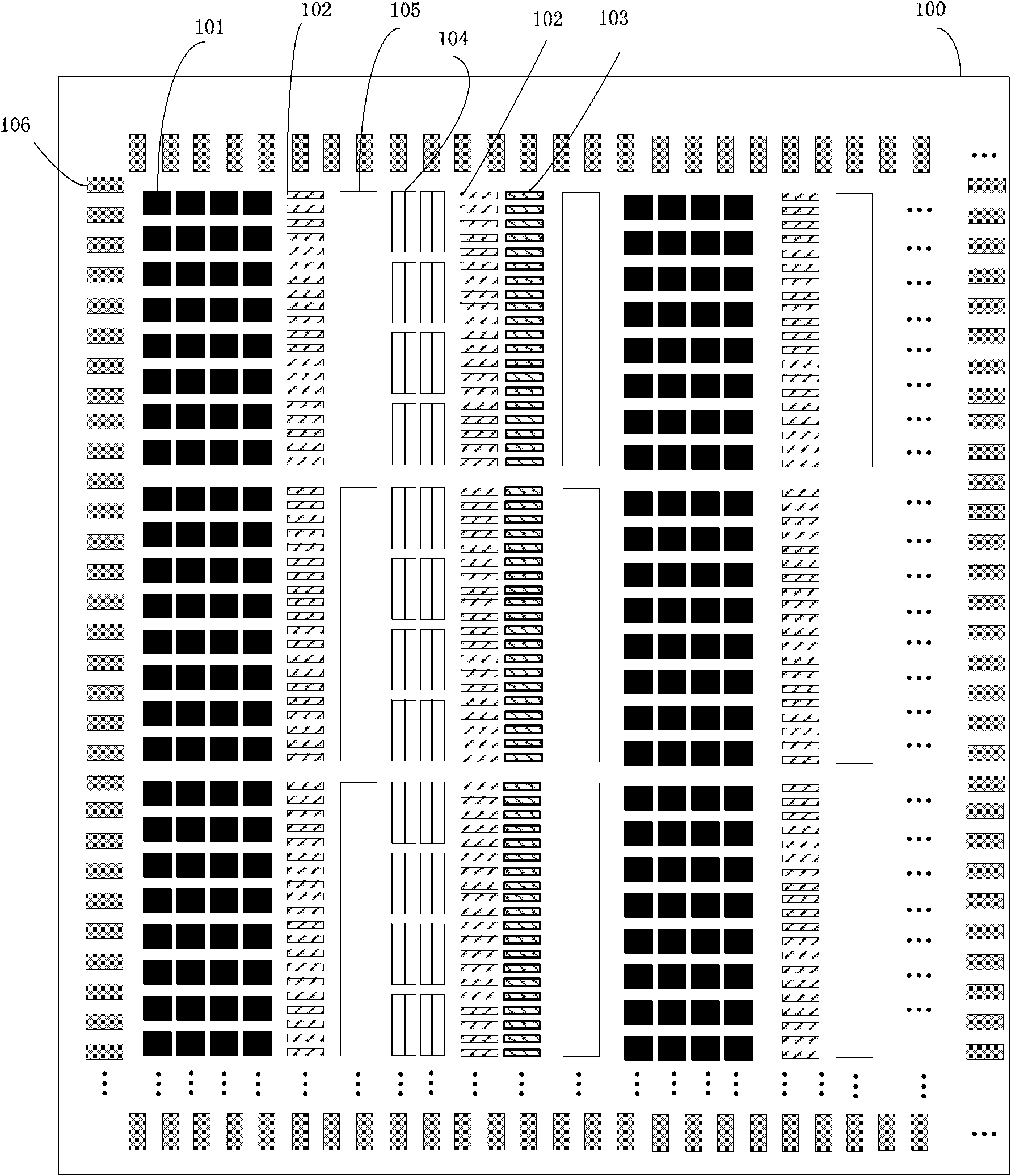

[0025] Please refer to figure 1 , an array structure 100 of a reconfigurable operator, including a logic unit, a connection unit, and an input and output unit. The input and output units are distributed around the lo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More