Method and circuit for testing multi-clock domain

A technology with multiple clock domains and test methods, applied in the direction of measuring electricity, measuring electrical variables, electronic circuit testing, etc. The effect of testing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

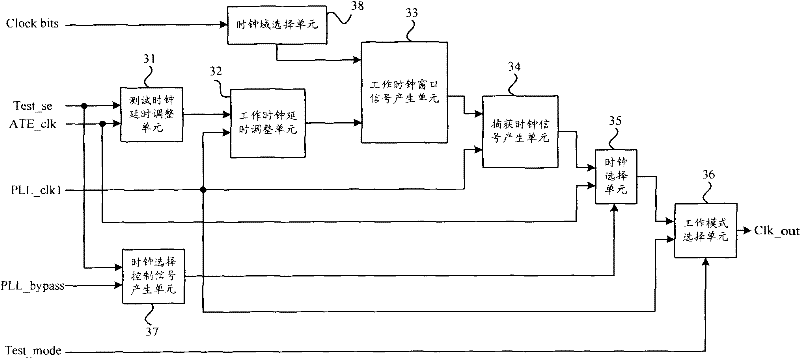

[0034] The technical solutions of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0035] The present invention considers that when testing a chip in the prior art, due to the existence of multiple clock domains, each clock domain needs to be tested separately, and there are problems such as complicated testing process and inability to correctly test cross-clock domain circuits, etc., and proposes a A multi-clock domain testing method, the core idea of this method is to set the clock domain selection signal, and use this signal to control one or more clock domains as clock domains that can be tested. In this way, not only can multiple clock domains work simultaneously, In order to improve the test efficiency, and can eliminate the mutual influence between different clock domains, and solve the problem of cross-clock domain circuit testing.

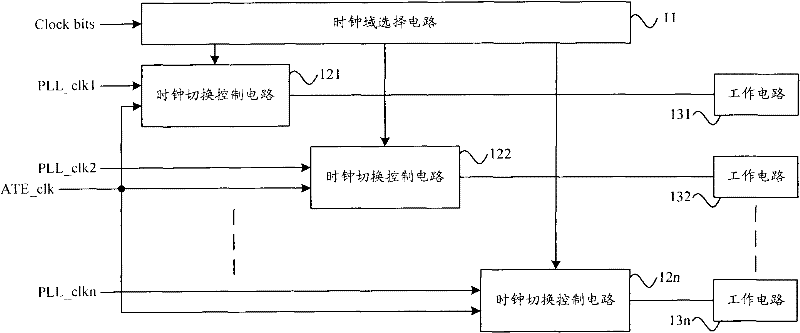

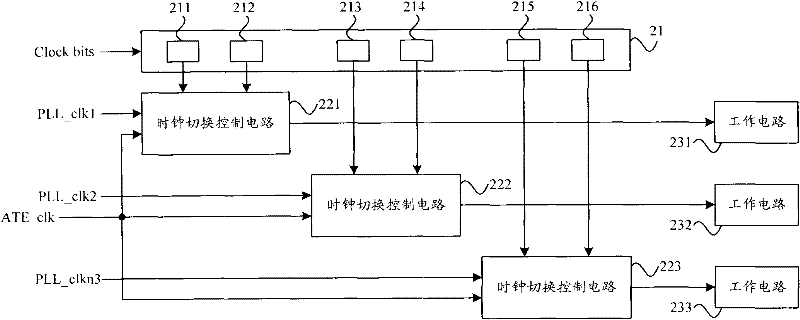

[0036] figure 1 Shown is a structural block d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More