Method for improving error correction capacity and related memory device and controller of memory device

An error correction and memory device technology, applied in the field of error correction, can solve the problems of increased cost of the error correction code engine, inability to take into account the operation performance, system resource usage control, waste, etc., so as to take into account the system resource usage control and improve error correction ability, taking into account the effect of operational efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

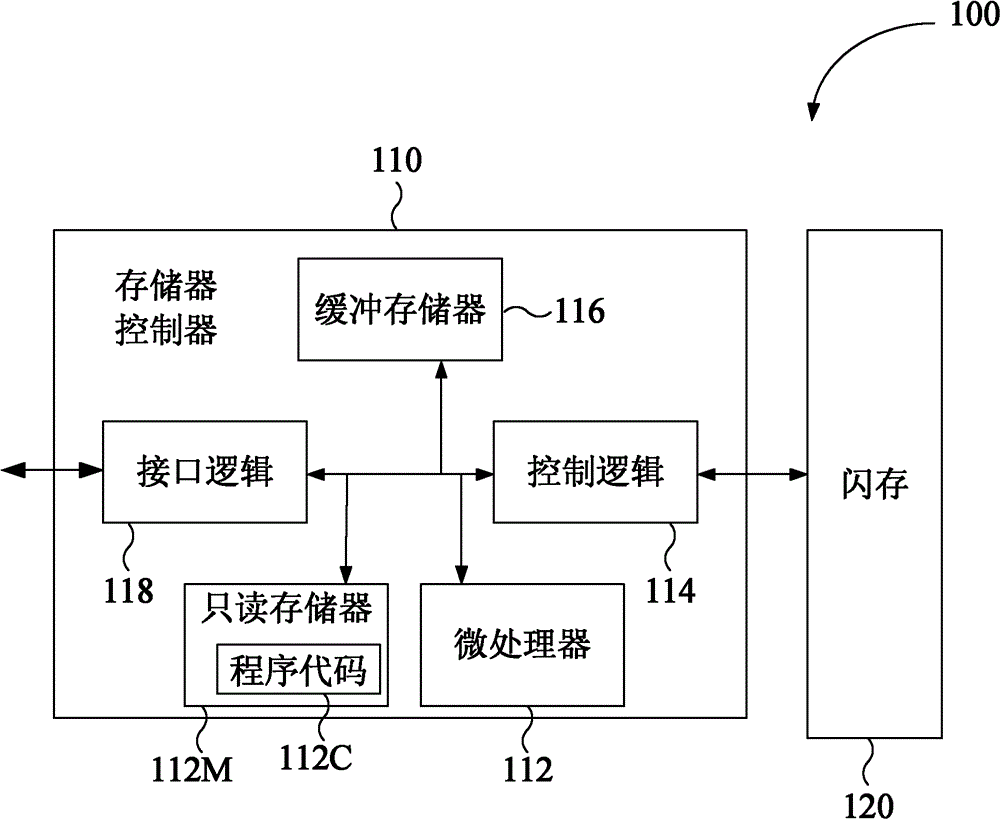

[0053] Please refer to figure 1 , figure 1 It is a schematic diagram of a memory device 100 according to a first embodiment of the present invention, wherein the memory device 100 in this embodiment is especially a portable memory device (eg, a memory card conforming to SD / MMC, CF, MS, XD standards) ). The memory device 100 includes: a flash memory (FlashMemory) 120; and a controller for accessing the flash memory 120, wherein the controller is such as a memory controller 110, and the memory device 100 (especially the controller such as The error correction capability of the memory controller 110) can be improved without increasing the number of encoding / decoding bits of an Error Correction Code Engine (ECC Engine). According to this embodiment, the memory controller 110 includes a microprocessor 112 , a read only memory (ROM) 112M, a control logic 114 , a buffer memory 116 , and an interface logic 118 . The ROM is used to store a program code 112C, and the microprocessor 1...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap