Optimizing method of analogue integrated circuit design

An optimization method and integrated circuit technology, applied in computing, electrical digital data processing, instruments, etc., can solve the problems of sensitivity to parasitic effects of analog integrated circuits, failure to consider connection parasitic effects, long design cycle, etc., to improve optimization speed, Effects of shortening the design cycle and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

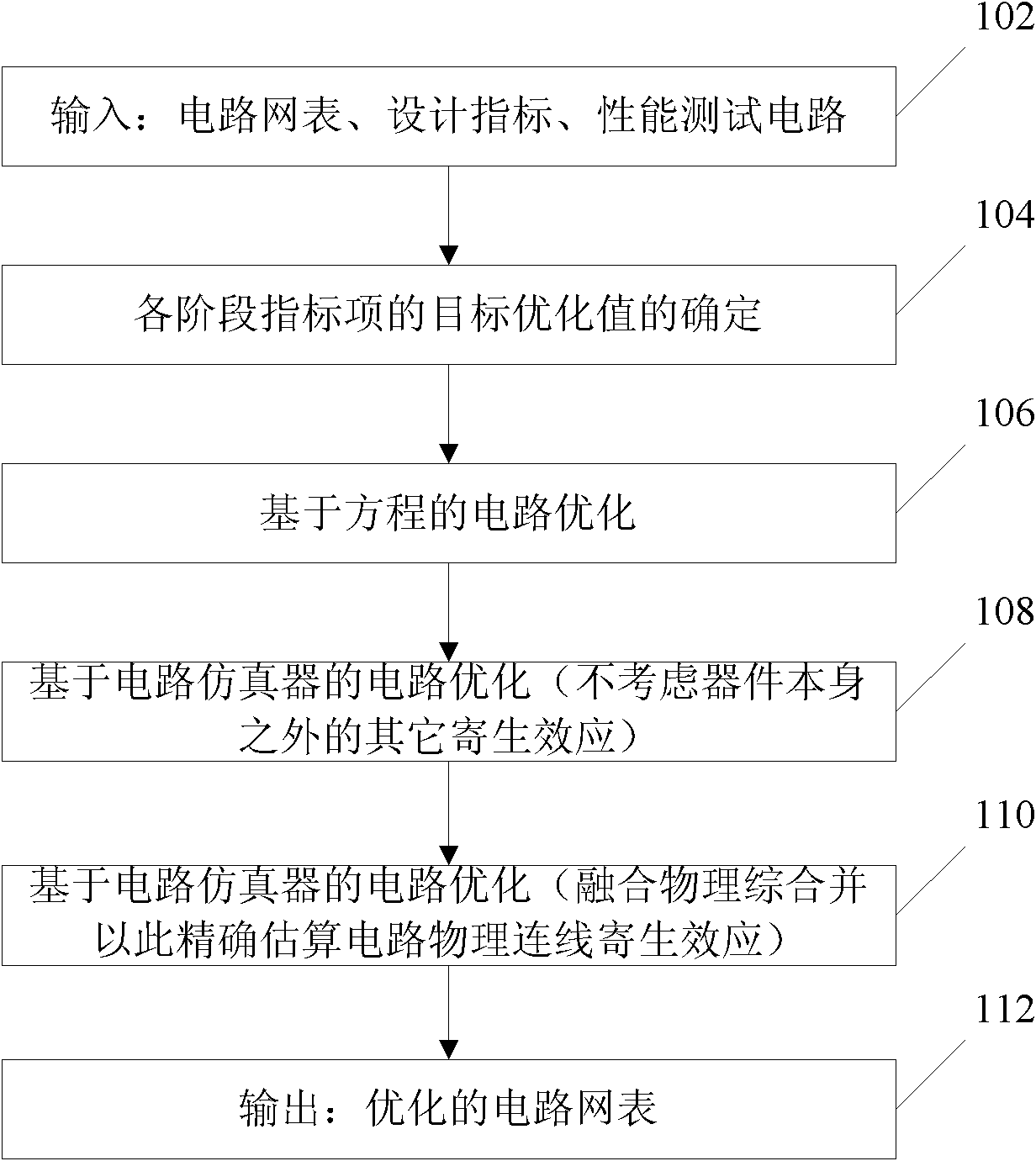

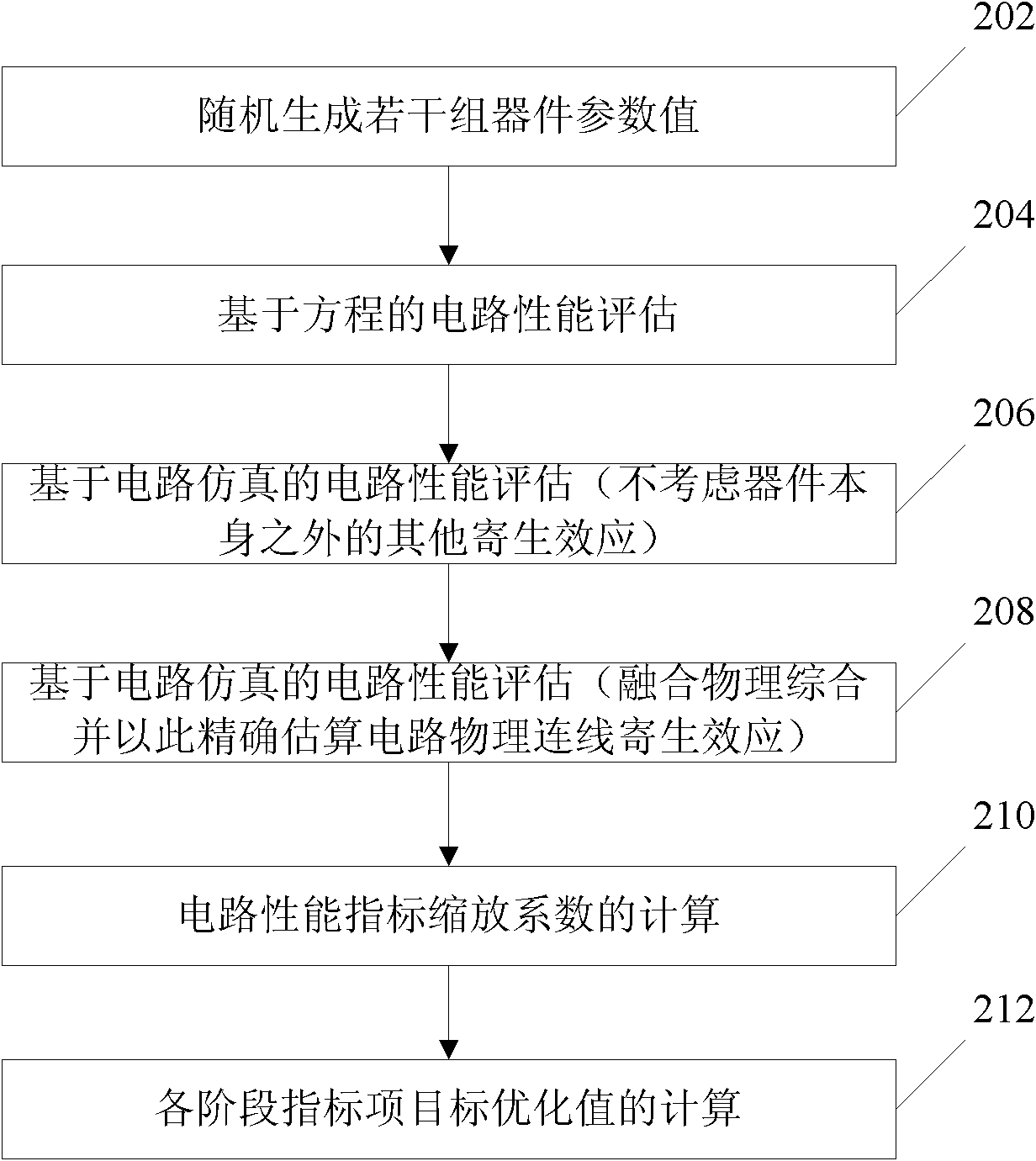

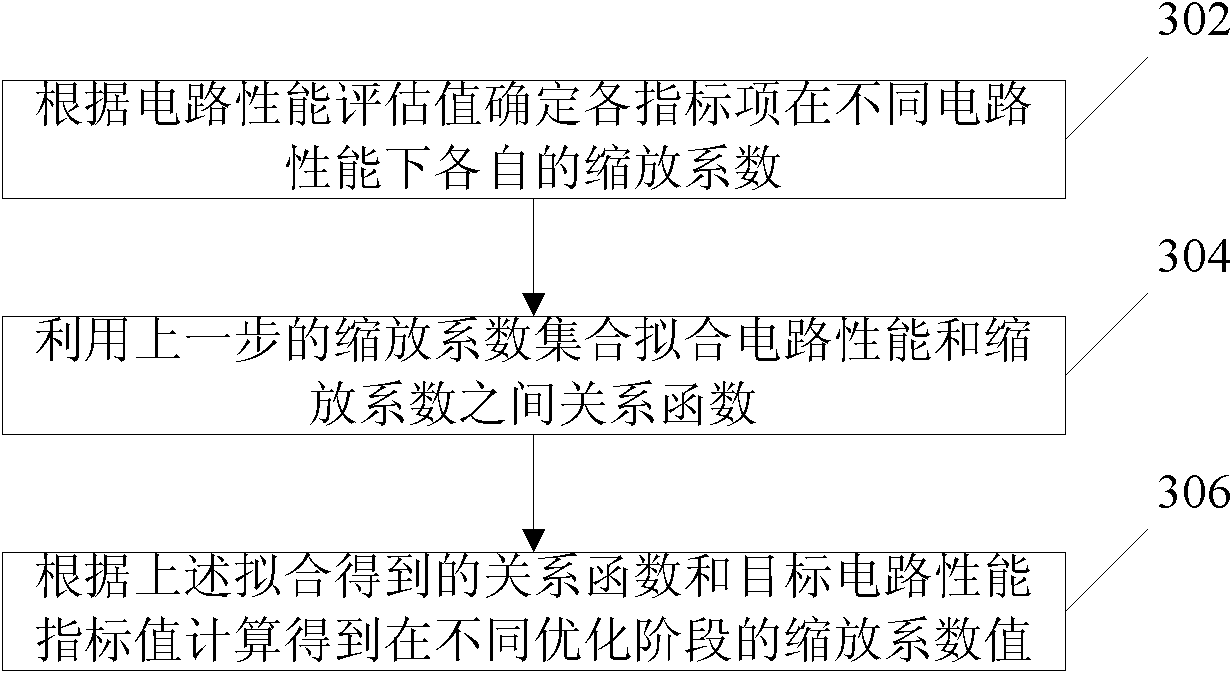

[0031] The present invention proposes a computer-aided automatic optimization method aimed at improving work efficiency for analog integrated circuit design, which specifically includes: determining the target optimization value of the circuit index item at each optimization stage before the analog circuit design optimization, using the method based on The circuit optimization method based on the equation realizes the circuit optimization of the first stage, and the circuit optimization method based on the circuit simulator that does not consider the connection parasitic effect realizes the circuit optimization of the second stage, and uses the fusion of physical synthesis and accurate estimation of the parasitic effect of the physical connection of the circuit The circuit optimization method based on circuit simulator realizes the third stage of circuit optimization. In particular, circuit optimization is controlled by using respective target optimization values of circuit p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More