Structure with alignment mark and manufacture method for stacking device

A technology for alignment marks and manufacturing methods, which is applied in the field of semiconductor technology and its formed structures, can solve problems such as hindering device operation, and achieve the effects of increasing production capacity, improving technology, and relieving stress and strain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The manufacture and use of the embodiments of the present invention are described below. It should be readily appreciated, however, that the embodiments of the invention provide many suitable inventive concepts that can be implemented in a wide variety of specific contexts. The specific embodiments disclosed are only used to illustrate the making and use of the present invention in specific ways, and are not intended to limit the scope of the present invention.

[0030] A specific background of embodiments of the present invention is described below, that is, alignment marks formed during processing of chips in a stacked device. However, the above-described embodiments are also applicable to an interposer or another structure that uses alignment marks during processing.

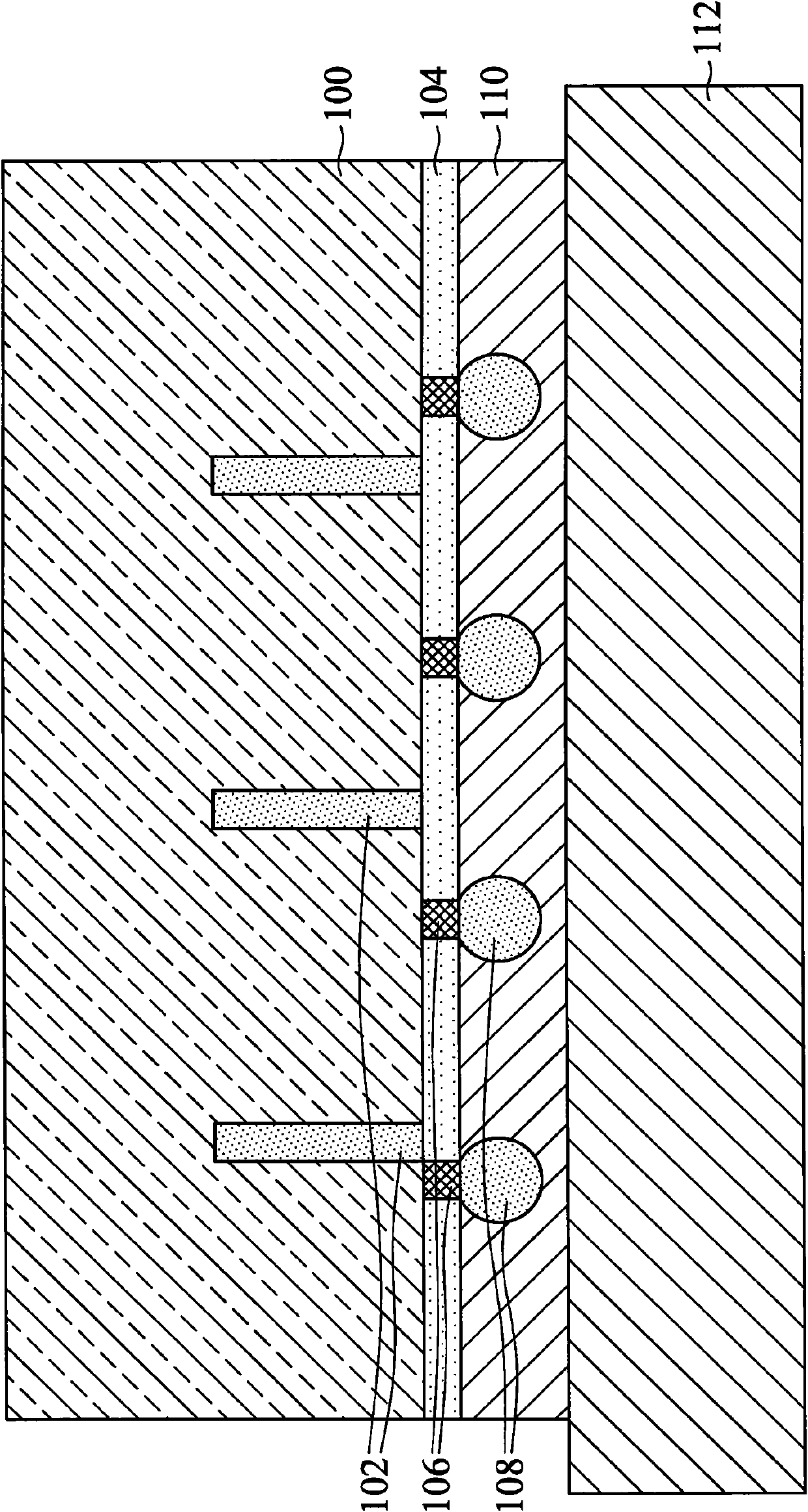

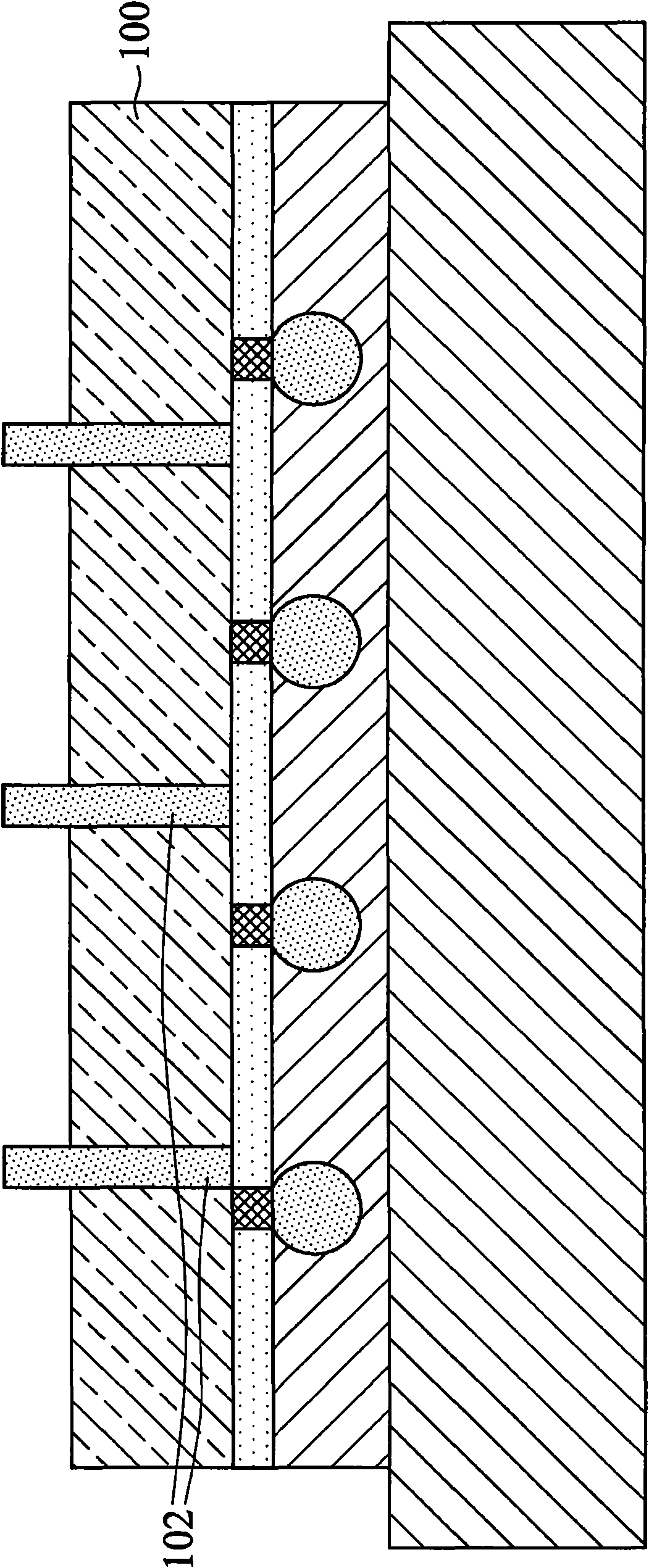

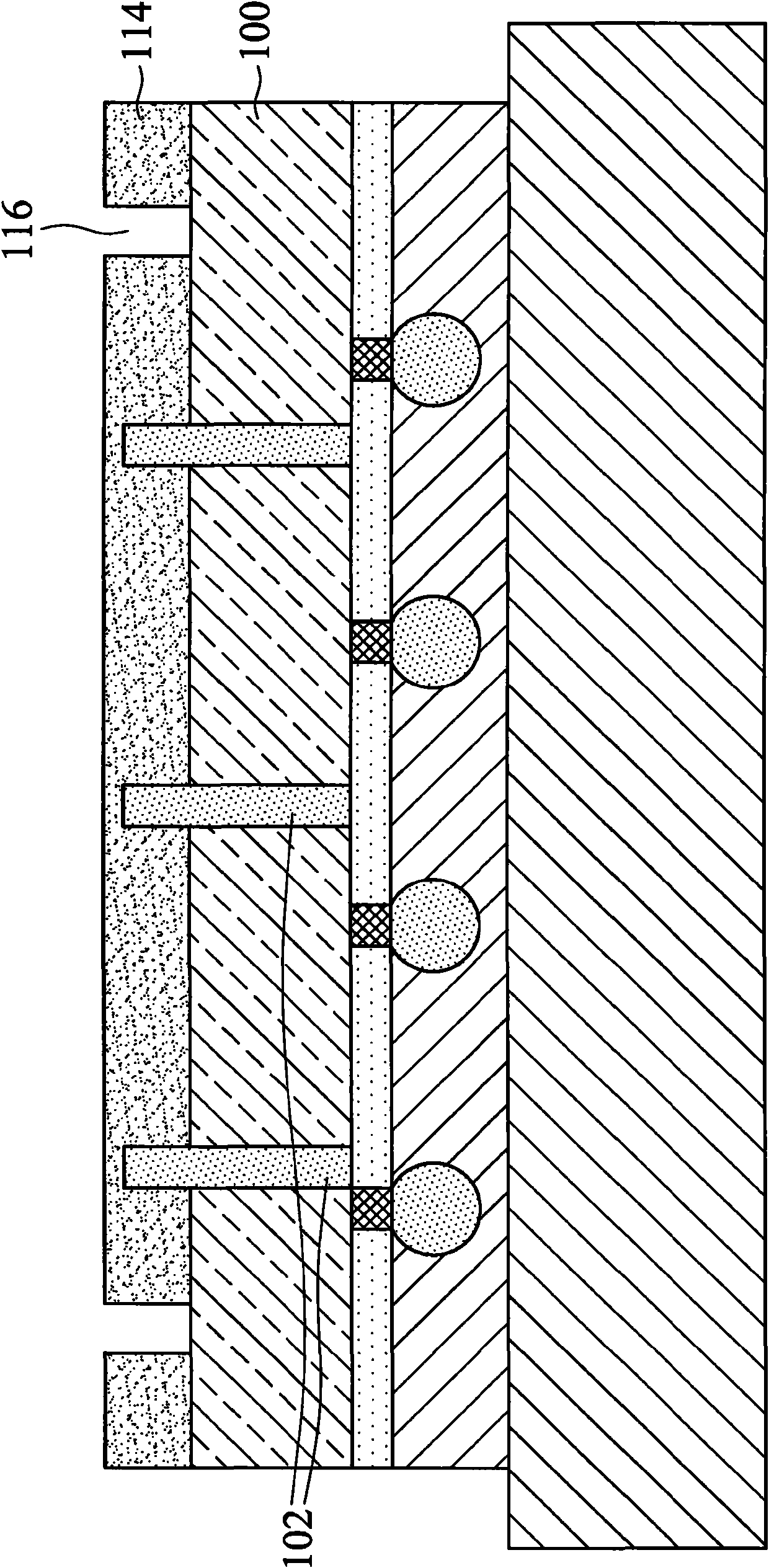

[0031] Figure 1A to Figure 1H A method for manufacturing an alignment mark for a stacked device according to an embodiment of the present invention is presented. figure 2 shown by Figure 1A to Fig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More