Optimization of static timing analysis of coupling interconnects

A static timing analysis and interconnection technology, applied in the field of microelectronics, which can solve the problems of inaccurate calculation results, low execution efficiency, and large calculation scale.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described below in conjunction with the accompanying drawings.

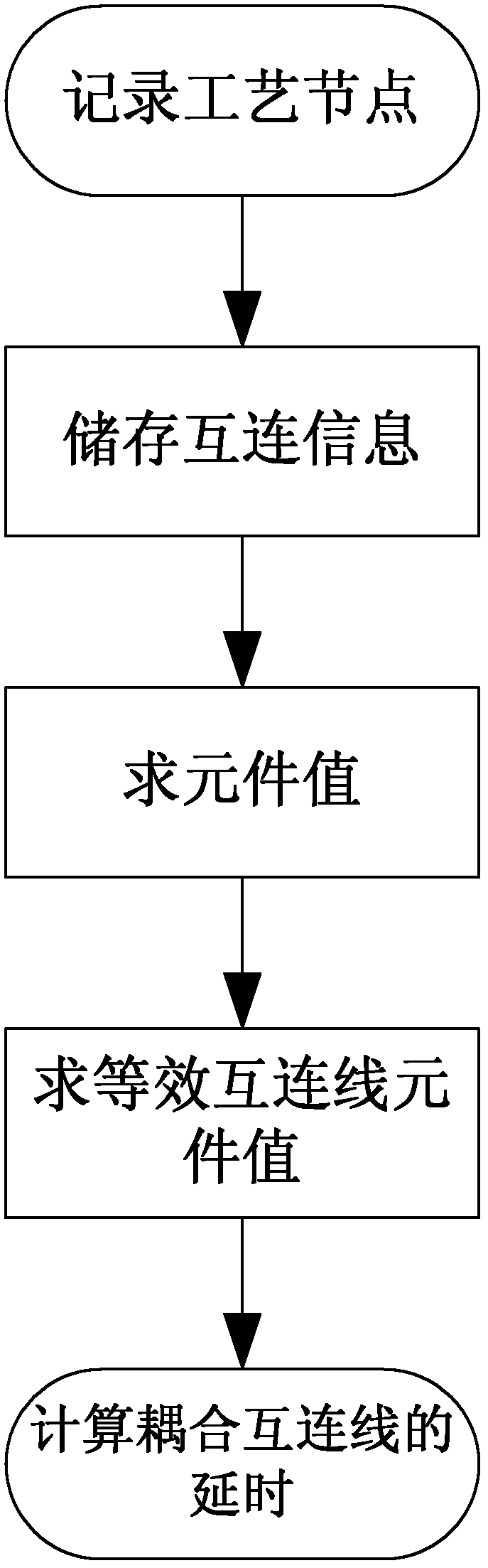

[0037] refer to figure 1 , the concrete realization of the present invention is as follows:

[0038] Step 1. Record the process node.

[0039] Read the process node in the record file from the top-level planning file in the early stage of integrated circuit design. The process node includes: the length of the interconnection line, the width of the interconnection line, the thickness of the interconnection line, the spacing of the interconnection line, and the thickness of the dielectric layer Interconnect parameters such as thickness.

[0040] Step 2. Store interconnection information.

[0041] Substitute the process node into the ITRS data table of the international standard process library, read the interconnection line parameters corresponding to the process node and the two ramp input voltage parameters, and the ramp input voltage parameters include the starting...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More