On-chip network mapping method based on ant-colony chaos genetic algorithm

A technology of chaotic genetics and network-on-a-chip, applied in the field of network-on-chip mapping based on ant colony chaotic genetic algorithm, can solve problems such as inability to meet the communication requirements between multi-cores

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

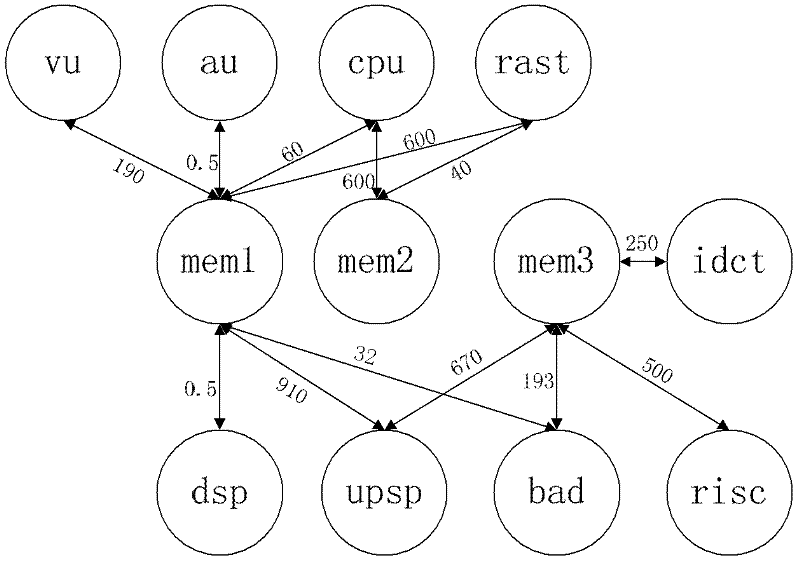

[0079] To verify the invention, the algorithm is applied to the mapping problem of MPEG4 decoder. MPEG4 decoder can be decomposed into 12 tasks, such as image 3 As shown, and then they are handed over to 12 IP cores for execution respectively. The mapping problem at this time is how to place these 12 IP cores on a NoC with a scale of 3x4.

[0080] Before formally applying the present invention to solve this problem, we need to define the mathematical expression of the objective function cost.

[0081] First, the system energy consumption is defined as:

[0082] E ( C ) = Σ i = 1 N Σ j = 1 N w i , j × h ...

Embodiment 2

[0094] In order to fully reflect the advantages of the present invention, a series of random task graphs are generated, and the NoC is mapped and optimized with emphasis on different optimization objectives (λ=1, 0.5, 0), and then the mapping results are carried out with the standard ant colony algorithm compared. In this embodiment, the definition of the objective function still adopts the formula (19) in Embodiment 1. The end result is as Image 6 shown. Image 6 The comparison results of communication energy consumption and link load variance of each mapping scheme with standard ant colony algorithm are shown when λ=1, 0.5, 0. It can be seen from the figure that the present invention is obviously superior to the traditional ant colony algorithm. When λ=1, the cost of the mapping scheme is 11% lower than that of the reference scheme; when λ=0.5, the cost of the mapping scheme is 4% lower than that of the reference scheme; when λ=0, the cost of the mapping scheme is 1% low...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More