A method for efficient utilization of rs error correction and detection algorithm in flash memory controller

A flash memory controller and error correction and detection technology, which is applied in the field of efficient utilization of RS error correction and detection algorithm, can solve the problems of high resource occupancy rate and low resource o Excellent error detection performance and extended service life

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

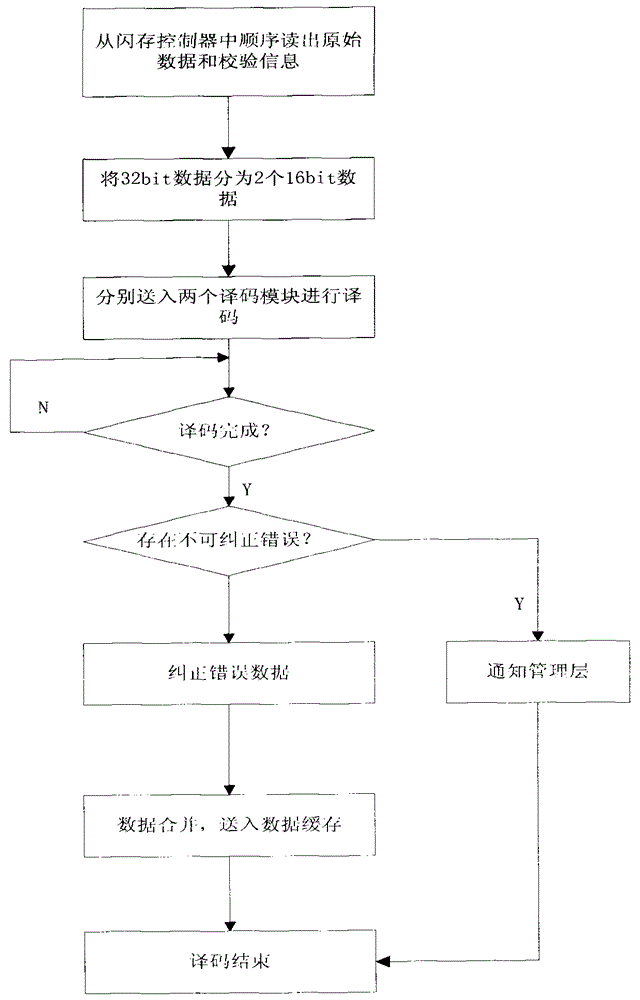

[0034] The error correction and detection module of the present invention adopts the RS code on the GF(2^8) field, and each symbol is 8bit (1 byte), wherein the original data length is 128 bytes, and the check information length is 2 bytes, correcting 1 byte error; for 512 bytes of data, 8 bytes of check information will be generated to correct 4 byte errors.

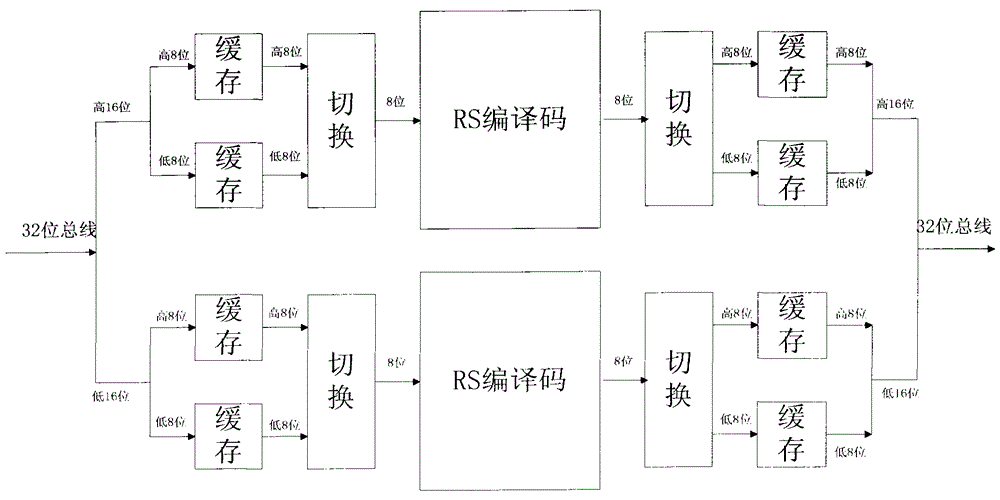

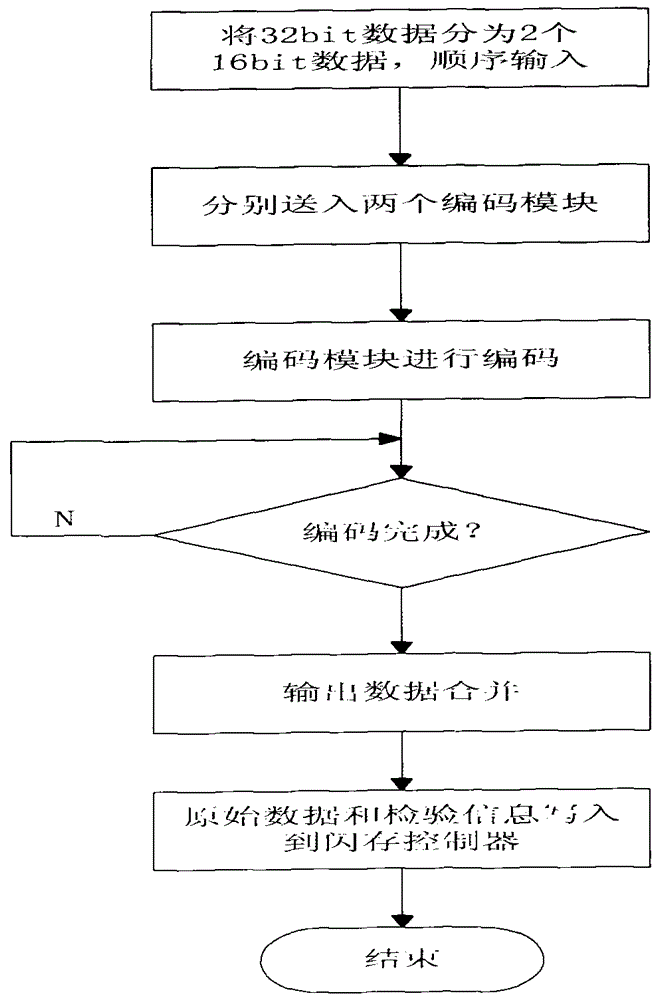

[0035] Structurally, the RS error correction and detection module adopts a combination of parallel and serial, such as figure 1 As shown, the 32-bit data line is first divided into high 16 bits and low 16 bits, and sent to two RS modules respectively, then each RS error correction algorithm module only needs to complete the encoding and decoding calculation of the 16-bit data interface. For 16-bit wide data, it is first given to a 16-bit wide cache. When the data in the cache is valid, use a 2-fold clock to read the lower 8-bit data in the cache as the first clock. The first original data is sent to the RS error correc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More